前言

本篇中,我想跳過一些細枝末節(jié), 先簡單介紹 AMD Xilinx Vitis AI 在 Zynq 這個硬件加速平臺下軟硬件開發(fā)的基本思路和流程,把各個開發(fā)流程和工具分開,幫助剛剛接觸Vitis/Vitis AI的同學快速找到學習和開發(fā)的方向。

為什么不用其他NPU平臺?

在使用Xilinx DPU來對我們的AI應用進行加速之前,我們應該明確一個問題:為什么我們需要使用Zynq 這樣一個硬件結構,而不是使用一些專用NPU芯片 (比如NV的嵌入式開發(fā)板) 來進行加速?

我個人認為, FPGA最大的優(yōu)勢還是其對于特定應用的定制化和可重構能力(這是FPGA相對于其他類型芯片最大的不同,同時也是FPGA最具魅力的地方)。這種特性使得我們可以集中有限的硬件資源來動態(tài)的配置各種定制化應用,實現(xiàn)局部的高性能,達到四兩撥千斤的效果。

舉個例子:如果我們的在運行AI算法時,如果CPU執(zhí)行預處理速度太慢,我們就可以自己設計自己的專用硬件來執(zhí)行縮放,裁剪和卷積操作。如果我們的視頻編解碼太慢,我們也可以使用專用的IP來進行編解碼。同樣的功能,在非FPGA的平臺上使用CPU來執(zhí)行時往往速度感人

搭建一個AI加速系統(tǒng)的必要步驟

正因如此,在使用 Vitis AI 的時候,我們其實是想要定制自己的硬件結構和AI模型的。要達成這個目標,我們會有一連串的問題需要解決:

1. 首先,硬件加速系統(tǒng)的第一步當然就是加速模塊設計(verilog或者HLS),沒有加速模塊,那我們的硬件加速的系統(tǒng)就是空談。在Vitis AI中,主要是指DPU和預處理等加速模塊。這個部分的重點是數(shù)字前端設計和算法設計。

2. 完成硬件設計之后,我們會遇到第二個問題,部署硬件模塊。與任何的SoC設計類似,如果我們想要在軟件系統(tǒng)中正確的調(diào)度我們的子模塊,我們在硬件底層就需要把合理地分配線路、內(nèi)存、帶寬,正確地設計時鐘、地址、中斷等等。這個部分需要著重考慮的是SoC硬件系統(tǒng)設計。

3. 由于Vitis AI需要在linux環(huán)境下使用,因此僅僅完成硬件設計還是不夠的。我們必須要想辦法讓一個 linux系統(tǒng)運行在我們的硬件平臺上,識別到我們的加速模塊。也就是說我們需要針對我們的硬件平臺編譯一個Linux系統(tǒng)。其實核心就是提前告訴操作系統(tǒng),你需要從哪里取地址,執(zhí)行什么樣的操作。在這個階段就進入了嵌入式工程師的領域。

4. 光有系統(tǒng)還不行,我們需要為linux下的APP提供一套環(huán)境。和Standalone程序有所不同,在Linux系統(tǒng)中,我們通常不會在使用直接訪問地址的方式來操作加速器(除非加速器的操作和地址設計非常簡單)。因此開發(fā)一個中間層和驅(qū)動層也是有必要的。在Vitis AI中,在這個部分由AMD Xilinx提供,我們在實際的流程中幾乎看不到這個部分。(如果你想要開發(fā)一個私有硬件加速框架,就需要考慮這部分了)。

5. 當我們完成了上面所有的硬件,軟件,平臺和環(huán)境之后。我們其實才到最后一步:AI應用的開發(fā)。在上一步我們已經(jīng)通過驅(qū)動和接口層把軟件和硬件進行了隔離。因此,在這個階段我們本質(zhì)上就是在一塊專用NPU芯片上開發(fā)AI程序。總的來說,我們大概需要解決以下幾個問題:

訓練模型(在模型設計階段就需要考慮算子是否能夠被硬件支持的問題)

轉換模型。通常加速器是不能直接運行tf之類模型的(有些平臺可以直接運行,可能是由驅(qū)動中間層實現(xiàn)的隱式的轉換,個人水平有限此處不展開了討論),因此我們需要把AI網(wǎng)絡轉換成硬件能夠運行的執(zhí)行文件。其實就是把模型轉換成加速器硬件看得懂的一組操作。在Vitis AI 中,我們需要把tf pt等框架的模型轉換成xmodel文件。

實現(xiàn)具體的加速程序,也就是在我們的程序中正確的調(diào)用各種加速器,來加速我們的APP。

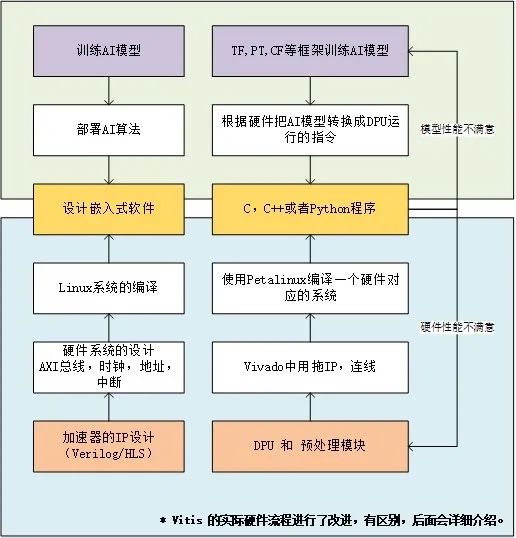

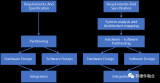

其實我們問題總結一下,我們就得到了Vitis AI下搭建一個系統(tǒng)所需要的基本思路(如圖所示)。

注意:此處框圖列出的思路和實際的步驟有一點區(qū)別,為了大家理解我做了一點簡化,此處僅僅體現(xiàn)我們從零開始搭建一個系統(tǒng)的通用思想。實際的步驟和工具的使用會在后續(xù)博客中詳細的介紹。

這里其實還是需要強調(diào)下,雖然我列出了很多步驟,但是并不是說每一步都需要我們獨立完成。在真實的項目中,整個開發(fā)流程通常需要一個團隊來完成。上圖是AMD Xilinx的官方的圖,展示了 Vitis AI流程下需要的工程師角色和開發(fā)的方向。這些角色的工作其實是相對獨立的。通常而言,我們只需要在官方工程的基礎上,根據(jù)我們的需求來重新開發(fā)我們需要的部分就好。例如,如果你僅需要修改AI模型,我們完全可以跳過硬件設計部分,直接使用AMD Xilinx幫我們設計好的平臺。如果你只需要改硬件,你也可以使用官方的程序,跳過AI訓練的步驟。

關于AMD Xilinx的軟件工具,開發(fā)環(huán)境

下面我們來聊一聊VitisAI需要的開發(fā)工具和開發(fā)環(huán)境。對于Vitis AI開發(fā)來說,我主要用到的開發(fā)工具就是 Vivado (HLS) / Petalinux / Vitis / Vitis AI。由于工具的名字比較多,這里我把對應的工具和對應的開發(fā)方向做一個簡單的介紹,方便大家快速找到自己需要的工具。

硬件

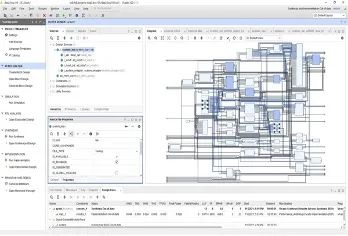

如果你是一個傳統(tǒng)FPGAer,那一定不需要我來介紹Vivado這個工具了。Vivado作為來設計數(shù)字電路和硬件系統(tǒng)的專用開發(fā)工具,基本上是人手必備了。我我唯一想要提醒的是,基于Vitis的流程來開發(fā)你的加速器時,我更推薦使用Linux開發(fā)環(huán)境,而不是Window。一個經(jīng)典的 Ubuntu 16.4.4 系統(tǒng)作為開發(fā)環(huán)境,可以節(jié)約我們很多寶貴的時間。

Vivado的BlockDesign是很Vitis流程中很常用的功能之一

嵌入式、硬件、軟件

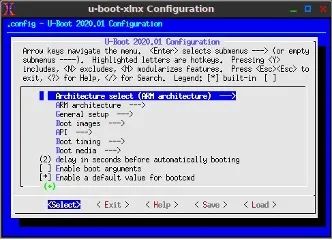

Petalinux是 ZynqMP系列官方工程原配的系統(tǒng),雖然理論上很多芯片已經(jīng)可以運行Ubuntu 和 pynq,但是想要深入官方的工程,Petalinux還是不得不品嘗的。Petalinux準確的來說其實是整套Linux的開發(fā)工具,而不僅僅是單純系統(tǒng)本身。舉個例子:在用Petalinux自動化生成設備樹,一般說的是在我們的開發(fā)環(huán)境(比如Ubuntu中)使用Petalinux工具來生成。Petalinux本身是需要安裝的,也沒有任何的GUI環(huán)境,因此對于新手有一定難度。但是想要開發(fā)一個屬于自己的動態(tài)可加載的加速應用(例如,KV260的動態(tài)加載的APP模式),Petalinux的流程是必須的。我打算日后單獨來聊一聊。

Petalinux還可以配置FPGA特定的功能和應用

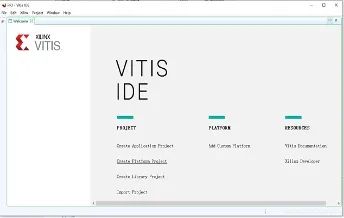

由于名字類似,Vitis 和 Vitis AI 恐怕最最令人迷惑的兩個工具了。實際上,這兩個工具是兩個完全不同的東西。Vitis 其實是一個集成開發(fā)環(huán)境,有安裝包,有GUI,它和Vivado有點類似(這個軟件改名叫Vitis SDK或許更合適)。在目前的流程中,Vitis主要用來開發(fā)嵌入式程序(C)和集成加速器(Verilog/HLS)。后面這部分似乎與Vivado類似,在Vitis中加入這部分的原因,主要是考慮到,Vivado不能很方便的進行軟件聯(lián)調(diào)。參考上面的流程圖,實際設計中我們?nèi)绻瓿?a target="_blank">嵌入式軟件后想要修改硬件,就需要返回到Vivado中重新設計,重新使用Petalinux工具編譯,最后修改軟件。這個流程經(jīng)過好幾個軟件,可以說非常痛苦的。Vitis的流程很好的解決這個問題。在Vitis中,我們可以很方便的重新連接IP端口,修改IP數(shù)量。硬件的編譯,系統(tǒng)的修改,都可以由Vitis自動完成(其實Vitis在后臺調(diào)用的還是Vivado的命令)。當然,Vitis會限制我們對于硬件平臺的修改,也不能完整編譯Petalinux,因此具體流程中我們需要三個軟件配合才能讓其流暢的工作。具體的流程,我會在后續(xù)的博客中具體的分析。

Vitis有不少老工具的既視感

AI

最后讓我們來談談Vitis AI。如果你不知道Vitis AI是什么,請記住,其實Vitis AI不是一個軟件而是一套給 AI開發(fā)者的工具腳本環(huán)境樣例的集合。像所有的github項目一樣,Vitis AI不需要安裝,下載Vitis AI只需要找到項目地址,然后根據(jù)README下載和配置即可。

假設你是一個純AI的開發(fā)者想要玩Vitis AI,其實你并不需要去管Vivado、petalinux、Vitis這種工具。因為AI幾乎是一個純軟件的部分。如果你只是先要運行一個基本的demo,你需要做的只是找到Vitis AI項目地址,clone,然后打開Vitis AI 的toturial。至于嵌入式系統(tǒng),加速器硬件,你只需要下載一個官方編譯好的系統(tǒng),燒錄進SD卡,最后打開開發(fā)板。你就會發(fā)現(xiàn),系統(tǒng),環(huán)境,加速器,都已經(jīng)準備好了。您的開發(fā)工作僅僅就參考我上圖的流程中AI的部分(嵌入式以上的部分就好)。

Vitis AI是一個Github的項目

小結

本篇主要是閑談個人對于Vitis AI的整個開發(fā)流程的理解,主要是想幫助一下新手快速找到一個開發(fā)目標,不至于迷失在大量的工具的方向中。后續(xù)的博客中,我會繼續(xù)嘗試介紹一些開發(fā)流程中的細節(jié)。

審核編輯:湯梓紅

-

Xilinx

+關注

關注

73文章

2182瀏覽量

124392 -

AI

+關注

關注

87文章

34324瀏覽量

275493 -

DPU

+關注

關注

0文章

390瀏覽量

24712 -

UltraScale

+關注

關注

0文章

120瀏覽量

31798 -

Vitis

+關注

關注

0文章

147瀏覽量

7837

原文標題:閑談 Vitis AI | DPU 在 UltraScale 平臺下的軟硬件流程 (1)

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發(fā)者社區(qū)】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

【米爾FZ3深度學習計算卡試用體驗】搭建Vitis Ai系統(tǒng)平臺并測試

【米爾FZ3深度學習計算卡試用體驗】DPU搭建

【米爾百度大腦EdgeBoard邊緣AI計算盒試用連載】IV. FZ5-DPU@2020.2(ZMJ)

Vitis AI Model Zone軟件平臺具備哪些功能?

在ultrascale+上利用VCU和DPU實現(xiàn)的智能零售系統(tǒng)

阿里平頭哥發(fā)布首個 RISC-V AI 軟硬全棧平臺

【KV260視覺入門套件試用體驗】Vitis AI 初次體驗

【KV260視覺入門套件試用體驗】部署DPU鏡像并運行Vitis AI圖像分類示例程序

【KV260視覺入門套件試用體驗】Vitis-AI加速的YOLOX視頻目標檢測示例體驗和原理解析

【KV260視覺入門套件試用體驗】Vitis AI 構建開發(fā)環(huán)境,并使用inspector檢查模型

單片機測控系統(tǒng)的軟硬件平臺技術

在賽靈思FPGA SoC平臺上使用VITIS AI加速人工智能應用

軟硬件融合的概念和內(nèi)涵

閑談Vitis AI|DPU在UltraScale平臺下的軟硬件流程(1)

閑談Vitis AI|DPU在UltraScale平臺下的軟硬件流程(1)

評論