將現(xiàn)場(chǎng)可編程門陣列 (FPGA) 連接到模數(shù)轉(zhuǎn)換器 (ADC) 輸出是一項(xiàng)常見的工程挑戰(zhàn)。本文概述了各種接口協(xié)議和標(biāo)準(zhǔn),以及在高速數(shù)據(jù)轉(zhuǎn)換器實(shí)現(xiàn)中使用低壓差分信號(hào)(LVDS)的應(yīng)用技巧和技術(shù)。

界面樣式和標(biāo)準(zhǔn)

將FPGA連接到ADC數(shù)字?jǐn)?shù)據(jù)輸出是一個(gè)常見的工程挑戰(zhàn)。由于ADC使用各種數(shù)字?jǐn)?shù)據(jù)樣式和標(biāo)準(zhǔn),因此任務(wù)變得復(fù)雜。單數(shù)據(jù)速率(SDR)CMOS對(duì)于低速數(shù)據(jù)接口非常常見,通常低于200 MHz。在這種情況下,數(shù)據(jù)由發(fā)射器在時(shí)鐘的一個(gè)邊沿轉(zhuǎn)換,并由另一個(gè)時(shí)鐘邊沿的接收器接收。這可確保數(shù)據(jù)在被接收器采樣之前有足夠的時(shí)間建立。在雙倍數(shù)據(jù)速率(DDR)CMOS中,發(fā)射器在每個(gè)時(shí)鐘邊沿轉(zhuǎn)換數(shù)據(jù)。這允許在相同的時(shí)間內(nèi)傳輸兩倍于SDR的數(shù)據(jù);但是,接收器正確采樣的時(shí)間更為復(fù)雜。

并行LVDS是高速數(shù)據(jù)轉(zhuǎn)換器的通用標(biāo)準(zhǔn)。它使用差分信號(hào),每個(gè)比特使用一個(gè) P 線和一個(gè) N 線,在最新的 FPGA 中實(shí)現(xiàn)高達(dá) 1.6 Gbps 的 DDR 或 800 MHz 的速度。并行LVDS的功耗低于CMOS,但需要兩倍的導(dǎo)線數(shù)量,這使得布線變得困難。雖然不是LVDS標(biāo)準(zhǔn)的一部分,但LVDS通常用于具有源同步時(shí)鐘系統(tǒng)的數(shù)據(jù)轉(zhuǎn)換器。在此設(shè)置中,與數(shù)據(jù)同相的時(shí)鐘與數(shù)據(jù)一起傳輸。然后,接收器可以使用此時(shí)鐘更輕松地捕獲數(shù)據(jù),因?yàn)樗F(xiàn)在知道數(shù)據(jù)轉(zhuǎn)換。

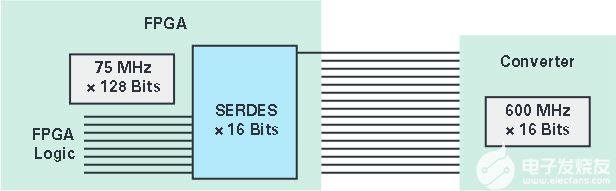

FPGA邏輯通常不夠快,無法跟上高速轉(zhuǎn)換器的總線速度,因此大多數(shù)FPGA都有串行器/解串器(SERDES)模塊,用于將轉(zhuǎn)換器側(cè)的快速窄串行接口轉(zhuǎn)換為FPGA側(cè)的寬窄并行接口。對(duì)于總線中的每個(gè)數(shù)據(jù)位,該模塊輸出2、4或8位,但速率為時(shí)鐘速率的二分之一、四分之一或八分之一,從而有效地反序列化數(shù)據(jù)。數(shù)據(jù)由FPGA內(nèi)部的寬總線處理,其運(yùn)行速度比進(jìn)入轉(zhuǎn)換器的窄總線慢得多。

LVDS信令標(biāo)準(zhǔn)也用于串行鏈路,主要用于高速ADC。串行LVDS通常用于引腳數(shù)比接口速度更重要的情況。通常使用兩個(gè)時(shí)鐘,即數(shù)據(jù)速率時(shí)鐘和幀時(shí)鐘。并行LVDS部分提到的所有注意事項(xiàng)也適用于串行LVDS。并行LVDS僅由多條串行LVDS線路組成。

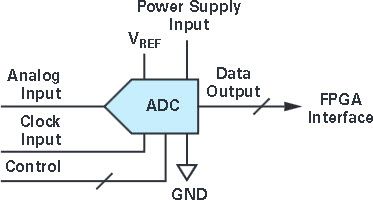

圖1.將ADC連接到FPGA有不同的接口可能性。

我2C 使用兩條線:時(shí)鐘和數(shù)據(jù)。它支持總線上的大量器件,無需額外的引腳。我2C 是一種相對(duì)較慢的協(xié)議,工作在 400 kHz 至 1 MHz 范圍內(nèi)。它通常用于零件尺寸是一個(gè)問題的慢速設(shè)備。我2C也經(jīng)常用作控制接口或數(shù)據(jù)接口。

SPI 使用三根或四根線:

時(shí)鐘

數(shù)據(jù)輸入和數(shù)據(jù)輸出(4線)或雙向數(shù)據(jù)輸入/數(shù)據(jù)輸出(3線)

芯片選擇(每個(gè)非主設(shè)備一個(gè))

SPI支持的器件數(shù)量與可用片選線的數(shù)量一樣多。它提供高達(dá)約100 MHz的速度,通常用作控制接口和數(shù)據(jù)接口。

串行端口(SPORT)是一種基于CMOS的雙向接口,每個(gè)方向使用一個(gè)或兩個(gè)數(shù)據(jù)引腳。其可調(diào)字長(zhǎng)為非 8% 分辨率提供了更好的效率。SPORT 提供時(shí)域多路復(fù)用 (TDM) 支持,通常用于音頻/媒體轉(zhuǎn)換器和高通道數(shù)轉(zhuǎn)換器。它提供每個(gè)引腳約 100 MHz 的性能。SPORT在Blackfin處理器上受支持,并在FPGA上提供直接的實(shí)現(xiàn)。SPORT 通常僅用于數(shù)據(jù),但可以插入控制字符。?

JESD204是JEDEC標(biāo)準(zhǔn),用于單個(gè)主機(jī)(如FPGA或ASIC)與一個(gè)或多個(gè)數(shù)據(jù)轉(zhuǎn)換器之間的高速串行鏈路。最新規(guī)范為每個(gè)通道或差分對(duì)提供高達(dá) 3.125 Gbps 的速率。未來的修訂版可能會(huì)指定 6.25 Gbps 及以上。通道采用8B/10B編碼,將通道的有效帶寬降低到理論值的80%。時(shí)鐘嵌入在數(shù)據(jù)流中,因此沒有額外的時(shí)鐘信號(hào)。多個(gè)通道可以綁定在一起以提高吞吐量,同時(shí)數(shù)據(jù)鏈路層協(xié)議可確保數(shù)據(jù)完整性。與簡(jiǎn)單的LVDS或CMOS相比,JESD204在FPGA/ASIC中需要更多的數(shù)據(jù)成幀資源。它以更昂貴的FPGA和更復(fù)雜的PCB布線為代價(jià),大大降低了布線要求。

圖2.SERDES模塊位于FPGA接口中,轉(zhuǎn)換器上具有高速串行接口。

一般性建議

一些一般性建議有助于ADC和FPGA之間的接口。

在接收器(FPGA 或 ASIC)上使用外部電阻端接,而不是內(nèi)部 FPGA 端接,以避免由于不匹配而導(dǎo)致的反射,從而破壞時(shí)序預(yù)算。

如果在系統(tǒng)中使用多個(gè)ADC,請(qǐng)勿使用來自一個(gè)ADC的一個(gè)數(shù)控振蕩器(DCO)。

在向接收器布置數(shù)字走線時(shí),不要使用大量的長(zhǎng)號(hào),以保持所有走線的長(zhǎng)度相等。

在CMOS輸出上使用串聯(lián)端接來降低邊沿速率并限制開關(guān)噪聲。驗(yàn)證是否使用了正確的數(shù)據(jù)格式(二進(jìn)制補(bǔ)碼、偏移二進(jìn)制)。

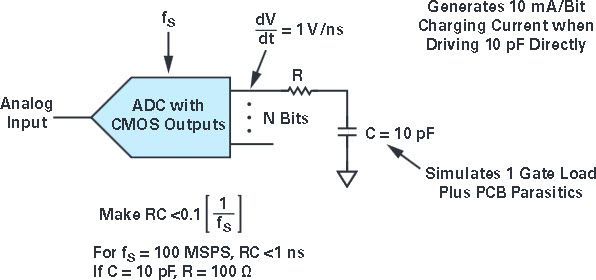

對(duì)于單端CMOS數(shù)字信號(hào),邏輯電平以約1 V/ns的速度移動(dòng),典型輸出負(fù)載最大值為10 pF,典型充電電流為10 mA/位。應(yīng)通過使用盡可能小的容性負(fù)載來最小化充電電流。這通常可以通過僅驅(qū)動(dòng)一個(gè)具有最短走線的柵極來實(shí)現(xiàn),最好沒有任何過孔。通過在數(shù)字輸出和輸入中使用阻尼電阻器,也可以將充電電流降至最低。

阻尼電阻和容性負(fù)載的時(shí)間常數(shù)應(yīng)約為采樣速率周期的10%。如果時(shí)鐘速率為100 MHz,負(fù)載為10 pF,則時(shí)間常數(shù)應(yīng)為10 ns的10%或1 ns。在這種情況下,R 應(yīng)為 100 Ω。為了獲得最佳信噪比(SNR)性能,1.8 V DRVDD優(yōu)于3.3 V DRVDD。然而,當(dāng)驅(qū)動(dòng)大容性負(fù)載時(shí),SNR會(huì)降低。CMOS輸出可在高達(dá)約200 MHz采樣時(shí)鐘下使用。如果驅(qū)動(dòng)兩個(gè)輸出負(fù)載或走線長(zhǎng)度超過 1 或 2 英寸,建議使用緩沖器。

應(yīng)小心處理ADC數(shù)字輸出,因?yàn)樗矐B(tài)電流會(huì)耦合回模擬輸入,從而增加ADC的噪聲和失真。

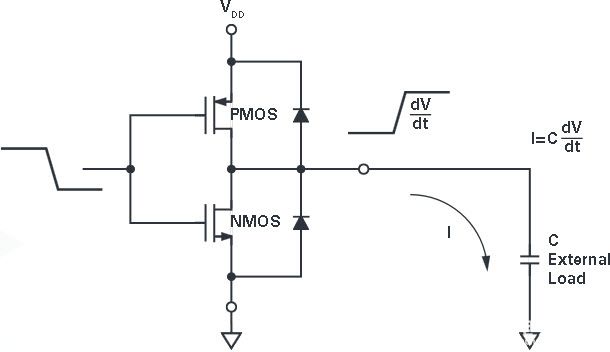

圖3所示的典型CMOS驅(qū)動(dòng)器能夠產(chǎn)生較大的瞬態(tài)電流,尤其是在驅(qū)動(dòng)容性負(fù)載時(shí)。必須特別注意CMOS數(shù)據(jù)輸出ADC,以使這些電流最小化,并且不會(huì)在ADC中產(chǎn)生額外的噪聲和失真。

圖3.典型的CMOS數(shù)字輸出驅(qū)動(dòng)器。

典型示例

圖4所示為16位并行CMOS輸出ADC的情況。每個(gè)輸出端的負(fù)載為10 pF,模擬一個(gè)柵極負(fù)載和PCB寄生效應(yīng),每個(gè)驅(qū)動(dòng)器在驅(qū)動(dòng)10 pF負(fù)載時(shí)產(chǎn)生10 mA的充電電流。

圖4.使用串聯(lián)電阻來最小化CMOS數(shù)字輸出的充電電流。

因此,16位ADC的總瞬態(tài)電流可高達(dá)16 ×10 mA = 160 mA。這些瞬態(tài)電流可以通過在每個(gè)數(shù)據(jù)輸出中串聯(lián)一個(gè)小電阻R來抑制。應(yīng)選擇電阻值,使RC時(shí)間常數(shù)小于總采樣周期的10%。對(duì)于 fS= 100 MSPS,RC 應(yīng)小于 1 ns。C = 10 pF時(shí),R約為100 Ω是最佳的。選擇較大的 R 值會(huì)降低輸出數(shù)據(jù)建立時(shí)間并干擾正確的數(shù)據(jù)捕獲。CMOS ADC輸出端的容性負(fù)載應(yīng)限制為單個(gè)柵極負(fù)載,通常是外部數(shù)據(jù)采集寄存器。在任何情況下,數(shù)據(jù)輸出都不應(yīng)直接連接到嘈雜的數(shù)據(jù)總線。必須使用中間緩沖寄存器,以盡量減少ADC輸出的直接負(fù)載。

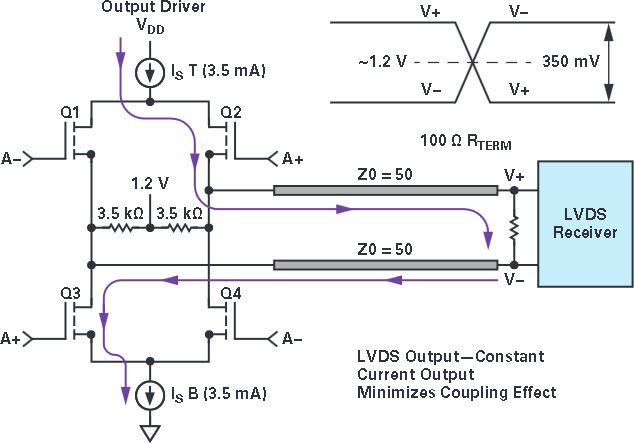

圖5顯示了采用CMOS封裝的標(biāo)準(zhǔn)LVDS驅(qū)動(dòng)器。標(biāo)稱電流為3.5 mA,共模電壓為1.2 V。因此,當(dāng)驅(qū)動(dòng)100 Ω差分終端電阻時(shí),接收器每個(gè)輸入端的擺幅為350 mV p-p。這相當(dāng)于700 mV p-p的差分?jǐn)[幅。這些數(shù)字來自LVDS規(guī)范。

圖5.典型的LVDS驅(qū)動(dòng)器設(shè)計(jì)。

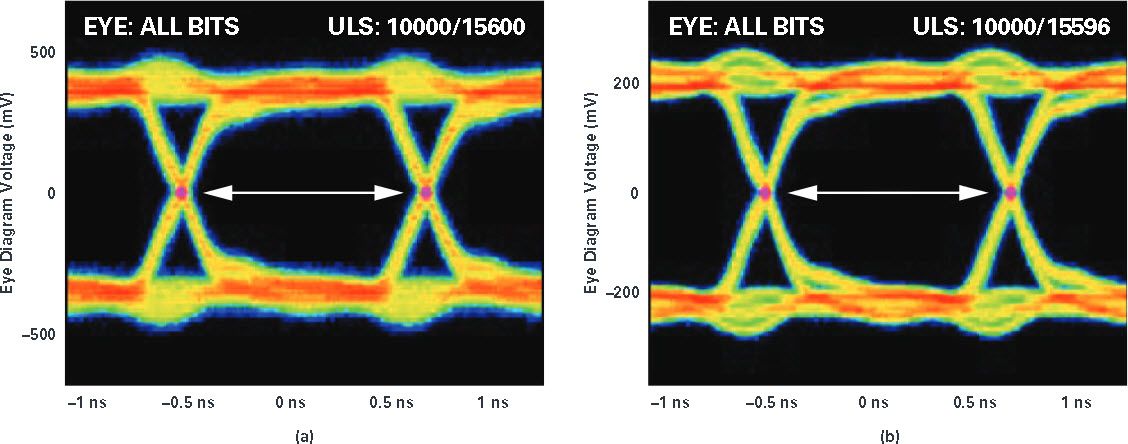

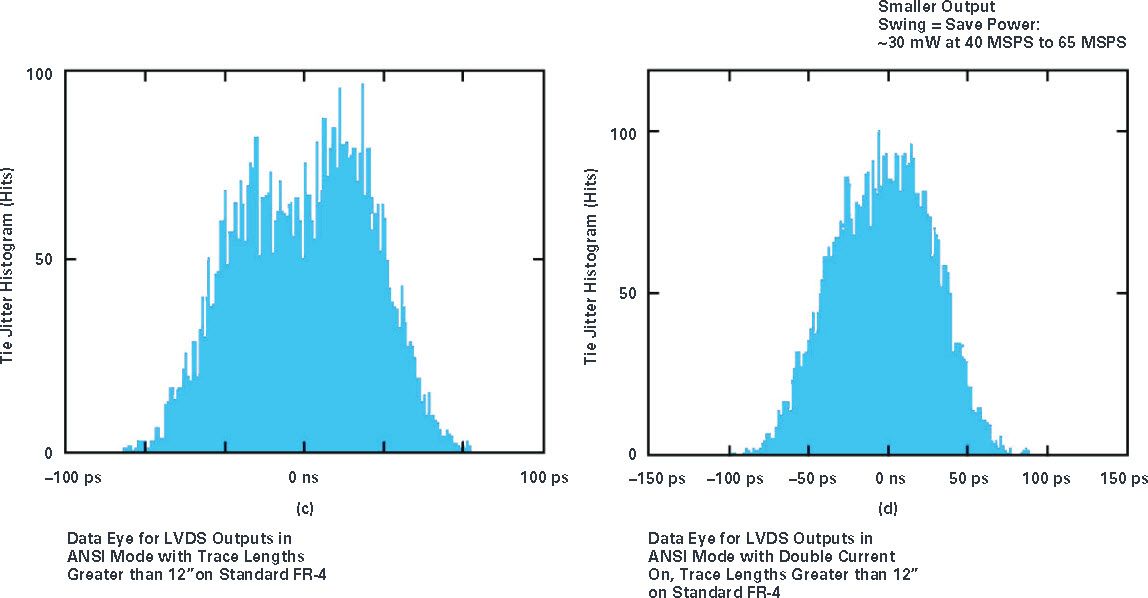

有兩種LVDS標(biāo)準(zhǔn):一種由ANSI定義,另一種由IEEE定義。雖然這兩個(gè)標(biāo)準(zhǔn)相似并且通常相互兼容,但它們并不相同。圖6比較了兩種標(biāo)準(zhǔn)的眼圖和抖動(dòng)直方圖。與ANSI標(biāo)準(zhǔn)320 mV p-p相比,IEEE標(biāo)準(zhǔn)LVDS的擺幅降低了200 mV p-p。這有助于節(jié)省數(shù)字輸出的功率。因此,如果 IEEE 標(biāo)準(zhǔn)能夠適應(yīng)需要與接收器建立的應(yīng)用和連接,請(qǐng)使用 IEEE 標(biāo)準(zhǔn)。

圖6.ANSI 與 IEEE LVDS 標(biāo)準(zhǔn)。

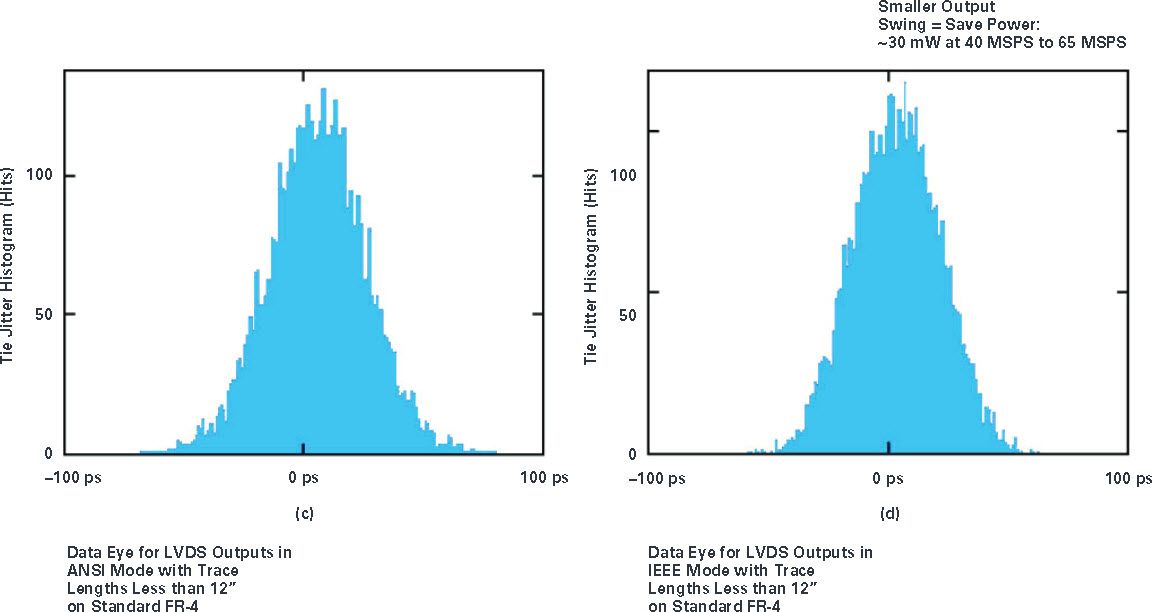

圖7比較了長(zhǎng)走線長(zhǎng)度超過12英寸或30 cm的ANSI和IEEE LVDS標(biāo)準(zhǔn)。這兩個(gè)圖形均按 ANSI 版本標(biāo)準(zhǔn)驅(qū)動(dòng)。在右圖中,輸出電流加倍。將輸出電流加倍可清除眼圖并改善抖動(dòng)直方圖。

圖7.ANSI 與 IEEE LVDS 標(biāo)準(zhǔn),跡線超過 12 英寸。

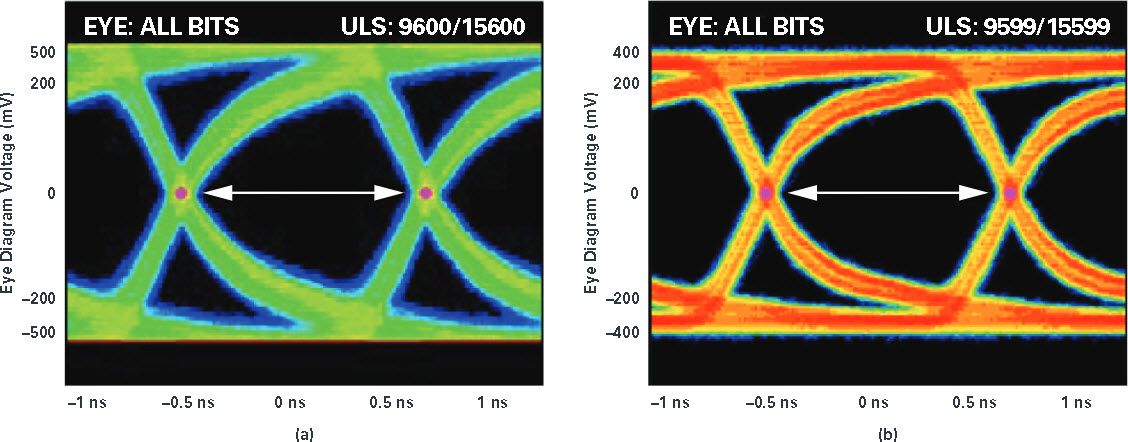

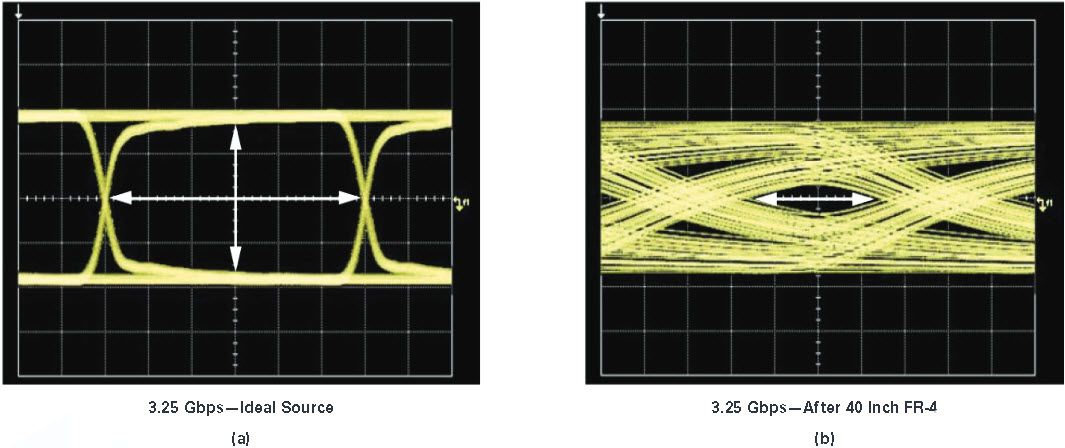

請(qǐng)注意圖 8 中長(zhǎng)跡線對(duì) FR4 材料的影響。左圖顯示了理想的眼圖,右圖位于發(fā)射器處。在40英寸外的接收器上,眼睛幾乎閉合,接收器難以恢復(fù)數(shù)據(jù)。

圖8.FR-4通道損耗的影響。

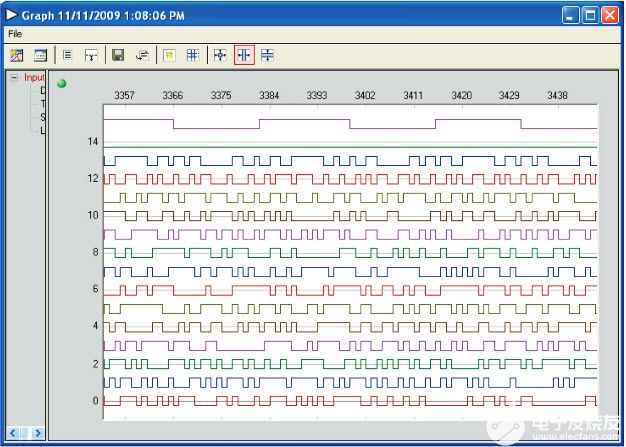

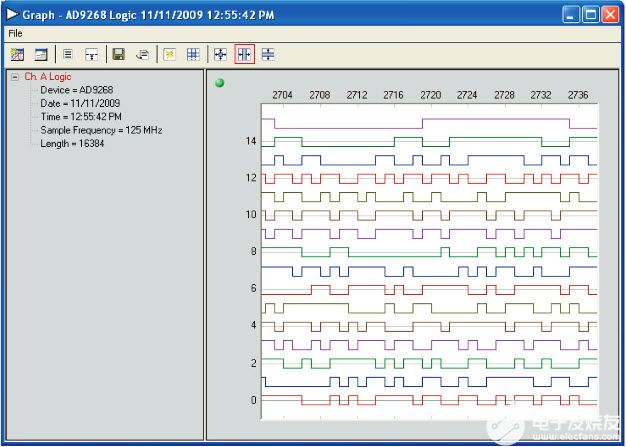

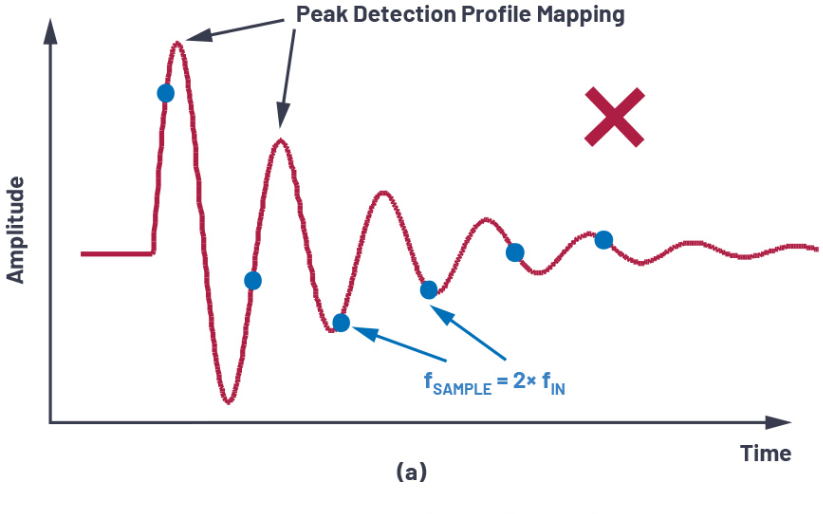

在圖9中,數(shù)據(jù)位的可視模擬數(shù)字顯示顯示第14位永遠(yuǎn)不會(huì)切換。這可能表明器件、PCB或接收器存在問題,或者無符號(hào)數(shù)據(jù)不夠大,無法切換最高有效位。?

圖9.AD9268缺少位 14 的 ADC。

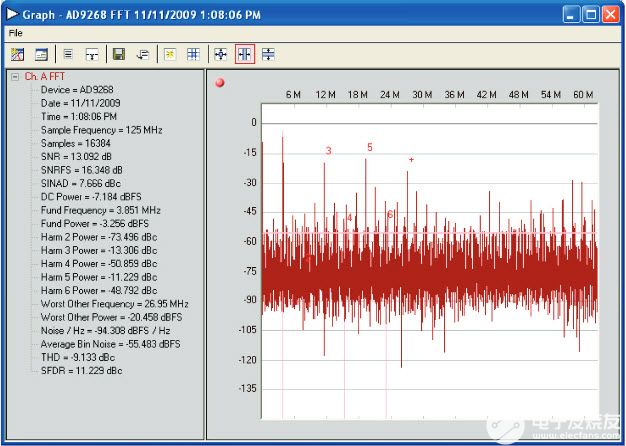

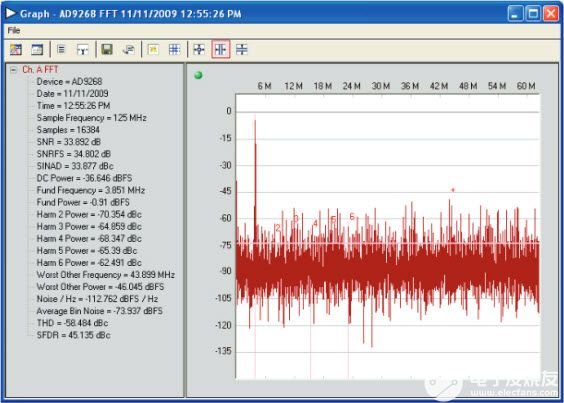

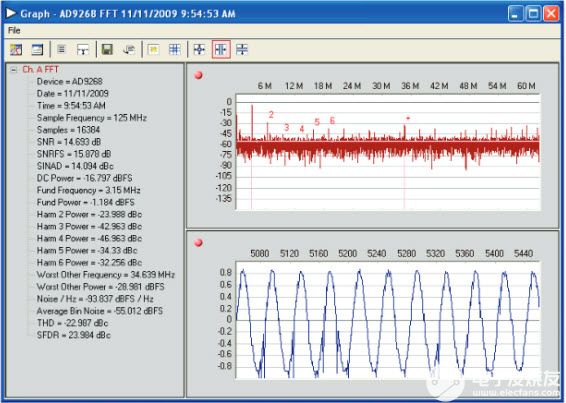

圖10顯示了前一個(gè)數(shù)字?jǐn)?shù)據(jù)的頻域視圖,其中第14位未切換。該圖顯示該位很重要,并且系統(tǒng)中某處存在錯(cuò)誤。

圖 10.缺少位14的AD9268 ADC頻域圖

圖11是相同數(shù)據(jù)的時(shí)域圖。數(shù)據(jù)不是平滑的正弦波,而是偏移的,并且在整個(gè)波形的各個(gè)點(diǎn)都有明顯的峰值。

圖 11.缺少位14的AD9268 ADC時(shí)域圖

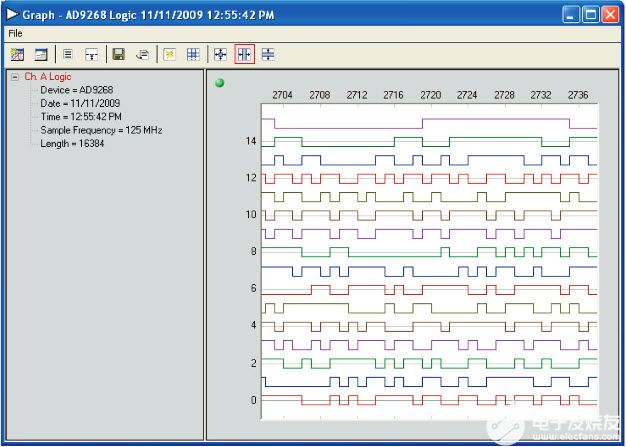

在圖12中,兩個(gè)位短接在一起,而不是遺漏一點(diǎn),以便接收器始終在兩個(gè)引腳上看到相同的數(shù)據(jù)。

圖 12.AD9268 具有第9位和第10位短路的ADC。

圖13顯示了兩個(gè)位短接在一起的相同情況的頻域視圖。雖然基本音清晰存在,但本底噪聲明顯低于應(yīng)有的水平。地板的扭曲程度取決于哪些位短路。

圖 13.AD9268 ADC頻域圖,第9位和第10位短接在一起。

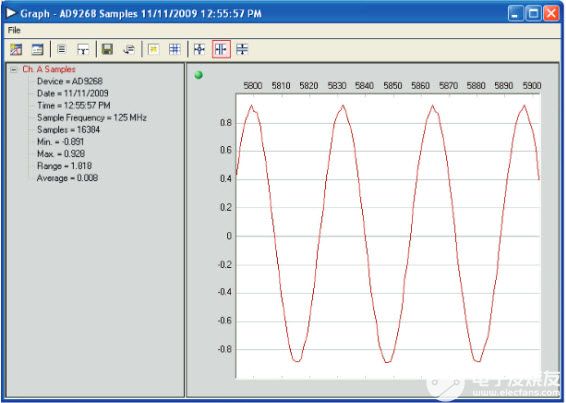

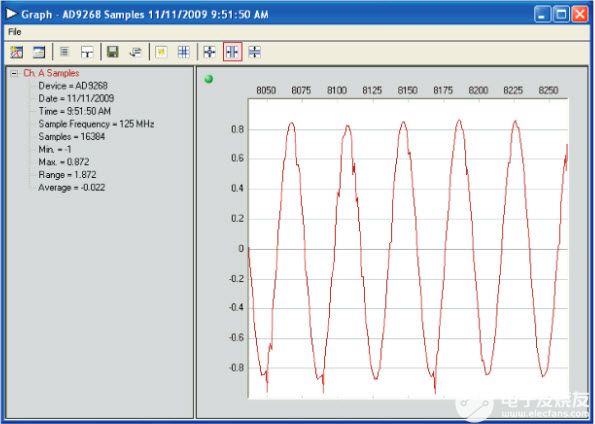

在圖 14 所示的時(shí)域視圖中,這個(gè)問題不太明顯。雖然在波的波峰和波谷中會(huì)損失一些平滑度,但當(dāng)采樣率接近波形的頻率時(shí),這種情況也很常見。

圖 14.AD9268 ADC時(shí)域圖,第9位和第10位短接在一起。

圖15顯示了一個(gè)時(shí)序無效的轉(zhuǎn)換器,在本例中是由建立/保持問題引起的。與以前的錯(cuò)誤不同,以前的錯(cuò)誤通常在數(shù)據(jù)的每個(gè)周期中表現(xiàn)出來,時(shí)序錯(cuò)誤通常不太一致。不太嚴(yán)重的時(shí)序錯(cuò)誤可能是間歇性的。這些圖顯示了不符合時(shí)序要求的數(shù)據(jù)采集的時(shí)域和頻域。請(qǐng)注意,時(shí)域中的誤差在周期之間不一致。另外,請(qǐng)注意FFT/頻域中本底噪聲升高。這通常表示缺少位,這可能是由不正確的時(shí)間對(duì)齊引起的。

圖 15.AD9268具有無效數(shù)據(jù)和時(shí)鐘時(shí)序的時(shí)域圖

圖16是圖15所示時(shí)域時(shí)序誤差的近距離視圖。同樣,請(qǐng)注意,每個(gè)周期的錯(cuò)誤不一致,但某些錯(cuò)誤確實(shí)會(huì)重復(fù)。一個(gè)例子是此圖中幾個(gè)周期的谷上的負(fù)峰值。

圖 16.AD9268放大時(shí)域圖,數(shù)據(jù)和時(shí)鐘時(shí)序無效。

結(jié)論

本文討論了標(biāo)準(zhǔn)接口 — SPI、I2C、SPORT、LVDS 和 JESD204A——用于將 FPGA 連接到 ADC。隨著數(shù)據(jù)速率的進(jìn)一步提高,F(xiàn)PGA與ADC的接口仍將是一個(gè)共同的挑戰(zhàn)。JESD204B支持12.5 Gbps,JESD204C將遷移到32 Gbps。

審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1646文章

22069瀏覽量

619674 -

pcb

+關(guān)注

關(guān)注

4371文章

23526瀏覽量

410735 -

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

9114瀏覽量

152213

發(fā)布評(píng)論請(qǐng)先 登錄

CTSD精密ADC—利用異步采樣速率轉(zhuǎn)換(ASRC)簡(jiǎn)化數(shù)字?jǐn)?shù)據(jù)接口

FPGA與ADC數(shù)字輸出的各種接口協(xié)議和標(biāo)準(zhǔn)

LabVIEW如何顯示數(shù)字?jǐn)?shù)據(jù)?

數(shù)字?jǐn)?shù)據(jù)控件問題

28335AD數(shù)據(jù)采集當(dāng)ADC0為0V時(shí)DSP輸出數(shù)字?jǐn)?shù)據(jù)并不是0

數(shù)字?jǐn)?shù)據(jù)輸出的電氣規(guī)格和特點(diǎn)

數(shù)字?jǐn)?shù)據(jù)網(wǎng)

FPGA與ADC數(shù)字?jǐn)?shù)據(jù)輸出的接口

模數(shù)轉(zhuǎn)換器(ADC)選擇重要參數(shù):數(shù)字?jǐn)?shù)據(jù)輸出類型

FPGA與ADC數(shù)字?jǐn)?shù)據(jù)輸出接口的協(xié)議及標(biāo)準(zhǔn)

MT-201:FPGA與ADC數(shù)字?jǐn)?shù)據(jù)輸出的接口

FPGA與ADC數(shù)字?jǐn)?shù)據(jù)輸出的接口資料下載

具有LVDS輸出的LTM9011 ADC的AN147-Altera Stratix IV FPGA接口

CTSD精密ADC:利用異步采樣速率轉(zhuǎn)換(ASRC)簡(jiǎn)化數(shù)字?jǐn)?shù)據(jù)接口

FPGA與ADC數(shù)字?jǐn)?shù)據(jù)輸出的接口指南

FPGA與ADC數(shù)字?jǐn)?shù)據(jù)輸出的接口

FPGA與ADC數(shù)字?jǐn)?shù)據(jù)輸出的接口

評(píng)論