作為IC設計人員,熟練掌握數字前端語法檢查工具Spyglass的重要性不言而喻,本文手把手教你學習Spyglass工具。

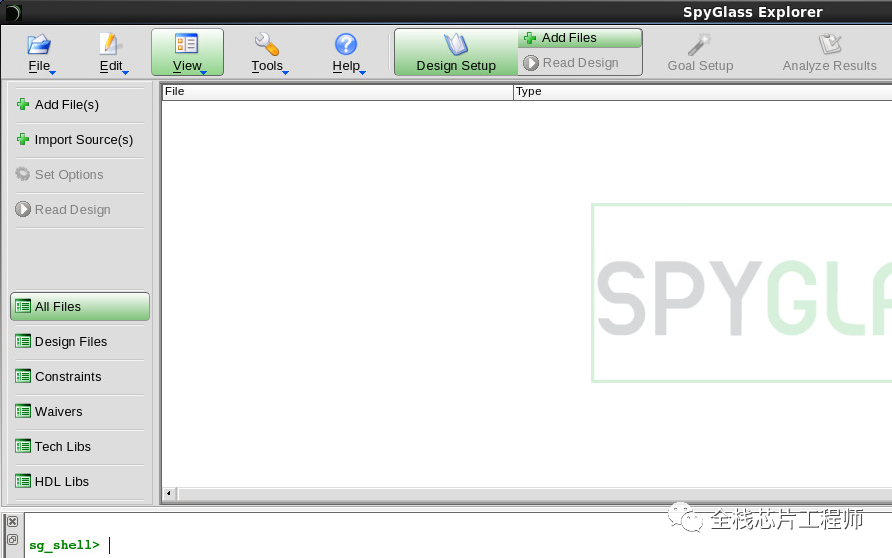

啟動Spyglass軟件:spyglass &

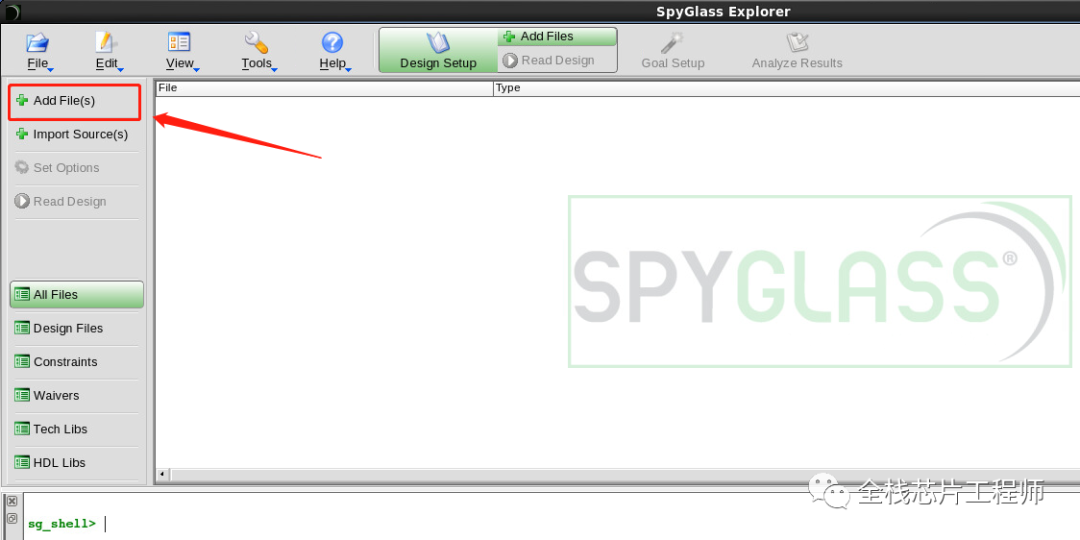

點擊左邊Add File(s):

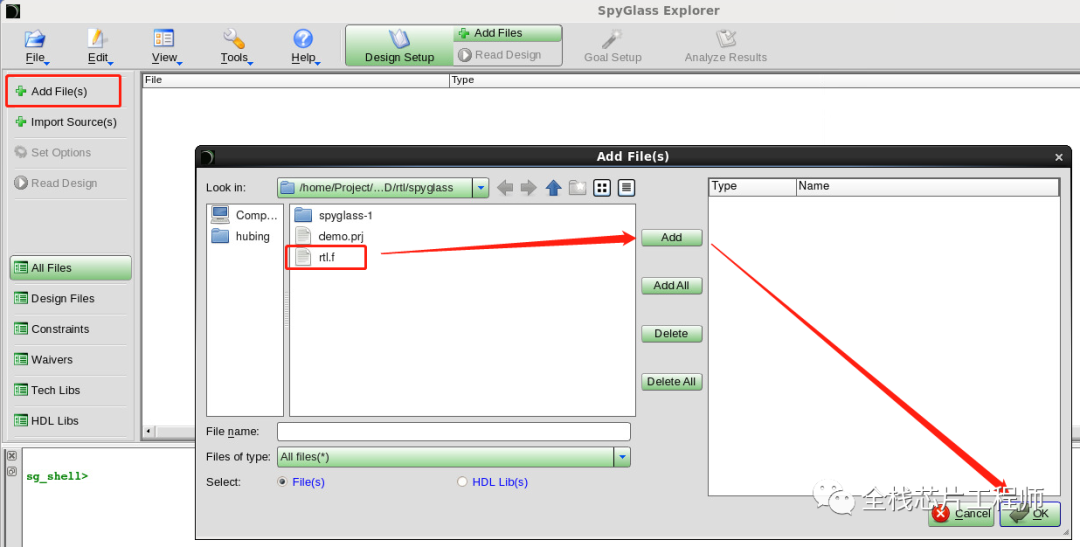

將.v文件通過rtl.f統一添加,如下圖,點擊OK:

或者通過命令添加:

sg_shell> read_file -type sourcelist rtl.f

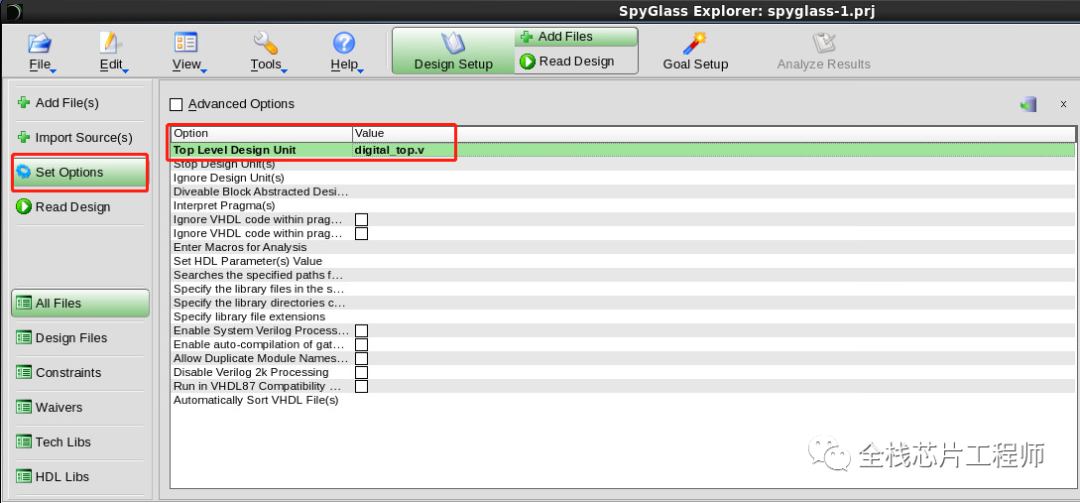

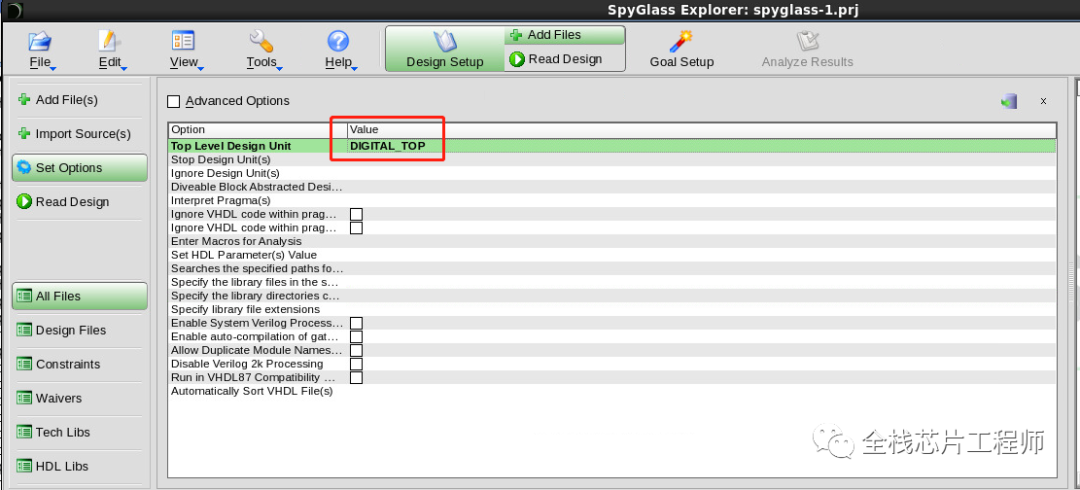

設置頂層,選中下圖左邊Set Options,手動設置Value為digital_top.v,這里我們留一個bug,后面看得到。

或者通過命令添加:

sg_shell> set_option top digital_top.v

我們也可以默認缺省頂層文件,此處,我們暫時不用remove_option top命令,注意剛才我們留了一個bug。

sg_shell> remove_option top

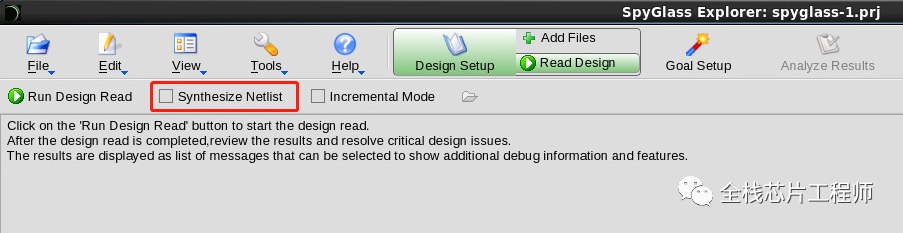

點擊Read Design,

選擇SynthesizeNetlist,在讀入設計的同時進行綜合

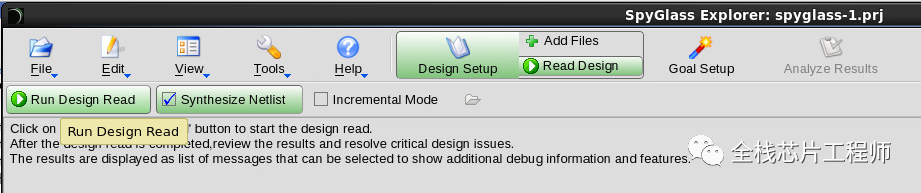

點擊Run Design Read:

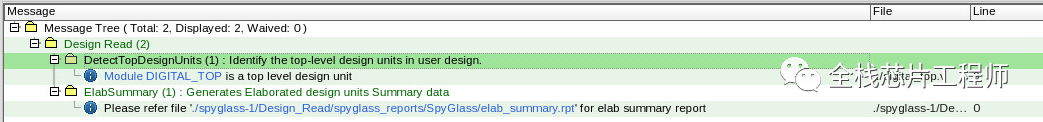

讀取完成發現:

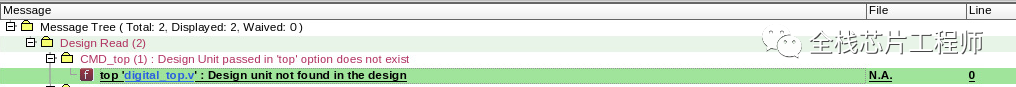

top 'digital_top.v' : Design unit not found in the design

bug來了,什么問題呢?找不到Design unit, 聰明的你一定發現了,頂層是module名,不是module文件名。如下圖所示:

也就是說設置Top level Design Unit的value為DIGITAL_TOP, 而不是digital_top.v。

再次Run Read Design,如下圖,讀取成功。

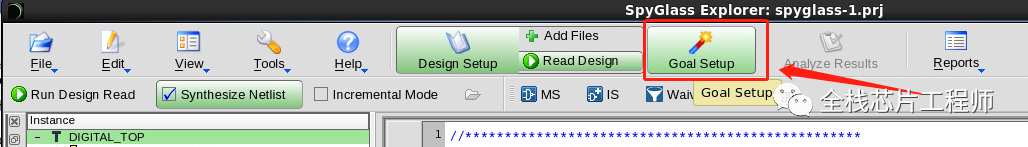

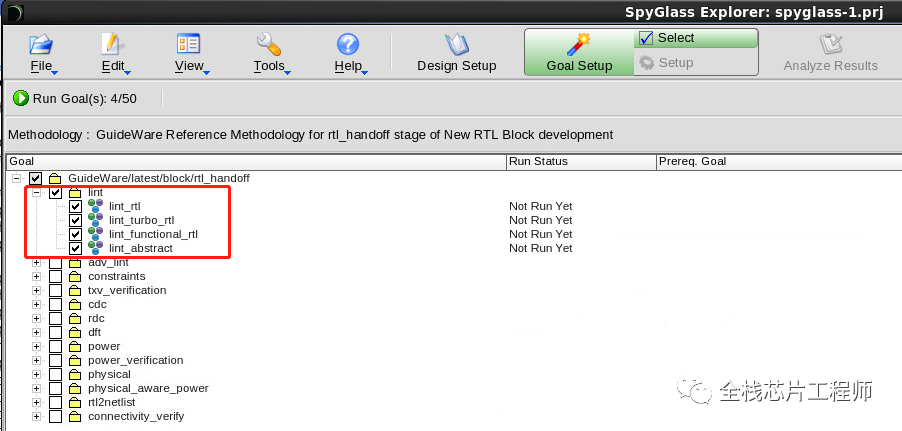

接著,設置Goal Setup:

首先選中lint,我們先看lint, 點擊Run Goal:

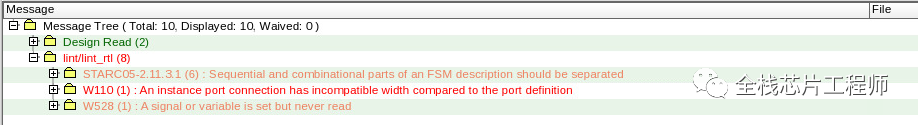

運行得到結果如下,我們開始逐一解析錯誤的原因,并給出RTL修改辦法,具體參見小編知識星球。

審核編輯:湯梓紅

-

IC設計

+關注

關注

38文章

1341瀏覽量

104938 -

軟件

+關注

關注

69文章

5080瀏覽量

88703 -

檢查工具

+關注

關注

0文章

6瀏覽量

6561 -

數字前端

+關注

關注

0文章

12瀏覽量

7841

原文標題:詳解Spyglass使用(一)

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

分享一些語法檢查的工具

詳解Spyglass使用(二)

手把手教你學習Spyglass工具

一步左移到位:動靜結合,VC SpyGlass如何加速復雜CDC驗證

下周五|一步左移到位:動靜結合,VC SpyGlass如何加速復雜CDC驗證

本周五|一步左移到位:動靜結合,VC SpyGlass如何加速復雜CDC驗證

明天|一步左移到位:動靜結合,VC SpyGlass如何加速復雜CDC驗證

詳解Spyglass使用(一)

詳解Spyglass使用(一)

評論