做動態(tài)仿真驗(yàn)證通常會遇到要等待仿真結(jié)果的情況,特別是在調(diào)試某個測試用例的時候。很多時候,工程師們會自然地認(rèn)為仿真速度大部分依賴于跑仿真任務(wù)的服務(wù)器本身的性能,以及EDA仿真工具的能力。而實(shí)際上,高效的驗(yàn)證環(huán)境以及代碼質(zhì)量也是影響仿真速度的關(guān)鍵因素。

另一方面,提高仿真速度這回事,對于芯片工程師來說本身就是“求人不如求己”。提高服務(wù)器機(jī)器性能意味著更大的資金投入,更高性能的仿真工具也不是一時半會能達(dá)成的。而探索更高效的驗(yàn)證方法學(xué),構(gòu)建更高執(zhí)行效率的代碼是當(dāng)下就能做的事情。

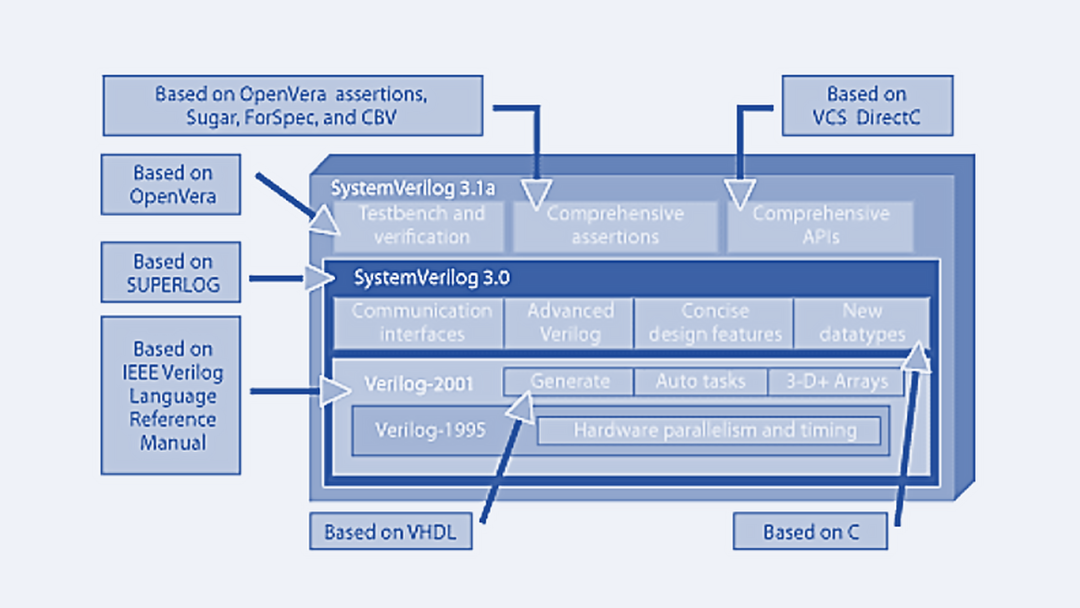

本文的主要內(nèi)容參考來自于Cliff Cummings在2019年DVCon會議上發(fā)表的文章:Yikes! Why is My SystemVerilog Still So Slooooow. 這篇文章主要探討了SystemVerilog仿真速度跟Coding風(fēng)格之間的關(guān)系,文章中有詳細(xì)的實(shí)驗(yàn)?zāi)繕?biāo)、方法和數(shù)據(jù)結(jié)果呈現(xiàn)。本文將摘錄和分析那些對仿真速度影響較大的編碼風(fēng)格。

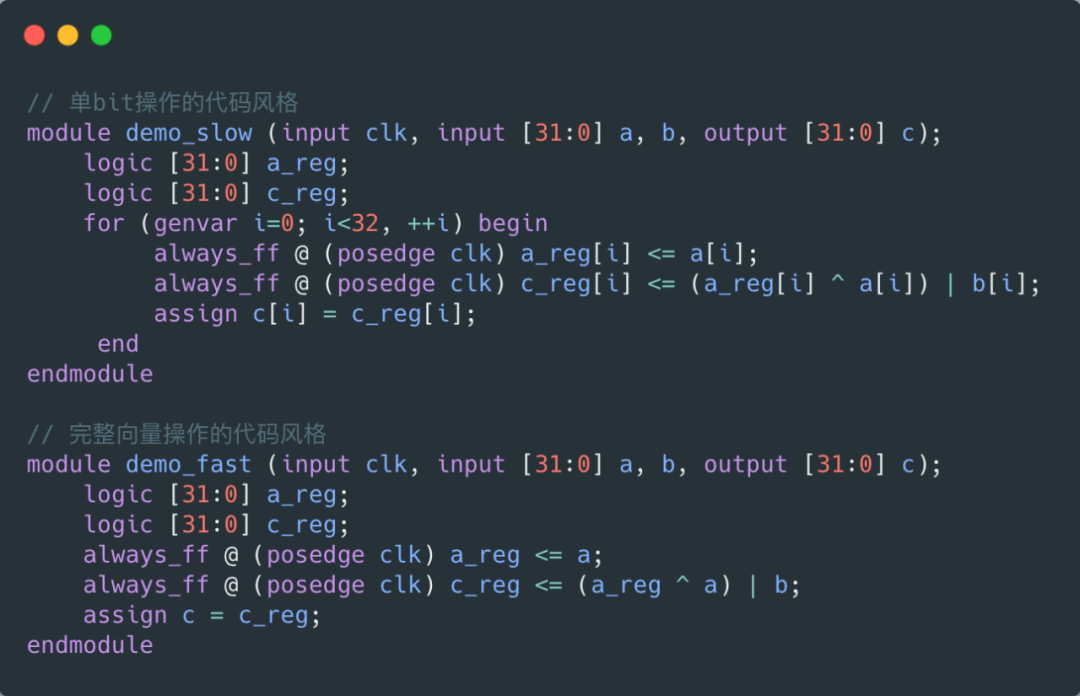

使用向量操作代替單bit操作

仿真器在做完整向量計(jì)算的速度比單bit計(jì)算要高。根據(jù)參考文獻(xiàn)的數(shù)據(jù),在某款仿真工具下,最高提速可以達(dá)到3倍以上。

下面是一個例程,分別呈現(xiàn)不同的代碼實(shí)現(xiàn)風(fēng)格。

避免在循環(huán)中實(shí)例化對象

這個技巧關(guān)系到內(nèi)存的分配和回收。低效的內(nèi)存管理會導(dǎo)致嚴(yán)重的cache miss、堆棧管理開銷和垃圾回收開銷,盡管這些都是操作系統(tǒng)幫我們做的。

當(dāng)我們需要一種新的數(shù)據(jù)結(jié)構(gòu)時,可以使用結(jié)構(gòu)體struct就不用class,類的例化和垃圾回收都是開銷。創(chuàng)建一個對象的時候,不要上來就是一個new,可以考慮是否可以重用之前創(chuàng)建過的對象。

如下例程,應(yīng)用這個技巧在三款主流仿真工具上都能帶來仿真速度收益,最高有超過一半的速度提升。

條件判斷字符串處理

在仿真過程中不斷地打印信息或者讀寫文件會導(dǎo)致仿真速度非常慢,畢竟調(diào)用計(jì)算機(jī)IO效率并不高。在UVM中有健全的report管理機(jī)制,可以根據(jù)設(shè)定的verbosity等級來判斷是否需要打印信息出來。

除了信息打印,字符串的格式處理也是很大的開銷。如果借用report的管理機(jī)制來判斷是否有必要進(jìn)行字符串格式處理,可以非常有效地提高仿真速度。

如下例程,帶有條件判斷的代碼在三款主流仿真工具上都能帶來仿真速度收益,而且這個收益非常大,達(dá)到了33倍~100倍。

減少不必要的端口采樣或驅(qū)動

這是另一種減少不必要操作的技巧。要知道在UVM中,操作TLM analysis port是開銷比較大的,因?yàn)槎丝诘尿?qū)動行為,都會通過回調(diào)機(jī)制來執(zhí)行關(guān)聯(lián)到該端口的所有consumer的端口動作。理解這個實(shí)現(xiàn)機(jī)制,其實(shí)還得看看UVM的源碼,這里就不做展開解析了。

此外,某些個analysis port是否連接到其他component是依賴于當(dāng)前的驗(yàn)證環(huán)境的,如果根據(jù)analysis port的狀態(tài)判斷是否進(jìn)行端口驅(qū)動,可以減少一些不必要的操作。

如下例程,在monitor的run_phase中根據(jù)其analysis port狀態(tài)來進(jìn)行端口采樣和廣播給其他組件,可以帶來一部分的仿真速度收益。

用回調(diào)函數(shù)代替低效的隨機(jī)約束

SystemVerilog提供了很多種隨機(jī)化變量和添加隨機(jī)約束的方法,具體可以參考公眾號的另外兩篇文章《暗藏玄機(jī)的SV隨機(jī)化》《五花八門的SystemVerilog隨機(jī)約束》。在設(shè)計(jì)隨機(jī)約束的時候,除了要確保約束不沖突(即約束有解)之外,還需要避免產(chǎn)生無效的約束解。

其實(shí),SV已經(jīng)提供了pre_randomize() / post_randomize()兩個分別在求解隨機(jī)值前后會執(zhí)行的回調(diào)函數(shù)。靈活使用這兩個函數(shù)可以避免一些非常低效的約束行為。

如下例程,使用post_randomize對隨機(jī)后的數(shù)列進(jìn)行排序,可以避免在約束中使用循環(huán)去限制每一個數(shù)列元素,從而獲得數(shù)十倍的仿真速度提升。

參考文獻(xiàn)

[1] Cliff Cummings, John Rose, Adam Sherer. "Yikes! Why is My SystemVerilog Still So Slooooow." (2019)

[2] IEEE Standard Association. "IEEE Standard for SystemVerilog-Unified Hardware Design, Specification, and Verification Language." (2013).

審核編輯 黃昊宇

-

仿真

+關(guān)注

關(guān)注

51文章

4250瀏覽量

135448 -

服務(wù)器

+關(guān)注

關(guān)注

13文章

9730瀏覽量

87453 -

eda

+關(guān)注

關(guān)注

71文章

2904瀏覽量

176772

發(fā)布評論請先 登錄

SystemVerilog中的類構(gòu)造函數(shù)new

[啟芯公開課] SystemVerilog for Verification

如何用questasim進(jìn)行systemverilog仿真

round robin 的 systemverilog 代碼

SystemVerilog Assertion Handbo

SystemVerilog的斷言手冊

SystemVerilog的正式驗(yàn)證和混合驗(yàn)證

如何利用SystemVerilog仿真生成隨機(jī)數(shù)

SystemVerilog中枚舉類型的使用建議

一些有趣的數(shù)組相關(guān)的SystemVerilog約束

解碼國產(chǎn)EDA數(shù)字仿真器系列之二 | 如何實(shí)現(xiàn)全面的SystemVerilog語法覆蓋?

一些有趣的數(shù)組相關(guān)的SystemVerilog約束

如何實(shí)現(xiàn)全面的SystemVerilog語法覆蓋

一些個SystemVerilog高效仿真技巧

一些個SystemVerilog高效仿真技巧

評論