大家應該都有接觸過Intel等公司的Designguide,對于串行總線,他們一般會有一個要求是TX與TX走一起,RX與RX走一起,或者規定如果RX與TX在同一層的話需要非常大的間距。為什么會有這樣的要求呢?那我們就需要弄清楚近端串擾與遠端串擾了。

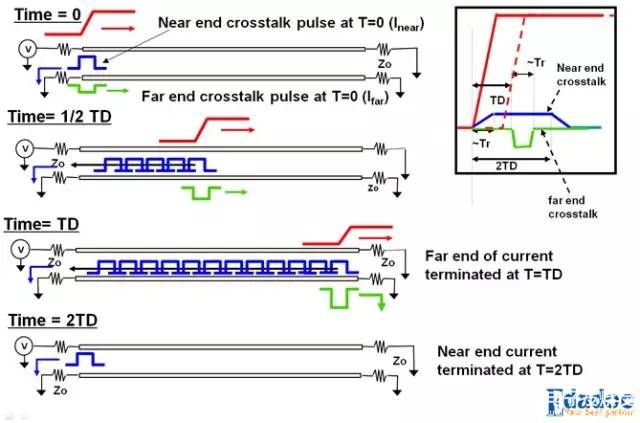

如上一章所見,容性耦合產生的電流分成兩半,一半往近端一半往遠端,而感性耦合產生一個往近端的電流。于是,我們會看到一個這樣的現象:

近端得到了一個持續的噪聲,而由于累加的原因,遠端得到了一個類似于脈沖的噪聲。

近端噪聲的幅值為

而遠端噪聲的幅值為

其中

與

是信號之間的互感與互容,

與

是信號與回流路徑之間的電感與互容。

關于兩個公式,我們不需要去記住,我們只需要知道它告訴了我們什么:攻擊信號的幅值影響著串擾的大小;減小串擾的途徑就是減小信號之間的耦合,增加信號與其回流平面之間的耦合。

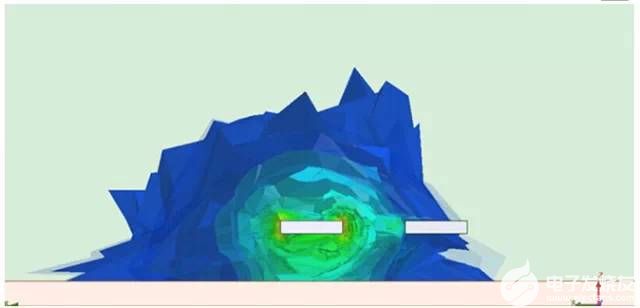

有圖為證:

兩張圖的線寬與線距是相同的。區別在于第二張圖走線與參考平面更近。

還有一點很重要的隱藏在公式中,如果兩線附近為同一種介質的話,有

也就是說,帶狀線是不存在遠端串擾的!而串行總線的輸入阻抗與輸出阻抗通常都為100Ω,這樣近端串擾就不會由源端反射至接收端。所以,將串行總線的RX與TX分開,能減小串擾對串行總線的影響。

審核編輯 :李倩

-

電流

+關注

關注

40文章

7128瀏覽量

134693 -

耦合

+關注

關注

13文章

595瀏覽量

101607 -

串擾

+關注

關注

4文章

189瀏覽量

27398

發布評論請先 登錄

OLI-P——分布式偏振串擾測量利器

什么是近端串擾與遠端串擾?

什么是近端串擾與遠端串擾?

評論