對于現代電子產品來說,從精妙的構思到成為實際的產品,要經過成千上萬個步驟,也需要不同團隊之間的合作,根據產品的復雜程度不同,團隊的大小也不同,小到幾個人,大到成千上萬人皆有可能。

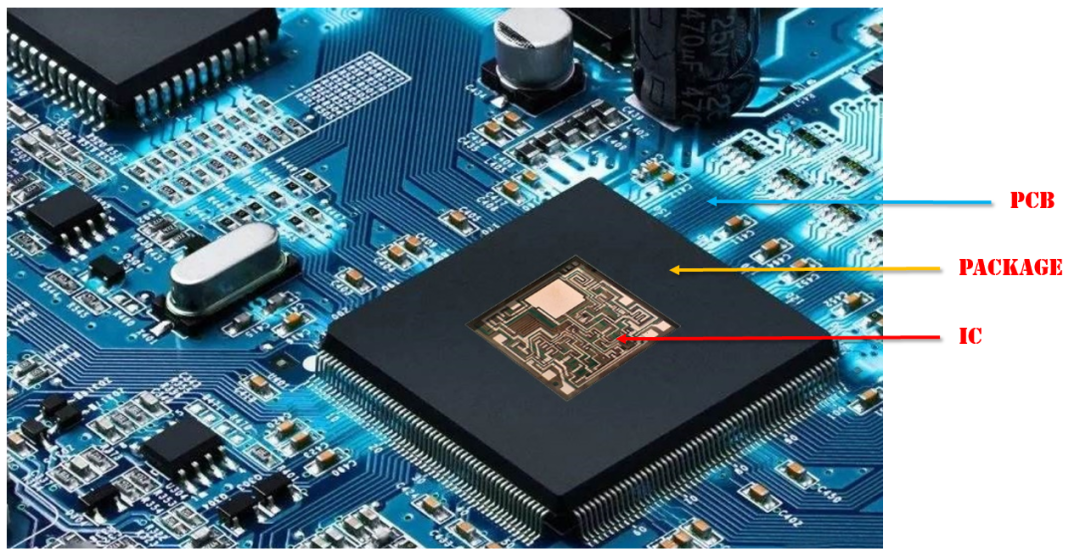

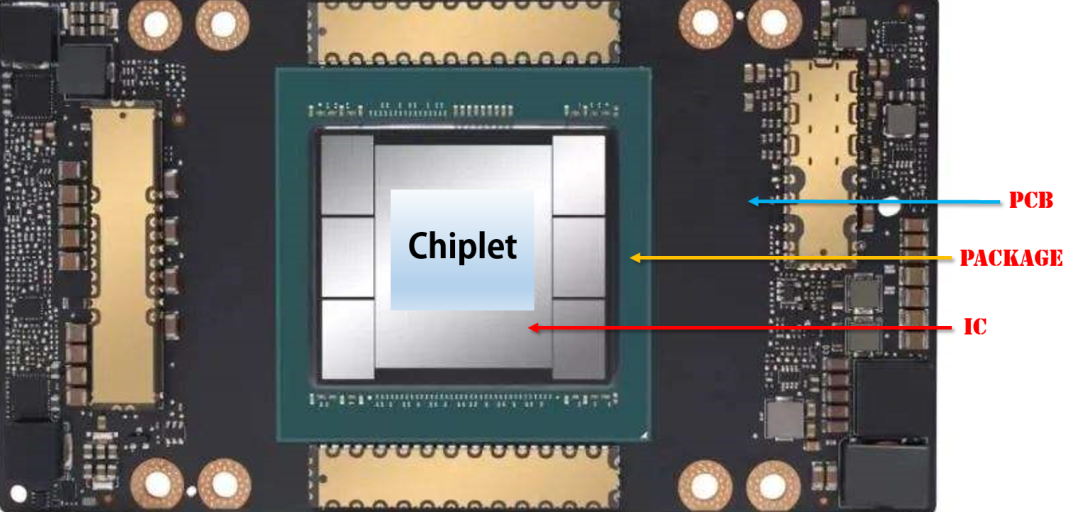

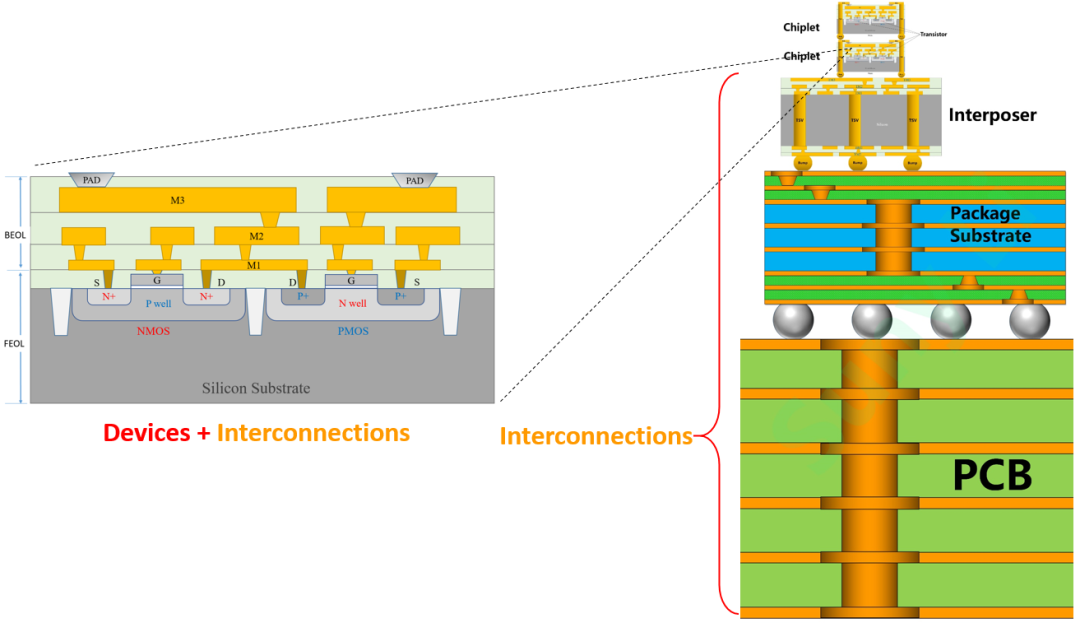

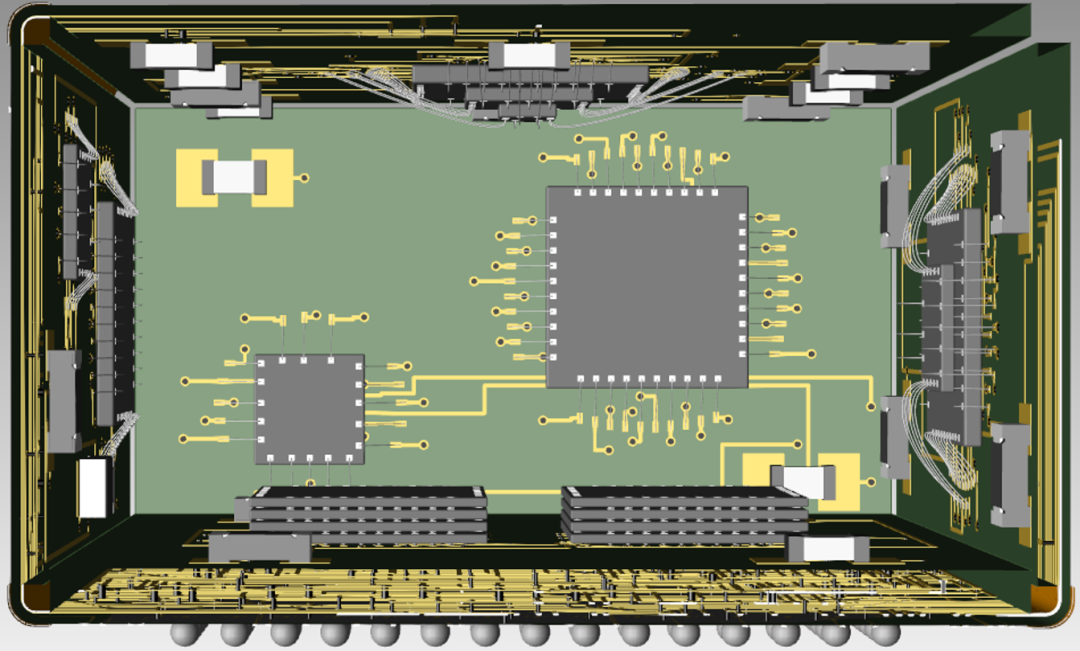

電子系統的集成主要分為三個層次,芯片、封裝、PCB。

IC傳統封裝PCB

IC先進封裝PCB

今天,我們以電子產品為例,結合這三個層次,對產品研發過程中的數據一致性做一些分析和探討。

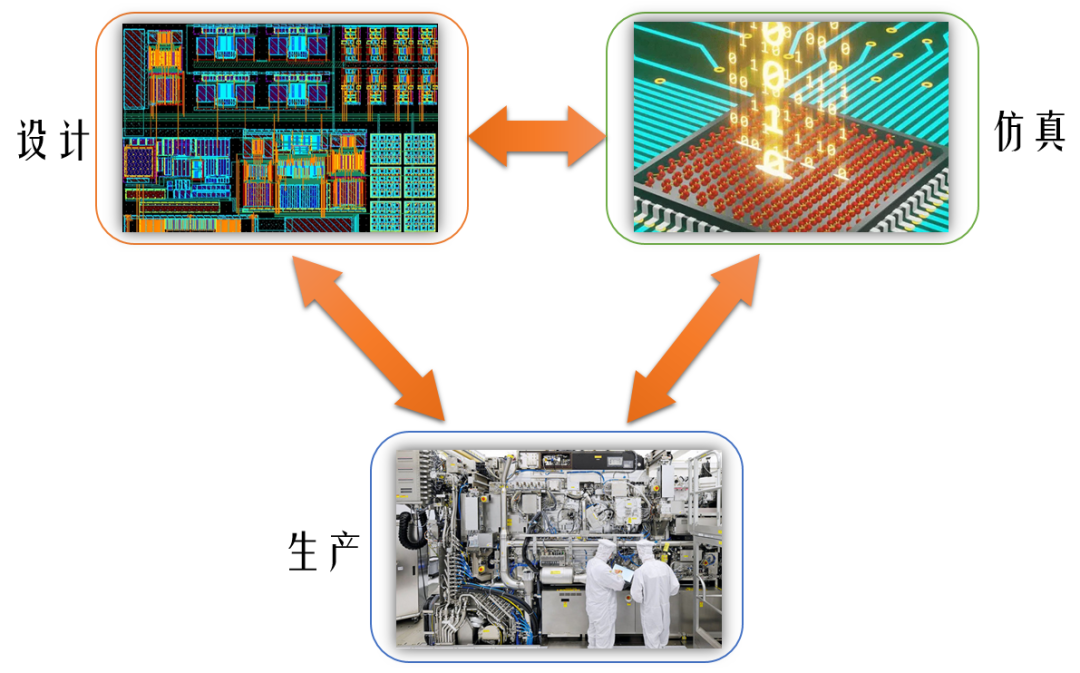

現代電子產品的研發過程一般可以分為三個階段:設計、仿真、生產,如下圖所示。

設計就是將設計者的思想變成可以生產的圖形的過程,仿真則是驗證這些圖形是否能夠滿足設計要求并對此進行優化,生產則是將圖形制造出來并組合到一起形成實物,實現設計的目的。

以芯片為例,分為設計、仿真、驗證、生產等環節,設計解決的是模型的構建,也就是從0到1(從無到有)的問題,仿真和驗證對模型進行確認和優化,也就確認設計中的1到底是等于1、大于1還是小于1的問題,并對相應的問題進行修正,從而以提高芯片一版成功的幾率。

芯片設計規模越大,工藝節點越小,對流片(Tape Out)成功的要求也越高,因此,對仿真驗證環節的要求也會更高。

由于篇幅關系,對于芯片這里我們就不展開討論。

對于封裝和PCB來說,其設計、仿真、生產的流程基本上是一致的,尤其當封裝進化為SiP和先進封裝之后,二者都屬于電子集成技術,只是實現的層次不同。封裝中的設計單元是裸芯片Chip或者Chiplet,而PCB中的設計單元是封裝好的芯片,是前者集成的產出物。

因此,我們下面的討論中,并不專門區分封裝和PCB,而統一進行設計、仿真、生產的論述。

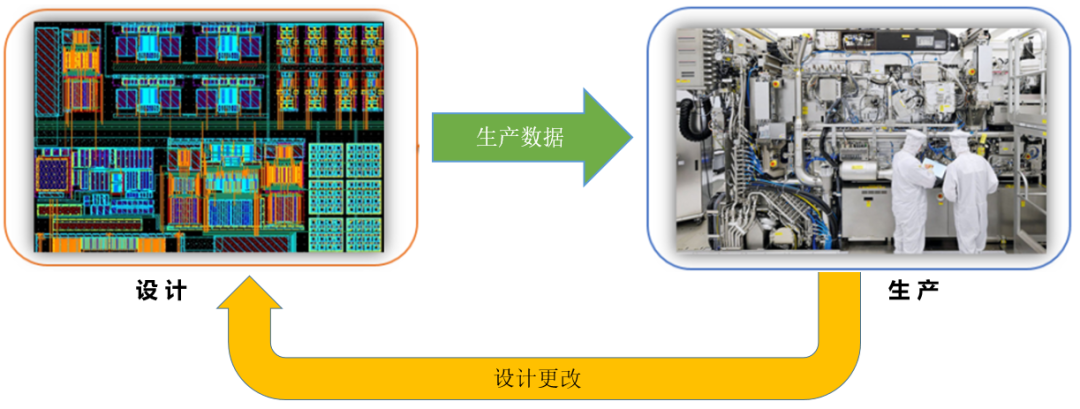

早先的產品研發,仿真環節相對比較淡化,設計完成后往往直接進行生產,然后再進行調試,修改,再生產,整個產品研發周期比較長,需要經過多次重復才能達到預期的目的。

隨著設計復雜程度的提高,投產一次的成本也日益高漲,設計-->生產的模式已經無法滿足產品的需求。生產之前,沒有經過充分且完備的仿真分析,幾乎是不可能做出成功的產品。

這就需要在設計和生產環節之間加入仿真環節,并且仿真的重要性日益提高。隨著仿真技術的發展和日益成熟,出現了一些新的概念和名詞,例如數字化樣機,數字化雙胞胎、數字孿生等概念,二者從本質上來講都屬于仿真的范疇。由此也可以看出業界對仿真環節的重視。

設計最終成為產品,生產環節至關重要,設計的目的就是為了生產,因此,從設計到生產的數據傳遞久經考驗,是比較成熟穩定的,例如芯片從設計到生產常用的數據格式為GDSII,PCB從設計到生產常用的數據格式為Gerber,封裝則較為特殊,從早先傳統封裝的DXF到SiP常用的Gerber再到先進封裝常用的GDSII。

對于從設計到仿真,其數據的傳輸方式則更為靈活和多樣化,但其成熟度要稍遜于設計到生產的數據傳遞。

在仿真中,我們將需要仿真的元素分為兩大類:Active 有源類,主要包括各類元器件,Passive 無源類,主要包括互連模型和RLC等無源器件。

對于仿真來說,最重要的就是模型的構建。模型可分為器件模型(Devices)和互連模型(Interconnections),器件模型也被稱為主動模型(Active Model),互連模型也被稱為被動模型(Passive Model),RLC一般也被定義在互連模型中。

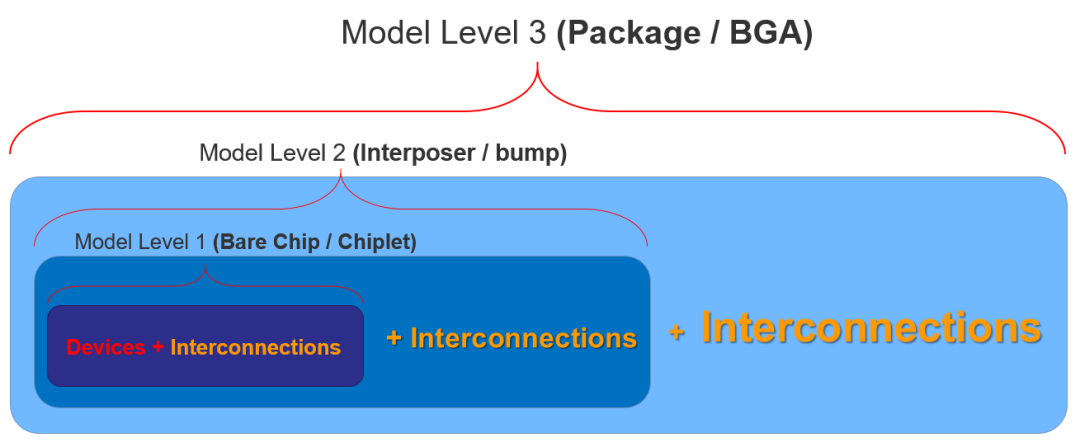

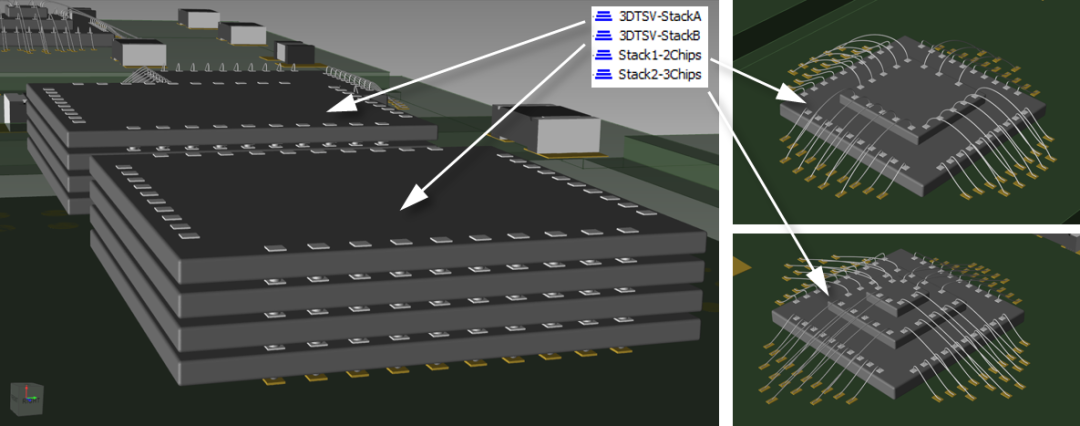

嚴格來說,從芯片到PCB的多級集成中,真正的器件模型只存在于第一個層次的集成中,即芯片中的晶體管模型,其他層次的集成如Interposer, Package、PCB中均為互連模型,如下圖所示。

同時,有一點非常重要,就是:器件模型+互連模型=>新的器件模型,是對本層次的模型化描述,并作為模型應用在下一個層次的仿真中。

例如在芯片內部,用器件模型來描述晶體管,其他的互連線和RLC都被視為互連模型;到了封裝層次,芯片整體作為一個器件模型,封裝中的互連線,平面層,RLC等被視為互連模型;到了PCB層次,封裝好的SiP或先進封裝(里面包含多塊芯片和它們之間的互連)作為器件模型,PCB上的互連線,平面層,RLC等被視為互連模型。

從下圖中,我們可以看出,芯片中的晶體管和互連形成第一級別的模型,再加上Interposer上的互連和Bump形成第二級別的模型,再加上封裝基板上的互連和BGA形成第三級別的模型。

不同級別的分類也可以根據實際需求進行靈活調整,例如將Interposer上的互連和封裝基板的互連統一處理,形成芯片和封裝兩級模型。

從上面的描述,針對封裝和PCB,我們可以得出如下結論:器件模型來源于上一層次的集成,在本層的集成主要是針對互連模型。

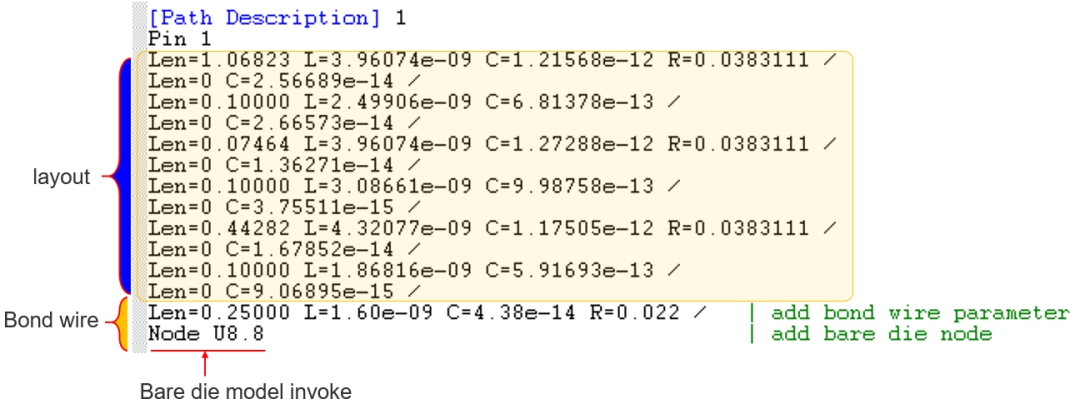

下面就是對典型封裝互連模型描述的實例,分為基板上的布線Layout和鍵合線Bond wire,是通過RLC參數對不同段的Layout或者Bond wire進行描述。

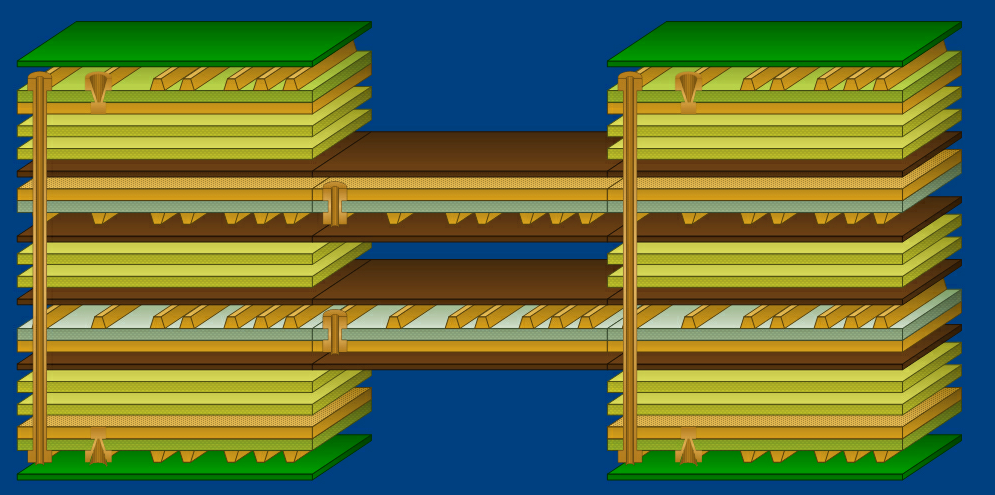

在封裝和PCB的原理圖和版圖設計中,主要的任務就是進行正確的互連,原理圖根據器件的功能對其邏輯互連關系進行定義,并傳遞到版圖,版圖依此是對物理互連分層繪制,并通過過孔或者TSV將各層連接起來。

生產則是將版圖的每一個物理層制造出來并組合到一起,使器件的功能正常運行并實現設計的目標,為了保證這個目標順利實現,在生產之前需要進行充分的仿真。

從設計數據到仿真數據,中間需要經過數據的傳遞和轉換。

對于版圖來說,需要傳遞的數據包括版圖層疊結構、每一層的材料、厚度、物理參數等,隨著設計復雜程度的提高,需要傳遞的數據愈發復雜。

例如,對于剛柔結合板 Rigid-Flex,由于要進行多種彎曲,不同的位置厚度和材料會有所不同,因此整個版圖會有會有多個層疊結構和多個區域,稱為Multi-stackup和Multi-zone再加上Multi-bend,設計數據比較復雜。

對于Interposer,其互連數量可能超過10萬+,巨大的數據量對設計和仿真工具都提出了新的要求,有時候讀入數據甚至需要數小時甚至更長的時間,其仿真過程更是需要數天甚至數周的時間。

作為設計工具的下游,仿真工具通常對設計工具的數據有較好的兼容性,多數仿真工具都可以直接打開設計文件,并將其轉換成自有的格式。

然而,隨著設計的日益復雜,能夠正確識別設計數據就成為仿真工具的重大挑戰,例如,設計工具可以準確地描述芯片堆疊、腔體、鍵合線,導入仿真工具后,不同的元素可能會出現錯位,設計工具可以準確地描述多層疊結構、多區域、多個彎曲,導入仿真工具后,層疊、區域、彎曲均可能出現偏差,這些錯位和偏差,輕則導致仿真精確度下降,嚴重則導致無法仿真。

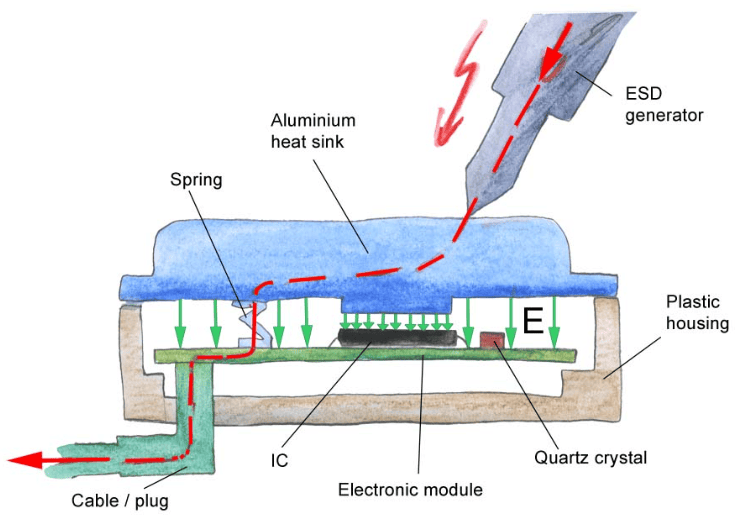

從二維空間升級到三維空間,對設計、仿真和生產都帶了挑戰。

早先的EDA設計工具基本都是平面化的,從頂視圖的角度去瀏覽每一層信息,現在設計工具逐漸走向3D化。就目前來說EDA工具的設計界面還是2D的,通常會有一個3D的瀏覽窗口,可以查看詳細的3D信息。

仿真工具的挑戰主要來源于設計工具數據的復雜化,因為設計數據變成了3D的,仿真工具需要正確識別這些數據并正確解析,包括3D結構、網絡、端口、材料信息等都需要準確地從設計工具傳遞到仿真工具,否則,就需要在仿真工具中做大量的工作補充或者修正這些信息,才能做到仿真數據和設計數據的一致性。

同時,仿真算法也需要更新或者重新開發,以適應新的復雜的3D設計數據。

專注于電路仿真的軟件通常3D功能比較弱,專注于電磁場仿真的軟件3D功能較強,但對數據的規模和復雜度有一定限制,如果設計特別復雜,數據規模大,復雜度高,設計數據中可能包含了2D2D+2.5D3D4D等多種集成技術,一般仿真工具很難正確導入,或者需要花費很長的時間解析和導入。

目前,很多傳統仿真工具還無法正確識別設計中的各種三維元素,如多級芯片堆疊,復雜多層鍵合線,2.5D和3D硅通孔,復雜基板彎曲等,無法識別正確的設計模型,更無法進行精確的仿真。因此,針對目前復雜的集成技術,仿真工具還有很大的發展空間,這也給新的仿真工具提供了機會。

設計構建了模型,仿真對模型進行了驗證和優化,使之更加準確,從在生產環節中,將模型具體化,做成產品。

如果設計、仿真、生產能夠做到數據的一致性,則可以在最大程度上保證產品一版成功。這也需要設計人員、仿真人員,生產人員協同地工作和努力。

審核編輯 :李倩

-

芯片

+關注

關注

459文章

52087瀏覽量

435241 -

pcb

+關注

關注

4348文章

23392瀏覽量

406118 -

封裝

+關注

關注

128文章

8444瀏覽量

144665

原文標題:設計 | 仿真 | 生產 的數據一致性?

文章出處:【微信號:算力基建,微信公眾號:算力基建】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

宏微科技亮相2025德國紐倫堡電力電子系統及元器件展覽會

宏微科技受邀參加2025德國紐倫堡電力電子系統及元器件展覽會

愛普生車規級晶振SG2520CAA智能汽車電子系統的應用

羅徹斯特電子的商用航空電子助力經驗證的航空電子系統

集成電路電磁兼容性及應對措施相關分析(一) 電子系統性能要求與ESD問題

集成電路電磁兼容性及應對措施相關分析(一) — 電子系統性能要求與ESD問題

Celsius EC Solver:對電子系統散熱性能進行準確快速分析

虛擬設計與優化電力電子系統依賴于半導體芯片模型

西門子創新搭載AI的電子系統設計軟件概述 Xpedition NG和HyperLynx NG軟件

FPGA仿真黑科技\"EasyGo Vs Addon \",助力大規模電力電子系統仿真

西門子EDA發布下一代電子系統設計平臺

使用泰克示波器精確診斷并優化汽車電子系統

電子系統的集成三個層次,芯片、封裝、PCB

電子系統的集成三個層次,芯片、封裝、PCB

評論