Address collision 指的是RAM的兩個port同時訪問相同的地址可能導致數據發生錯誤的情況。在Xilinx中,不同的RAM,不同的RAM配置會導致address collision時不同的數據結果。

Distributed RAM

對于DRAM,寫數據是 synchronous write,需要一個時鐘周期, 讀數據是 asynchronous read,當前時鐘周期就能讀出數據。因此當在某一個cycle讀寫同時訪問同一地址時,讀數據是 old data,即該地址原存放的數據而不是新要寫入的數據。

Block RAM

BRAM的讀寫都是 synchronous。BRAM的兩個Port分別為 PortA 和 PortB。

我們可以將 BRAM address collision 分為以下三類。

PortA 和 PortB 同時讀數據

兩個Port都會正確讀出該地址中的數據。

PortA 和 PortB 同時寫入數據

該地址最終被寫入的數據是 non-deterministic。因此設計中要避免兩個port同時寫數據的address collision。

PortA 寫數據同時 PortB 讀數據,或者是 PortA 讀數據同時 PortB 寫數據

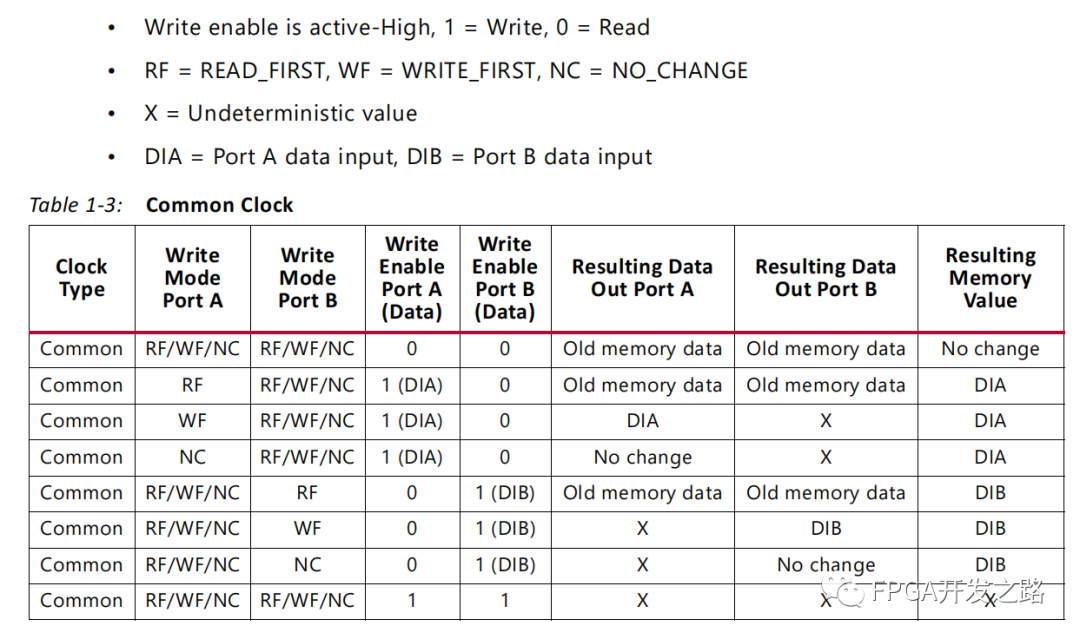

在這種情況下,數據總是會被正確寫入到RAM中,但是讀出的數據內容則依賴于BRAM的配置。BRAM的write mode可以配置為三種模式,write first,read first 和 no change。

下圖為不同配置下的數據讀寫結果。可以看到當 write port 配置為 READ_FIRST時,不管 read port 如何配置,都會讀出 old data。而當 write port 配置為 WRITE_FIRST 或 NO_CHANGE時,不管 read port 如何配置,讀數據都是 X,即 undeterministic。因此在可能發生address collision 的BRAM,一般將兩個 port都配置為 READ_FIRST,以確保數據讀出的正確。

Ultra RAM

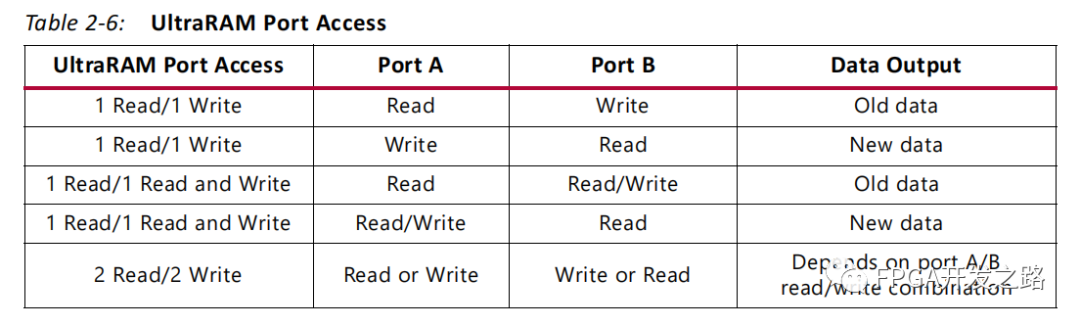

URAM的讀寫也都是 synchronous。URAM比較有意思的一點是,PortA 總是先于 PortB 執行操作,因此在 address collision 我們會看到不同于BRAM的結果。

PortA寫,PortB讀。PortB 會讀出new data。(因為PortA先執行,所以在PortB讀執行時,new data已經寫入RAM中了)

PortA讀,PortB寫。PortA 會讀出old data。(同樣的,這也是因為PortA先執行)

PortA寫,PortB寫。最終該地址寫入的值是PortB的值。(PortB因為后執行會覆蓋PortA寫的值)

Reference

《UltraScale Architecture Configurable Logic Block》

《UltraScale Architecture Memory Resources》

審核編輯 :李倩

-

數據

+關注

關注

8文章

7233瀏覽量

90816 -

RAM

+關注

關注

8文章

1386瀏覽量

116516 -

Xilinx

+關注

關注

73文章

2179瀏覽量

123994

原文標題:Xilinx RAM Address Collision

文章出處:【微信號:FPGA開發之路,微信公眾號:FPGA開發之路】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

工業數據采集如何避免IP沖突問題

局域網地址檢測器

工廠局域網出現設備IP沖突如何解決

什么原因會導致IP地址沖突?

ram芯片為什么要設置片選引腳

一般ram芯片上的引腳有哪些

PLC的IP沖突如何解決(NAt物聯網解決方案)

工業設備IP地址沖突如何通過NAT網關解決

ram存儲的數據在斷電后會丟失嗎

汽車裝配車間設備IP沖突的解決方案

工廠局域網設備IP沖突的解決方案

IP地址沖突解決方法圖示

兩個路由器ip地址沖突怎么解決

NAT網關實現工業設備網段隔離,解決IP沖突問題

如何解決工廠中相同IP設備沖突故障問題

Xilinx RAM地址沖突

Xilinx RAM地址沖突

評論