引言:在需要多個FPGA芯片的應用中,如果JTAG鏈上所有FPGA采用相同配置,可以通過“成組”加載方式同時加載;如果每個FPGA需要采用不同的配置數據流,可以通過“菊花鏈”加載方式或者使用外部邏輯依次加載。本文分別介紹串行配置和并行配置模式下的多片FPGA配置數據流加載方式。

1.菊花鏈串行配置模式(串行,多片FPGA采用不同配置流)

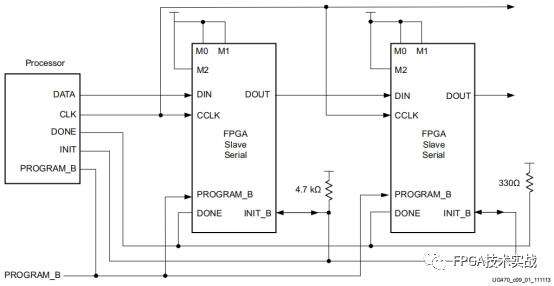

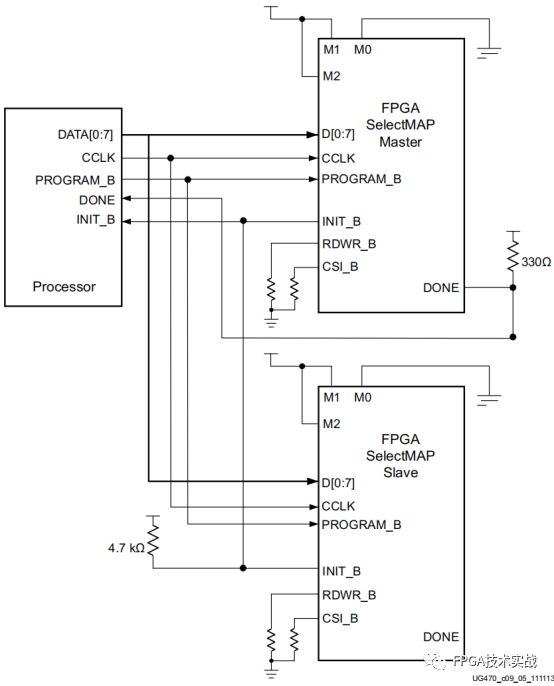

單一配置源可以通過利用串行菊花鏈方式加載多片7系列FPGA。在串行菊花鏈中,器件通過DIN管腳接收配置數據,通過DOU管腳將配置數據傳輸給下游器件。離配置源最近的器件稱為最上游器件,離配置源最遠的器件稱為最下游器件。如下圖所示。

圖1 Slave串行模式菊花鏈配置

在串行菊花鏈中,所有器件都設置為串行模式,配置時鐘由外部提供,如圖1中的Processor設備。如圖1所示:

1)DONE管腳為開路輸出,在Slave串行菊花鏈中應連接在一起,在最遠一片FPGA上拉;

2)INIT_B管腳為雙向管腳,開路,需要外部上拉電阻;

3)比特流啟動時鐘必須設置為CCLK。

串行菊花鏈中的第一個器件是最后加載數據流的。在配置鏈中的最后一個器件完成配置,并通過CRC校驗,進入啟動順序。在所有器件釋放它們的DONE管腳后,DONE信號上拉為高或者有鏈路中第一個器件驅動為高。

7系列FPGA與早期Virtex/Spartan系列FPGA串行菊花鏈連接考慮

1)許多較舊的FPGA設備無法接受7系列設備所能產生的CCLK頻率。選擇鏈中所有設備支持的配置CCLK速度;

2)7系列設備應始終位于串行菊花鏈的開頭,而較舊的系列設備位于鏈的末端;

3)為7系列FPGA位流選項提供的指南應盡可能適用于串行菊花鏈中的所有設備;

4)設備可通過其DOUT引腳的配置位數有限。對于從Virtex II系列開始的7系列和Virtex設備,限制為4294967264位。對于Spartan-6和Spartan-3代設備,限制為2147483632位。所有下游設備的比特流長度總和不得超過此數字。

串行菊花鏈配置設計要點

1)啟動順序

應在DONE之前或在DONE的同一周期內釋放,以確保所有DONE引腳釋放后,設備可正常工作。

2)連接所有DONE管腳

所有設備的DONE引腳必須以串行菊花鏈連接,以防止配置失敗。出于調試目的,有一種斷開單個DONE的方法通常很有用,從而可以通過串行或JTAG接口單獨配置設備。

3)DONE管腳上升時間

釋放所有DONE引腳后,DONE引腳應從邏輯0上升到邏輯1。如果DONE信號上升需要額外的時間,可以通過DonePipe選項設置,參看UG628。

2.成組串行配置模式(串行,多片FPGA采用相同配置流)

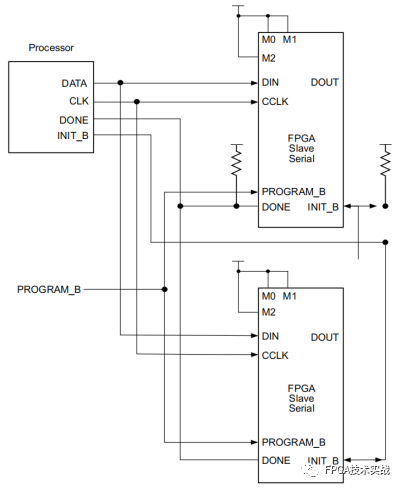

使用成組串行配置設置,可以從同一位流源同時配置多個設備(圖9-2)。在這種布置中,串行配置引腳被連接在一起,使得每個設備看到相同的信號轉變。對于成組串行配置,所有設備必須相同。配置可以由外部配置控制器驅動,從閃存或其他存儲器讀取位流。

圖2 成組串行配置模式 如圖2所示:

1)DONE引腳為漏極開路輸出;

2)INIT_B引腳是雙向開放漏極引腳。需要外部上拉電阻器;

3)必須為串行配置的CCLK設置啟動時鐘設置;

4)對于成組串行配置,所有設備必須相同(相同的ID CODE),并且必須使用相同的比特流進行配置。

成組串行配置考慮要點

1)啟動順序

應在DONE之前或在DONE的同一周期內釋放,以確保所有DONE引腳釋放后,設備可正常工作。

2)DONE管腳可斷開

出于調試目的,有一種斷開單個DONE的方法通常很有用,從而可以通過串行或JTAG接口單獨配置設備。

3)CCLK作為電路板時鐘信號布局布線

CCLK信號相對較慢,但7系列FPGA輸入緩沖器上的邊緣速率非常快。即使CCLK信號上的輕微信號完整性問題也會導致配置失敗。典型的故障癥狀是DONE仍然為低,INIT_B為高。因此建議采用注重信號完整性的設計實踐,包括IBIS的信號完整性仿真。

4)用于組合串行配置的PROM

用于組合串行配置的PROM文件與用于配置單個設備的PROM相同。沒有特殊的PROM文件注意事項。

3.成組串行配置模式(并行Slave,多片FPGA采用不同配置流)

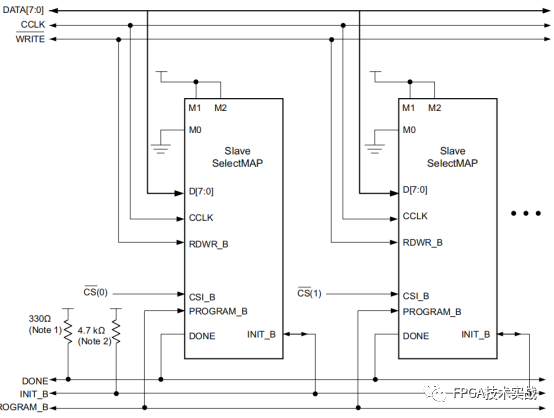

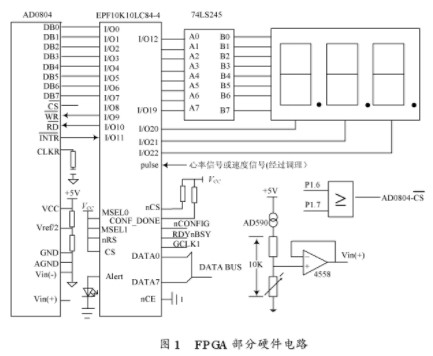

處于從屬SelectMAP模式的多個7系列設備可以連接在一個公共SelectMAP總線上,如圖3所示。在SelectMAP總線中,DATA、CCLK、RDWR_B、PROGRAM_B、DONE和INIT_B引腳在所有設備之間共享公共連接。

為了允許單獨訪問每個設備,不得將CSI_B(芯片選擇)輸入連接在一起。需要CSI_B信號的外部控制,通常由微處理器或CPLD提供。

圖3 從屬SelectMAP模式的多個7系列設備

如果要在配置后對設備執行回讀,則必須正確處理RDWR_B信號。否則,RDWR_B可能被綁定為低。

如圖3所示:

1)DONE引腳為漏極開路輸出;

2)INIT_B引腳是雙向開放漏極引腳。需要外部上拉電阻器;

3)不支持回退重新配置;

4)必須為SelectMAP配置的CCLK設置啟動時鐘設置;

5)需要諸如微處理器或CPLD的外部控制器來控制配置;

6)數據總線可以是x8、x16或x32(用于從屬SelectMAP)。

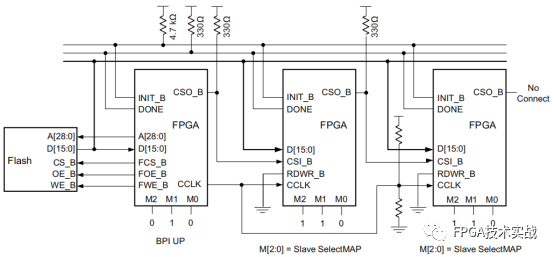

4. 并行菊花鏈配置模式(主/從并行,多片FPGA采用不同配置流)

7系列FPGA配置支持并行菊花鏈。圖4顯示了BPI模式下主導設備的示例示意圖。

主導設備也可以處于主或從SelectMAP模式。D[15:00]、CCLK、RDWR_B、PROGRAM_B、DONE和INIT_B引腳在所有設備之間共享公共連接。CSI_B引腳為菊花鏈。

圖4 并行菊花鏈

如圖4所示:

1)DONE引腳為漏極開路輸出;

2)INIT_B引腳是雙向開放漏極引腳,需要外部上拉;

3)必須為SelectMAP配置的CCLK設置啟動時鐘設置;

4)應啟用FCS_B、FWE_B、FOE_B、CSO_B弱上拉電阻器,否則每個引腳需要外部上拉電阻器。默認情況下,所有多功能I/O都具有配置后的弱下拉;

5)鏈中的第一個設備可以是主SelectMAP、從SelectMAP或BPI。以下設備必須處于從屬SelectMAP模式;

6)不支持并行菊花鏈方案中的回讀;

7)不支持回退重新配置。

5. 并行成組配置模式(并行,多片FPGA采用相同配置流)

也可以通過使用成組的SelectMAP配置,使用相同的配置位流同時配置多個設備。

如圖5所示,在成組SelectMAP布置中,兩個或更多設備的CSI_B引腳連接在一起(或連接到GND),使所有設備識別D引腳上顯示的數據。

圖5 成組的SelectMAP配置

如圖5所示,如果外部振蕩器可用,所有設備都可以設置為Slave SelectMAP模式。

1)不支持同步SelectMAP模式;

2)不支持回退重新配置;

3)DONE引腳為漏極開路輸出;

4)INIT_B引腳是一個雙向開放漏極引腳,需要外部上拉電阻器;

5)必須為SelectMAP配置的CCLK設置啟動時鐘設置;

6)公共DONE信號上需要一個外部上拉電阻器。由于扇出增加,設計者必須仔細關注信號的完整性。建議進行信號完整性模擬;

7)如果CSI_B信號連接在一起,則無法進行回讀,因為所有設備都同時嘗試驅動數據信號。

審核編輯:劉清

-

FPGA

+關注

關注

1640文章

21893瀏覽量

611044 -

JTAG

+關注

關注

6文章

403瀏覽量

72579 -

CRC校驗

+關注

關注

0文章

84瀏覽量

15440 -

FPGA芯片

+關注

關注

3文章

246瀏覽量

40111 -

DIN

+關注

關注

0文章

16瀏覽量

10869

原文標題:Xilinx 7系列FPGA架構之器件配置(四) 之多片FPGA配置

文章出處:【微信號:FPGA技術實戰,微信公眾號:FPGA技術實戰】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

勇敢的芯伴你玩轉Altera FPGA連載51:Altera FPGA配置方式概述

勇敢的芯伴你玩轉Altera FPGA連載52:Altera FPGA配置方式之AS/PS/JTAG配置方式

基于FPGA芯片的數據流結構分析

Altera Cyclone II FPGA的幾種代碼配置

串行配置和并行配置模式下的多片FPGA配置數據流加載方式

串行配置和并行配置模式下的多片FPGA配置數據流加載方式

評論