數據流(Data Flow)是控制流中的核心組件,用于把數據提取到服務器內存中,轉換數據并把數據寫入到目標結構中。

2020-11-06 11:19:03 4074

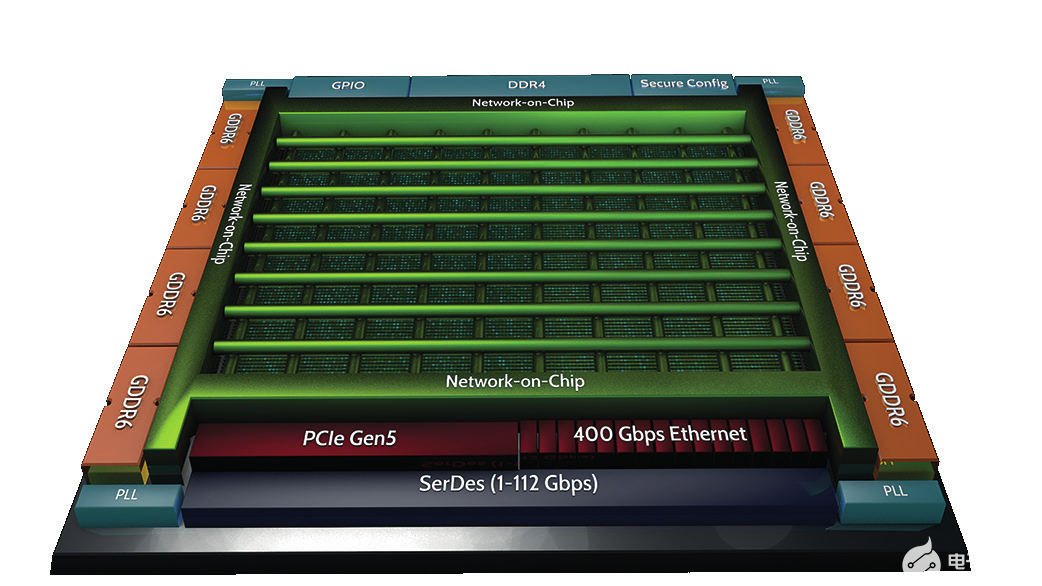

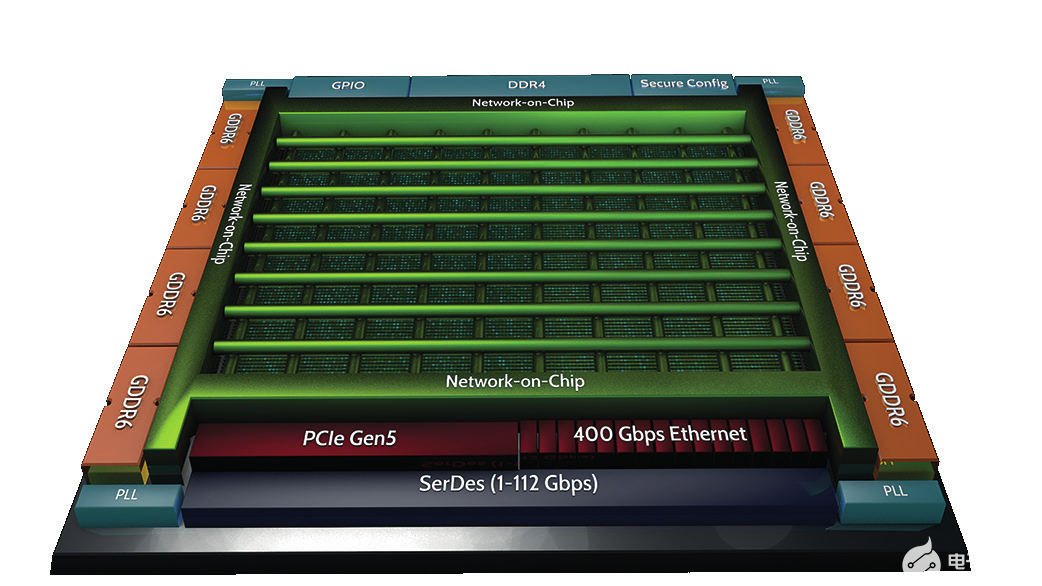

4074 隨著數據中心、人工智能、自動駕駛、5G、計算存儲和先進測試等應用的數據量和數據流量不斷增大,不僅需要引入高性能、高密度FPGA來發揮其并行計算和可編程硬件加速功能,而且還對大量數據在FPGA芯片內外

2022-07-06 15:48:52 798

798

最近準備采用Xilinx FPGA進行多機通信,即主FPGA芯片將采集到的不同層的圖像數據流分別輸出給對應的4塊從FPGA芯片中,主從FPGA之間的連接機制采用星形拓撲結構。經計算,圖像數據流接口速率需要數百兆比特/秒,因此需要調研FPGA支持的常見IO接口標準,及每種接口的應用場合。

2022-10-17 09:14:18 1626

1626 ,實際上每一個系列的FPGA都有其相應的內部結構),FPGA芯片主 要由6部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內嵌的底層功能單元和內嵌

2017-05-09 15:10:02

:將邏輯網表配置到具體的FPGA芯片上,需要在速度和面積之間進行選擇 7、時序仿真:后仿真,是將布局布線延時反標注到設計網表中 8、板級仿真與驗證:應用于高速電路,對高速系統信號完整性,電磁干擾等特征進行分析 9、芯片編程與調試:產生位數據流文件,將編程數據下載到FPGA芯片中

2020-12-04 15:28:09

整個設計消耗的芯片面積,這就是用速度的優勢換取面積的節約。反之,如果一個設計的時序要求很高,普通方法達不到設計頻率,那么一般可以通過將數據流串并轉換,并行復制多個操作模塊,對整個設計采取乒乓操作和串

2021-07-25 11:09:06

整個設計消耗的芯片面積,這就是用速度的優勢換取面積的節約。反之,如果一個設計的時序要求很高,普通方法達不到設計頻率,那么一般可以通過將數據流串并轉換,并行復制多個操作模塊,對整個設計采取乒乓操作和串

2021-07-26 14:47:48

來減少整個設計消耗的芯片面積,這就是用速度的優勢換取面積的節約。反之,如果一個設計的時序要求很高,普通方法達不到設計頻率,那么一般可以通過將數據流串并轉換,并行復制多個操作模塊,對整個設計采取乒乓操作

2021-07-04 14:16:15

來減少整個設計消耗的芯片面積,這就是用速度的優勢換取面積的節約。反之,如果一個設計的時序要求很高,普通方法達不到設計頻率,那么一般可以通過將數據流串并轉換,并行復制多個操作模塊,對整個設計采取乒乓操作和串

2021-11-22 10:04:03

整個設計消耗的芯片面積,這就是用速度的優勢換取面積的節約。反之,如果一個設計的時序要求很高,普通方法達不到設計頻率,那么一般可以通過將數據流串并轉換,并行復制多個操作模塊,對整個設計采取乒乓操作和串

2021-07-09 14:34:18

來減少整個設計消耗的芯片面積,這就是用速度的優勢換取面積的節約。反之,如果一個設計的時序要求很高,普通方法達不到設計頻率,那么一般可以通過將數據流串并轉換,并行復制多個操作模塊,對整個設計采取乒乓操作

2021-07-09 14:24:42

來減少整個設計消耗的芯片面積,這就是用速度的優勢換取面積的節約。反之,如果一個設計的時序要求很高,普通方法達不到設計頻率,那么一般可以通過將數據流串并轉換,并行復制多個操作模塊,對整個設計采取乒乓操作和串

2021-08-10 14:51:33

來減少整個設計消耗的芯片面積,這就是用速度的優勢換取面積的節約。反之,如果一個設計的時序要求很高,普通方法達不到設計頻率,那么一般可以通過將數據流串并轉換,并行復制多個操作模塊,對整個設計采取乒乓操作和串

2020-08-02 10:45:07

操作的第二個優點是可以節約緩沖區空間。

巧妙運用乒乓操作還可以達到用低速模塊處理高速數據流的效果。

串并轉換設計技巧

串并轉換是FPGA設計的一個

2010-11-01 13:17:36

我正在深入研究協調引導程序的工作方式。特別地,我正在研究數據流是如何工作的,以便能夠發送被破壞的文件。引導加載程序使用Intel十六進制文件。我想確認(似乎的確如此)引導加載程序一次發送一行十六進制

2020-04-06 07:52:47

的SAS接口控制器,可是我不想這么做。主要是擔心這樣寫的話速率高不起來,我現在是這么想的:先找一塊專用的SAS接口芯片,然后我再用FPGA來配置它,使FPGA來控制硬盤的讀寫操作,不知道這樣可不可以?可是我在網上找了很久都沒有找到這種方案的,還請壇子里面了解這塊的給我些幫助,謝謝了~

2015-09-25 01:55:17

ADC有哪幾種運行方式?ADC的數據流是怎樣的?

2022-02-28 07:38:58

我這里的板子用ADV7619芯片在輸入端輸入4K@30Hz的視頻,輸出端在SDR模式下,輸出48bit的RGB444數據流,最后輸入到FPGA芯片做圖像處理。我的問題是,這個48bit的RGB數據流是相鄰24位奇數像素和24位偶數像素的組合嗎

2018-11-20 17:22:15

總線錯誤處理功能。位數據流處理器程序結構如圖 9-11 所示。主要程序代碼如下:[code]//各個數據收發的起始狀態//接收數據的 idle 狀態always @ (posedge clk or posedge rst)beginif (rst)rx_idle

2018-12-21 18:19:17

esp32作為spi從機連接一款AD,該AD芯片上電后就會持續不斷地向外發送數據,如果循環調用spi_slave_transmit(),那么兩次調用之間就會漏掉一些數據。請問從機有沒有辦法在不漏數據的情況下采集這個數據流?

2023-02-17 07:36:20

單選功能按鈕的設計是個很典型的數據流控制實例,文中給出的用LabVIEW本身解決變量沖突、響應時序控制、初始狀態自適應調整等問題的方法,沒有使用事件驅動結構,避免了在測試系統中并行使用事件驅動結構產生的沖突。

2014-12-23 10:11:41

遇到的難題。單選功能按鈕的設計是個很典型的數據流控制實例,文中給出的用LabVIEW本身解決變量沖突、響應時序控制、初始狀態自適應調整等問題的方法,沒有使用事件驅動結構,避免了在測試系統中并行使用事

2019-04-11 09:40:05

小白跪求LabVIEW上位機與下位機(USB3.0高速數據流!!!)之間的通信程序設計,最好是能有現成的例子。不知道LabVIEW是否能支持USB口3.0高速數據流,不是串口,是USB口,最好能達到150M到200M!!

2017-07-22 18:12:21

LabVIEW按照數據流(dataflow)模式運行VI。 當接受到所有所需的輸入時,程序框圖節點將運行。節點在運行時產生輸出端數據并將該數據傳送給數據流路徑中的下一個節點。 數據流經節點的過程

2018-11-20 10:47:21

LabVIEW用NI-DAQmx高速數據流盤TDMS文件格式是NI推薦的文件格式,用于將基于時間的測量數據保存到磁盤,以實現高性能、可用性和復用性。借助NI-DAQmx 9.0,TDMS文件寫入功能

2022-06-10 21:08:17

的6個原型中運行良好。當我連接到FPGA上的參考電壓IO時,其中2個變為不同的電阻值,因此RAM數據流不起作用。我手動手動測試參考電壓引腳以排除出售的問題。在我的工作板上,我在參考電壓電阻12k上測量

2019-06-20 15:21:24

TI AWR1642 學習筆記4之串口數據流解析? 背景:在不使用采集板的情況下,怎么去解析AWR1642 data port打印的數據流,我使用到的工具有串口助手(用于串口數據的打印與查看

2021-07-27 07:59:52

USB數據流模型 本章介紹了數據如何在USB中傳送,將涉及到系統中關于信號的發送和協議定義的一層。對于USB系統中這一層中各個定義的詳細情況可參見第六章和第七章。本章中介紹的數據

2008-06-17 10:32:55

”來滿足數據流的要求。這里待測vi我們用一個“等待”函數來代替。圖3強制人工數據依賴關系“順序結構”順序結構確保:第一幀:開始計時,第二幀:運行“等待”函數或待測vi,第三幀:停止計時并顯示結果。這里

2012-02-14 11:10:54

圖形化編程語言以及數據流 LabVIEW開發環境和其他開發系統(如C、Java等)的最大不同就是:LabVIEW使用的是通常叫做"G"的圖形化開發語言,通過使用這種語言來生

2019-05-28 07:40:05

局部變量和屬性節點即可以用于控制器又可以用于指示器.而數據流是不能直接在兩個指示器中進行數據傳遞的.下面分別用三種傳遞數據的方法來分析一下它們的區別和運行效率.在第三個框圖中,最初我用的是和上兩個框圖同樣的運行

2011-11-30 14:57:54

1、直接數據流,速度最快2、本地變量,速度稍慢3、采用屬性節點Description,速度慢了一個數量級4、直接數據流+屬性節點只增加為兩者單獨調用時間的累加。5、屬性節點Value為什么比屬性節點

2011-11-14 17:13:33

】這個全局變量,或者在外部加上一次while循環,都可以解決掉這個問題,但這個數據流原理我不太清楚是因為什么,有沒有哪位大拿分析分析

2020-08-13 09:53:25

OneNET初始化函數mqtt怎么上傳數據到指定主題如何獲取數據流信息?設備管理

2021-03-30 07:50:57

stm32對于串口數據流的處理,錯過絕對后悔

2021-12-13 06:43:02

` 本帖最后由 蛙蛙蛙 于 2021-4-26 16:08 編輯

本視頻是Combat FPGA開發板的配套視頻課程,本章節課程主要介紹如何從DPHY輸出并行流中提取有效數據、CSI數據流的結構

2021-04-26 15:53:36

本文和設計代碼由FPGA愛好者小梅哥編寫,未經作者許可,本文僅允許網絡論壇復制轉載,且轉載時請標明原作者。OV5640提供了一個DVP接口用來輸出采集到的圖像數據流,本文提供了一個將DVP接口的圖像

2020-02-18 19:56:10

``實現本設計信號數據處理和控制所用的硬件結構如附件圖1(所用FPGA為V5-LX50T):數據流:AD6644對30M中頻信號進行采樣,將14位量化信號輸入FPGA。FPGA對采樣信號做DDC處理

2012-05-28 16:32:43

設計時很重.(2)寫程序驗證首先要實現的就是邏輯驗證或者說是功能驗證,初學者應該首先達到這一層面。今天寫這個帖子想講一下基于數據流的驗證方法,閑言少敘,進入正題。一、仿真數據文件這個數據文件寫的非常

2017-09-27 10:04:50

豐田數據流分析[此貼子已經被作者于2008-6-15 12:00:37編輯過]

2008-06-15 11:03:19

通過FPGA器件本身間接的將數據燒錄到Flash等外部配置芯片中。另一種下載配置是將配置數據流直接下載到配置芯片中。由于JTAG方式靈活多用,尤其是在線調試非常快速便利,因此我們的FPGA核心板電路中就

2016-08-10 17:03:57

本帖最后由 羊駝啊 于 2016-11-3 22:58 編輯

關于全局變量編程和數據流編程。labview里很重要的一個部分就是多線程之間交換數據。不止一本書里提到,要慎用全局變量。理由一般

2016-11-03 22:55:27

關于視頻監視領域的視頻壓縮與數據流知識點總結的太棒了

2021-06-03 06:30:54

本文討論了支持高速數據流處理的技術、最大化系統流處理性能的應用設計和在數據流導入磁盤與數據流導入存儲器應用中可獲得的數據速率基準。

2021-04-29 06:25:46

。它們主要包括晶體管(三極管)、存儲單元、二極管、電阻、連線、引腳等。

隨著電子產品越來越“小而精,微薄”,半導體芯片和器件尺寸也日益微小,越來越微細,因此對于分析微納芯片結構的精度要求也越來越高,在芯片

2024-01-02 17:08:51

汽車數據流分析

2008-06-15 13:10:43

OneNET云平臺GET數據流,使用Finsh/MSH測試命令進行測試。2、軟硬件平臺(1)STM32F103RET6、外部12M晶振(2)ESP8266 WiFi模塊(3)BH1750光照強度傳感器(4

2022-04-24 14:56:59

、3.0發動機數據流定義與解釋別克君威2.0發動機數據流定義與解釋凱越數據流列表凱越發動機數據流定義賽歐數據流列表賽歐數據流定義[此貼子已經被作者于2008-6-15 12:32:57編輯過]

2008-06-15 12:28:25

汽車防盜數據流

2013-08-31 16:23:06

奇瑞數據流分析手冊

2008-06-15 12:02:57

于存儲器的不同系統數據,從而實現不同的芯片邏輯功能,可以在很大程度上提高資源利用率。原始配置FPGA的方法是硬件設計者根據需求設計生成配置數據流,然后通過專用配置芯片對FPGA進行配置,例如通過下載

2019-08-07 06:17:30

嗨,我想知道如何實現/ addtimestamp到數據流讓我們說RTP流。附:我想在kintex FPGA中實現它。以上來自于谷歌翻譯以下為原文Hi,I am wondering how

2018-12-25 10:59:03

在軟件設計中,除了要注意程序架構以外,還應該對程序的數據流進行設計,從輸入到輸出,采用什么樣的一種結構,能夠讓這個系統實時有效,最大限度的挖掘系統的資源,并充分提高系統的性能。我想知道各位是采用什么的思路,請明白人指點一二。

2013-07-23 00:19:23

使用mmWave Demo Visualizer記錄保存的AWR1443BOOST的數據流,該如何解析?有教程么?

2019-06-26 08:07:34

本文以DM270平臺為基礎,設計了DSP端的數據流核心和ARM端的DSP管理者。

2021-04-26 06:11:24

、輸出信號都是由某個時鐘沿驅動觸發器產生出來的。同步時序電路可以很好的避免毛刺,布局布線后仿真,和用邏輯分析儀采樣實際工作信號都沒有毛刺。 5. 乒乓操作“ 乒乓操作 ” 是一個常常應用于數據流控制

2020-09-18 10:32:44

1、直接數據流,速度最快2、本地變量,速度稍慢3、采用屬性Description,速度慢了一個數量級4、直接數據流+屬性節點只增加為兩者單獨調用時間的累加。5、屬性節點Value為什么比屬性節點

2014-11-13 11:16:26

微流控芯片設計汶顥股份專業從事微流控芯片領域,具有深厚的研究與技術基礎,團隊成員有化學、細胞生物學、環境、醫藥等多個學科專業背景,能夠為客戶設計各種復雜功能、不同材質、不同微結構的微流控芯片

2018-06-22 15:59:44

怎么去解析AWR1642 data port打印的數據流?

2021-09-30 09:08:03

想用藍牙給stc32下載程序,一直失敗,估計是藍牙數據流設置和下載器不一樣,我用的是普中的開發板,但是我不知道普中給的自動下載器的數據流,,那個下載器只能設置波特率TVT。。。。有哪位大神知道嗎?望告知謝謝

2017-11-03 22:38:03

想用LABVIEW吧八個通道數據流分開,請問有什么好方案嗎?

2014-02-11 10:38:06

日產汽車數據流分析

2008-06-15 12:10:26

本田數據流分析手冊

2008-06-15 11:00:47

求大佬分享一個基于模擬音頻連接器的全雙工數據流實現方案

2021-06-03 06:06:04

我在NI上下載了labview一個程序,運行起來還有點小問題,我想運行 看看他的數據流,深入的研究下,哪位大神能指導下,怎么增加個仿真信號 和輸出采集,這樣能清楚的看到其整個數據流的過程,謝謝~

2013-12-31 10:40:43

`大家好,我想通過動作一次布爾控件向串口發送一個指令,過1S再自動發送一個指令。1、我用平鋪順序結構把兩個指令分別放進兩個幀里面,顯示無法確定數據流方向。2、請問有什么辦法能滿足我需要求?`

2018-11-01 13:56:36

我想設置AD9122發送一組實數的數據流,(利用FPGA產生的10M載波信號)應該怎樣設置寄存器呢?我的想法是這樣的 1B->E4(旁路預調值,旁路反sinc-1濾波器,旁路NCO

2018-09-26 17:47:05

單片機與電腦通過IIC 通訊,有沒有方法讀取通訊時的數據流。。。

2019-09-19 09:13:07

,該設備接到am335x的spi的數據流方向與sdk內核spi主控制器里的是相反的(如默認d0 in,d1 out,硬件接線剛好相反)。。。。。請問我該在哪里改這個數據流方向呢?是在spi-omap2-mcspi.c里面改么?

2018-06-04 00:33:06

各位大神,求助STM32F4系列的DMA1各通道和數據流的映射表!

2019-04-16 14:42:16

部署實時數據流平臺面臨的五大挑戰

2021-03-17 07:00:02

(包括YCbCr數據流、行場同步信號和像素時鐘)經ITU輸入接口送入FPGA主控芯片。FPGA主控芯片對ITU信號進行解交織和色彩空間轉換,再將轉換后的每個像素的RGB值寫入SDRAM存儲器。再由

2019-04-22 07:00:11

各位大神,我想問一下事件結構中的數據流動問題,比如顯示一個波形,沒有連線就可以顯示了。多謝。

2015-11-14 17:32:09

針對動態Web頁面資源中的實施細粒度和透明訪問控制問題,定義片斷的概念,提出基于數據流分析的“片斷”級Web頁面資源的訪問控制方法,分析數據流中的請求信息與響應片斷的

2009-04-09 09:27:32 23

23 為提高Java軟件的安全性,針對Java程序的脆弱性分析問題,提出一種基于數據流的感染分析法,闡述了具體思路和實現步驟。依據該方法實現的分析系統能有效分析出Java字節碼程序

2009-04-11 09:43:55 11

11 本文基于數據流框架理論,提出了如何將數據流分析方法應用于JAVA 字節碼中,通過建立數據流與半格、數據流和函數調用圖的關系,從而對類型信息進行分析。實驗表明該數據流分

2009-12-25 13:22:59 9

9 針對網絡數據流存儲的瓶頸問題,提出了一種網絡數據流存儲算法分析與實現方法,仿真結果表明,模型能顯著提高網絡數據流的實時存儲能力

2011-05-26 15:57:33 21

21 開銷過大。在此基礎上,基于獨立數據結構的長持續時間數據流的并行檢測算法中不同線程具有本地數據結構,線程之間不需要同步,產生較少的開銷。理論分析與實驗結果表明,基于獨立數據結構的長持續時間數據流的并行檢測算

2018-03-06 15:54:27 0

0

電子發燒友App

電子發燒友App

評論