當裸片尺寸無法繼續擴大時,開發者開始考慮投入對 3D 堆疊裸片方法的研究。考慮用于 3D 封裝的高端器件已經將當前的可測試性設計 (DFT) 解決方案推向了極限。

如果設計人員已經幾乎無法平衡工具運行時間、片上面積需求、向量數量和測試時間,他們如何在 3D 器件上去實現 DFT 呢?

3D IC 測試簡介

幾種設計趨勢相結合,顯著增加了 IC 測試生成所需的計算資源。首先是設計規模和復雜性的增長。與此同時,可用于 2D 封裝測試訪問的 I/O 更少了。

這些因素也導致測試覆蓋率、良率、功耗和互連測試要求承受巨大壓力。3D 裸片堆疊和封裝是改進系統級封裝技術的重要一步。3D 裸片堆疊有多種方法,但它們的共同目標是使用尺寸更小且良率高的裸片進行垂直堆疊。這種策略緩解了大型 2D 或 2.5D 器件的許多測試挑戰。

在對 3D 堆疊中組裝的裸片進行晶圓探針測試時,建議采用高質量的已知良好裸片 (KGD) 測試。KGD 測試通常包括除裸片間互連測試以外的所有封裝測試。

然后,封裝測試需要進行裸片間 (D2D) 互連測試并重新運行 KGD 測試,以確保封裝和組裝期間沒有引入任何缺陷。每個級別的 3D 測試都需要進行故障診斷,包括完整的封裝級堆疊層診斷。

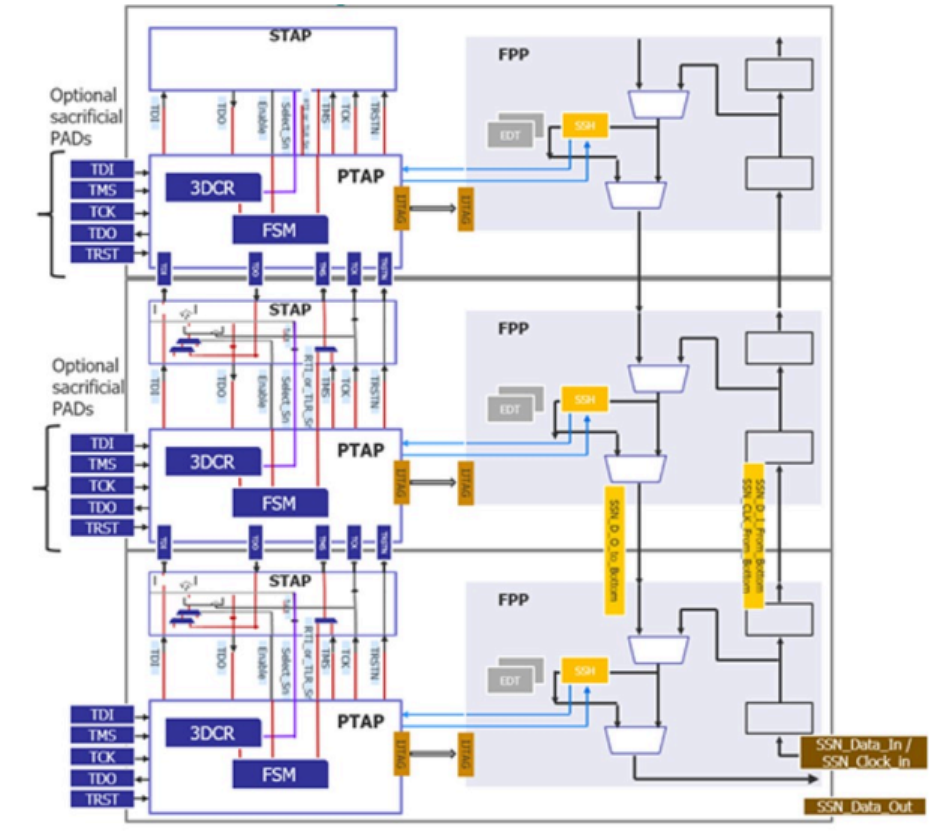

在本文中,我們詳細介紹了一種靈活可擴展、易于實現且全面的 3D IC DFT 解決方案。

圖 1:Tessent 3D DFT 解決方案概述

審核編輯:劉清

-

IC測試

+關注

關注

14文章

45瀏覽量

23761 -

DFT

+關注

關注

2文章

232瀏覽量

23141 -

3D封裝

+關注

關注

7文章

139瀏覽量

27555 -

KGD

+關注

關注

0文章

4瀏覽量

8107

原文標題:易于實現且全面的 3D 堆疊裸片器件測試

文章出處:【微信號:Mentor明導,微信公眾號:西門子EDA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

英倫科技光場裸眼3D顯示產品在博物館裸眼3D顯示方面的應用

中興通訊攜手中國移動推出AI裸眼3D創新產品

中興通訊全場景AI終端應用與裸眼3D新品亮相

裸眼3D筆記本電腦——先進的光場裸眼3D技術

紫光展銳助力全球首款AI裸眼3D手機發布

中興通訊與中國移動發布全球首創AI裸眼3D新品,引領3D科技新浪潮

英倫科技裸眼3D系列:革新視界,盡享未來科技魅力!

英倫科技裸眼3D平板電腦:革新視覺體驗,重塑價格優勢

英倫科技裸眼3D平板有哪些方面的優勢?

什么是光場裸眼3D?

英倫科技裸眼3D顯示屏重塑裸眼3D精彩體驗

易于實現且全面的3D堆疊裸片器件測試方法

易于實現且全面的3D堆疊裸片器件測試方法

評論