1, 介紹

前面的文章《一文搞懂Cortex-A77(ARMv8架構)工作原理》,《一文搞懂cpu cache工作原理》介紹CPU、cache的組成與工作原理,這篇文章將介紹CPU與cache之間的MMU的組成與工作原理。通過本文可以了解CPU訪問的虛擬地址是怎么轉換成物理地址,然后通過物理地址在cache、主存或者EMMC中獲取相應的數據。

早期的內存是比較小的,一般是幾十k,不過相應的程序也是比較小的,這時程序可以直接加載到內存中運行。后來為了支持多個程序的并行,內存中出現了固定分區,在編譯階段將不同程序,劃分在不同的內存區域上。這種方式存在不少問題:一是內存分區大小與程序大小要匹配,二是地址空間無法動態的增長。于是內存動態分區思想便誕生了,內存上線劃出一塊區域給操作系統,然后剩余的內存空間給用戶進程使用,這樣用戶程序所使用的內存空間,跟隨程序大小及數目進行變動。

不論是靜態分析,還是動態分區,都存在一些問題:進程地址空間安全問題、內存使用效率低。為了能夠讓多程序安全、高效地并行運行,物理內存中需要存放多個程序的代碼及數據,這時虛擬內存便誕生了。不得不說虛擬內存是一個偉大的發明,一方面它讓每個程序認為自己是獨自、連續的使用內存,另一方面,每個程序之間的內存形成了安全隔離,避免程序破壞彼此的內存。

后來隨著軟件的快速發展,一個程序的大小變得很大,這時物理內存大小跟不上程序大小增加的速度。這樣便不能將整個程序加載到物理內存中,一是物理內存沒有這么大,二是如果將整個程序加載到內存,為了多程序并行,就需要將大量的數據及代碼換入、換出,這導致程序運行效率低下。

虛擬內存并沒解決高效使用內存的問題,好在程序運行遵循時間、空間局部性原理,進而出現了分頁機制。分頁機制從根本上解決了高效使用物理內存的問題。每次只需要將幾頁的代碼、數據從磁盤中加載到內存,程序就能正常運行。當程序運行的過程中,需要新的代碼、數據會產生缺頁異常,這些代碼、數據就會從磁盤加載到內存,然后程序從異常恢復正常運行。

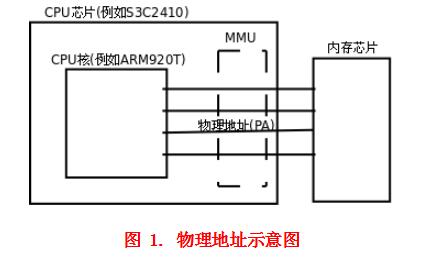

對于支持虛擬內存,分頁機制的系統,處理器直接尋址虛擬地址,這個地址不會直接發給內存控制器,而是先發給內存管理單元(Memory Manager Unit,MMU)。MMU就是負責將虛擬地址轉換和翻譯成物理地址的一個硬件模塊,其實MMU所做的事,完全可以通過CPU來實現。為啥還要一個MMU硬件模塊呢?就是為了提升虛擬地址到物理地址轉換的速度,減少轉換所消耗的時間。

MMU包含兩個模塊TLB(Translation Lookaside Buffer)和TWU(Table Walk Unit)。TLB是一個高速緩存,用于緩存頁表轉換的結果,從而縮短頁表查詢的時間。TWU是一個頁表遍歷模塊,頁表是由操作系統維護在物理內存中,但是頁表的遍歷查詢是由TWU完成的,這樣減少對CPU資源的消耗。

虛擬內存及分頁機制的出現,解決了進程地址空間安全性的問題和內存使用效率低的問題,但是也引入了系統性能變差的問題。本來CPU可以直接通過訪存執行程序,但是現在引入了虛擬地址到物理地址的轉換。MMU硬件模塊的出現,就是為了解決這個性能問題。因此,幾G運行內存的電腦,可以并行運行幾十G的多程序,讓你在聽歌的同時,能夠并行處理編輯文檔,下載電影,收發郵件等。

2, 框架

2.1 內存管理體系結構

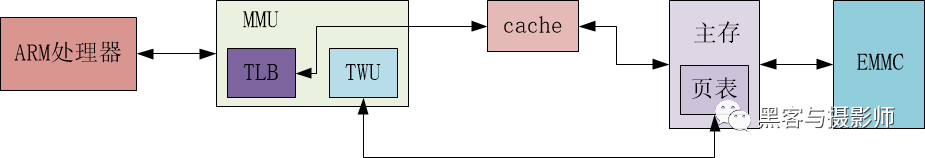

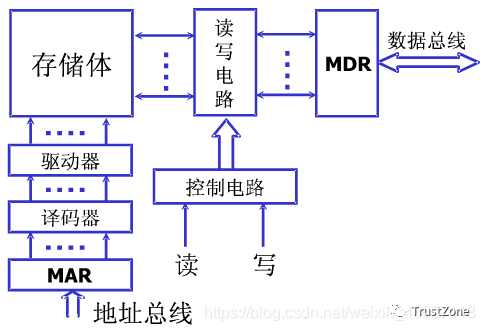

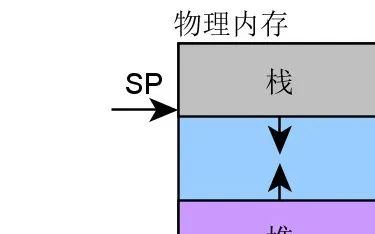

在SMP(Symmetric Multi Process,對稱多處理器)系統中,每個處理器內置了MMU模塊,MMU模塊包含了TLB和TWU兩個子模塊。TLB是一個高速緩存,用于緩存虛擬地址到物理地址的轉換結果。頁表的查詢過程是由TWU硬件自動完成的,但是頁表的維護是需要操作系統實現的,頁表存放在主存中。

頁表的查詢是一個耗時的過程,理想情況下,TLB命中,可以從中直接得到虛擬地址對應的物理地址。當TLB未命中的時候,MMU才會通過TWU查詢頁表,從而翻譯虛擬地址得到物理地址。得到物理地址后,首先要查詢該物理地址的內容是否存在于cache中,若cache命中,則直接取出物理地址對應的內容返回給處理器。

若cache沒有命中,會進一步訪問主存獲取相應的內容,然后回寫到cache,并返回給處理器。如果沒能在頁表中查詢到虛擬地址對應的物理地址,則會觸發一個與MMU相關的缺頁異常,在異常處理的過程中,會將EMMC中相關的數據加載到主存,然后建立相應的頁表,然后將物理地址對應的內容返回給cache及處理器。

2.2 MMU相關的基本概念

(1)虛擬地址相關基本概念

虛擬內存(Virtual Memory,VM):為每個進程提供了一致的、連續的、私有的內存空間,簡化了內存管理。將主存看成是一個存儲在磁盤上的地址空間的高速緩存,當運行多個進程或者一個進程需要更多的空間時,主存顯然是不夠用的,這時需要更大、更便宜的磁盤保存一部分數據。

虛擬地址空間(Virtual Address Space,VAS):每個進程獨有。

虛擬頁(Virtual Page,VP):把虛擬內存按照頁表大小進行劃分。

虛擬地址(Virtual Address,VA):處理器看到的地址。

虛擬頁號(Virtual Page Number,VPN):用于定位頁表的PTE。

(2)物理地址相關的基本概念

物理內存(Physical Memory,PM):主存上能夠使用的物理空間。

物理頁(Physical Page):把物理內存按照頁表的大小進行劃分。

物理地址(Physical Address,PA):物理內存劃分很多塊,通過物理內存進行定位。

物理頁號(Physical Page Number,PPN):定位物理內存中塊的位置。

(3)頁表相關的基本概念

頁表(Page Tabel):虛擬地址與物理地址映射表的集合。

頁表條目(Page Table Entry,PTE):虛擬地址與獨立地址具體對應的記錄。

頁全局目錄(Page Global Directory,PGD):多級頁表中的最高一級。

頁上級目錄(Page Upper Directory,PUD):多級頁表中的次高一級。

頁中間目錄(Page Middle Directory,PMD):多級頁表中的一級。

2.3 頁命中、缺頁

(1)頁命中

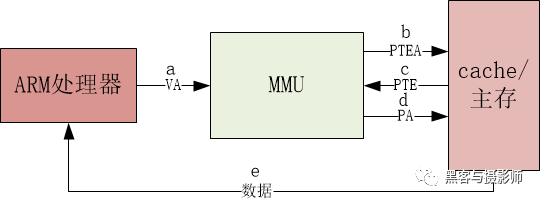

a) 處理器要對虛擬地址VA進行訪問。 b) MMU的TLB沒有命中,通過TWU遍歷主存頁表中的PTE地址。 c) 主存向MMU返回PTE。 d) MMU通過PTE映射物理地址,并把它傳給高速緩存或主存。 e) 高速緩存或主存返回物理地址對應的數據給處理器。

(2)缺頁

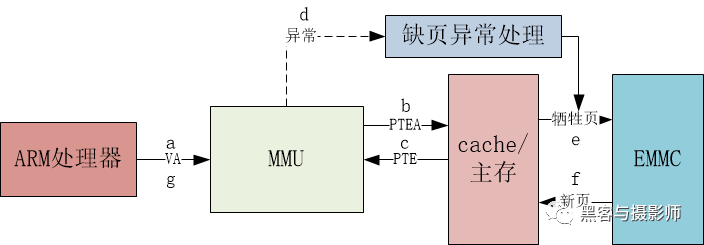

a) 處理器要對虛擬地址VA進行訪問。 b) MMU的TLB沒有命中,通過TWU遍歷主存頁表中的PTE地址。 c) 主存向MMU返回PTE。 d) PTE中有效位是0,MMU觸發一次異常,CPU相應缺頁異常,運行相應的處理程序。 e) 缺頁異常處理程序選出物理內存中的犧牲頁,若這個頁面已經被修改,將其換出到EMMC。 f) 缺頁異常處理程序從EMMC中加載新的頁面,并更新內存中頁表的PTE。 g) 缺頁異常處理程序返回到原來的進程,再次執行導致缺頁的指令。CPU將引起缺頁異常的虛擬地址重新發給MMU。由于虛擬頁面現在緩存在主從中,主存會將所請求的地址對應的內容返回給cache和處理器。

2.4 多級頁表映射過程

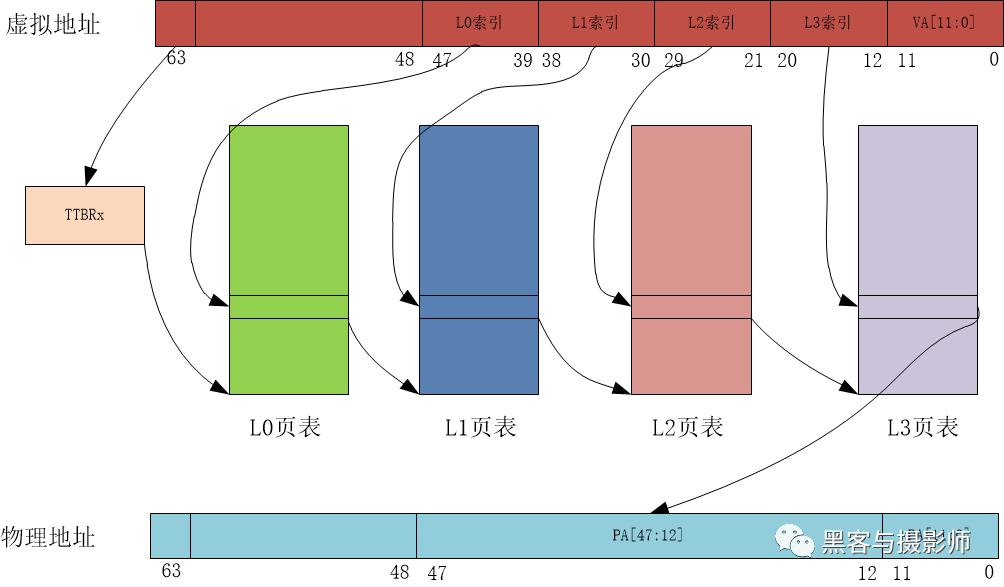

物理頁面大小一級地址總線寬度不同,頁表的級數也不同。以AArch64運行狀態,4KB大小物理頁面,48位地址寬度為例,頁表映射的查詢過程如圖:

對于多任務操作系統,每個用戶進程都擁有獨立的進程地址空間,也有相應的頁表負責虛擬地址到物理地址之間的轉換。MMU查詢的過程中,用戶進程的一級頁表的基址存放在TTBR0。操作系統的內核空間公用一塊地址空間,MMU查詢的過程中,內核空間的一級頁表基址存放在TTBR1。

當TLB未命中時,處理器查詢頁表的過程如下:

處理器根據虛擬地址第63位,來選擇使用TTBR0或者TTBR1。當VA[63]為0時,選擇TTBR0,TTBR中存放著L0頁表的基址。

處理器以VA[47:39]作為L0的索引,在L0頁表中查找頁表項,L0頁表有512個頁表項。

L0頁表的頁表項中存放著L1頁表的物理基址。處理器以VA[38:30]作為L1索引,在L1頁表中找到相應的頁表項,L1頁表中有512個頁表項。

L1頁表的頁表項中存放著L2頁表的物理基址。處理器以VA[29:21]作為L2索引,在L2頁表中找到相應的頁表項,L2頁表中有512個頁表項。

L2頁表的頁表項中存放著L3頁表的物理基址。處理器以VA[20:12]作為L1索引,在L3頁表中找到相應的頁表項,L3頁表中有512個頁表項。

L3頁表的頁表項里,存放著4KB頁面的物理基址,然后加上VA[11:0],這樣就構成了物理地址,至此處理器完成了一次虛擬地址到物理地址的查詢與翻譯的工作。

審核編輯:劉清

-

處理器

+關注

關注

68文章

19409瀏覽量

231207 -

ARM

+關注

關注

134文章

9169瀏覽量

369250 -

SMP

+關注

關注

0文章

76瀏覽量

19750 -

TLB電路

+關注

關注

0文章

9瀏覽量

5272 -

MMU

+關注

關注

0文章

91瀏覽量

18370

原文標題:一文搞懂MMU工作原理

文章出處:【微信號:IC大家談,微信公眾號:IC大家談】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

嵌入式中ARM的MMU和Cache機制

ARM920T的高速緩沖存儲器cache與MMU簡析

ARMv8 Uboot支持MMU和Cache對比實驗指南

Cache的工作原理

Buffer和Cache之間區別是什么?

cache結構與工作原理

ARM920T的MMU與Cache介紹

Cache工作原理講解 Cache寫入方式原理簡介

Cache工作原理是什么

MMU原理:CPU是如何訪問到內存的?

介紹CPU與cache之間的MMU的組成與工作原理

介紹CPU與cache之間的MMU的組成與工作原理

評論