簡介

在如今這個超級計算時代,需要新的計算架構、更快的加速能力,及更大的存儲容量,來滿足數據和帶寬的快速增長需求,這推動了整個市場的技術進步,并重塑片上系統 (SoC) 設計。隨著包括 DDR、PCIe、CXL、以太網、HDMI 和 DisplayPort 在內的高帶寬接口不斷普及和升級換代,所涉及的數據和系統的安全性也在不斷提高。而設備和云之間收集和移動的敏感信息及私有信息的增多,相關企業必須要加強數據的保護力度,并遵守最新的標準和法規。

無論是保護 HPC、移動、IoT 和汽車 SoC 領域的在途數據,還是靜態數據,為了能夠保持接口性能,同時降低對延遲和面積的影響,設計人員需要找到最佳的安全實施方法。

如今,安全在半導體行業處于重要位置,所有接口以及跨接口移動的數據都需要得到保護。畢竟,SoC 的安全性取決于其最薄弱的入口點。本文介紹了設計人員在當前萬物互聯時代可用于保護 SoC 的一些關鍵安全接口。

SoC 有許多需要安全保護的接口

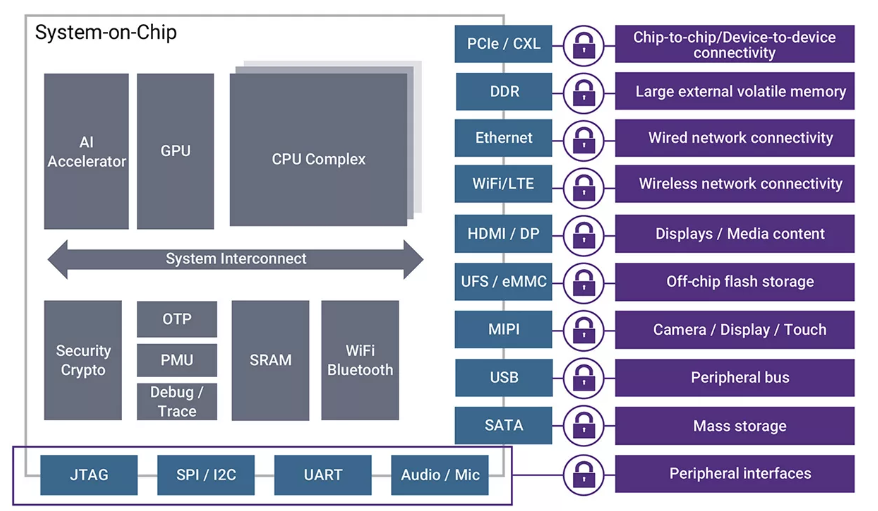

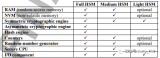

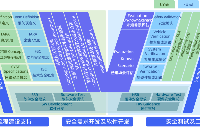

如圖 1 所示,SoC 中有許多接口需要安全保護,以防止數據被讀取/修改/重新排序/刪除、中間人攻擊以及惡意人員進行的其他攻擊。

圖 1:高級 SoC 結構圖

對于芯片間連接和設備間連接,PCIe 和 CXL 增加了完整性和數據加密 (IDE) 等安全要求,通過 AES-GCM 加密實現數據機密性、完整性和重放保護。DDR 和 LPDDDR 等內存接口依靠 AES-XTS 加密進行數據加密,以確保機密性。用于有線網絡連接的以太網現正普及到汽車行業,這種以太網依靠媒體訪問控制安全 (MACsec) 來實現機密性、完整性、來源真實性和重放保護。用于各種顯示器的 HDMI、DisplayPort 和 USB Type-C 接口需要最新版本的高帶寬數字內容保護 (HDCP v2.3),以便對優質音頻/視頻內容進行高級別保護;HDCP v2.3 不僅要求強加密,還要求更嚴格的安全機制,包括硬件信任根、強化的執行環境和運行時完整性檢查。eMMC 等片外閃存利用 AES-XTS 實現數據保密。此外,行業正在制定 MIPI 和 UCIe 等協議的新安全標準。

接口安全通常涉及兩個主要組件。其中一個組件用于身份驗證和密鑰管理,適用于控制平面;顧名思義,它負責處理身份驗證、密鑰創建和分發以及訪問控制等功能。這些功能需要在安全的環境中運行。另一個組件負責解決端點之間的批量完整性和數據加密問題。這與數據平面有關,數據平面需要解決方案來支持特定的接口帶寬,并要求在延遲、面積和功耗方面達到最佳水平。 以下各部分介紹了一些具有集成安全功能的關鍵接口。

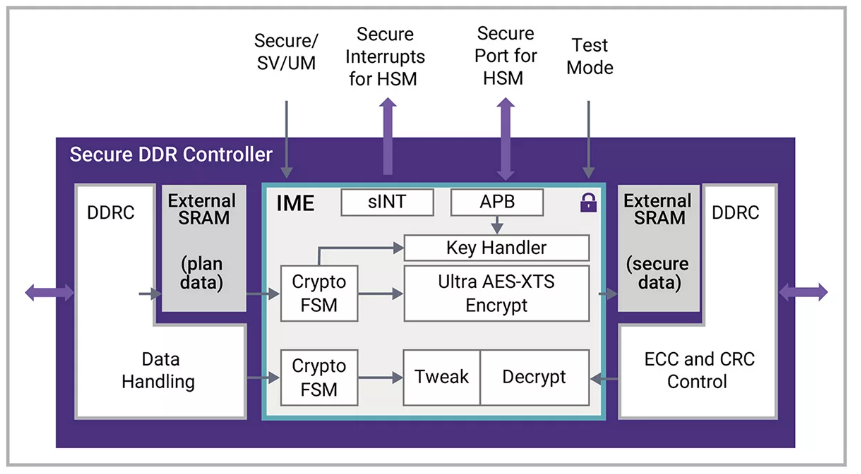

具有內嵌存儲加密 (IME) 功能的安全 DDR 控制器

內存和存儲安全旨在保護存儲資源和存儲在其中的數據,無論是在本地存儲,還是在外部數據中心和云中存儲。隨著對更高容量、更快訪問和加速處理的需求不斷增加,設計人員正在轉向高性能、低延遲的內存加密解決方案,以保持性能,同時保護最新一代 DDR、LPDDR、GDDR 和 HBM 內存接口上的數據。

AES-XTS(有時稱為 XTS-AES)是用于保護內存數據機密性的加密算法。它是一種基于標準的對稱算法,由 NIST SP800-38E 和 IEEE Std 1619-2018 規范定義,其算法屬性允許流水線架構從而使性能擴展到 Tbps 帶寬。CTS 模式為數據大小無法被底層 AES 密碼的 16 字節塊整除的數據單元提供支持。

存儲接口的最佳安全解決方案是內嵌式的,與相關的 DDR 控制器緊密集成,靠近 PHY 接口,在 DRAM 突發模式下工作。這種解決方案需要有效地處理各種密鑰大小的加密和解密,管理密鑰,并盡可能與內存控制器重疊執行任務,以進一步降低總體延遲。

新思科技安全 DDR/LPDDR 控制器具有集成 IME 安全功能(圖 2),可為讀/寫通道提供符合標準的獨立加密支持,確保數據機密性,實現每個區域加密/解密,且在面積、性能和延遲方面進行了高度優化。新思安全DDR/LPDDR 控制器的加密/解密延遲開銷低至 2 個時鐘周期。

通過集成新思科技安全 DDR/LPDDR 控制器,SoC 設計人員可以獲得以下優勢:

高性能、低延遲的安全內存接口,可高效地支持各種數據流量

讀寫通道獨立保護

基于符合標準的 AES-XTS 加密算法的加密/解密

支持 256 位和 512 位 AES-XTS 密鑰大小

超低延遲(低至 2 個周期)

每個區域加密/解密

每個周期一次 tweak 預計算

高效的密鑰設置和刷新

密鑰讀回保護/歸零

支持 FIPS 140-3 認證

旁路模式

圖 2:新思科技安全 DDR5 控制器 (DDRC) 模塊圖

具有完整性和數據加密 (IDE) 功能的安全 PCIe 和 CXL 控制器

IDE 為事務層數據包 (TLP) 和流量控制單元 (FLIT) 提供機密性、完整性和重放保護,確保線路上的數據不會被觀察、篡改、刪除、插入和重放。IDE 基于 NIST SP800-30D 標準定義的 AES-GCM 加密算法,具有 256 位密鑰和 96 位 MAC 標簽。

IDE 參考標準為:

PCI-SIG:PCIe 5.0 和 6.0 IDE ECN

PCIe 6.0 IDE 不僅支持更高帶寬,還增加了部分標頭加密和 FLIT 模式支持等新功能。最近發布的 TEE 設備接口安全協議 (TDISP) ECN 定義了系統中可信 I/O 虛擬化的架構要求,為 PCIe 控制器 + IDE 解決方案帶來了額外的要求,包括支持 T 位檢查和邊帶信號處理、每個數據包的額外數據包檢查、中斷、錯誤條件等。

CXL 2.0 和 3.0:用于 CXL.cache/mem 協議的 IDE。CXL.io 協議參考 PCIe 5.0 和 6.0 IDE ECN。

CXL 3.0 IDE 對 CXL.io 協議使用最新的 PCIe 6.0 IDE 功能,對于 CXL.cache/.mem 協議還能支持更多 FLIT 模式。

與安全內存控制器一樣,在尋找具有安全功能的 PCIe 和 CXL 解決方案時,重要的是要考慮優化,這些解決方案能夠提供最高性能、最低延遲和最佳面積,并支持適當的用例(根端口/端點/交換機端口、通道數量、數據總線寬度、IDE 流數量、支持的前綴數量等)。

借助與控制器集成的即插即用新思科技 PCIe 和 CXL IDE 安全模塊,設計人員可以獲得以下優勢:

符合持續更新的最新標準(PCIe 5.0/6.0.1、CXL 2.0/3.0)

接收和發送方向的全雙工最大化吞吐量

具有高度的可配置性,可根據特定用例調整解決方案

基于 256 位密鑰大小的 AES-GCM 加密算法,為 TLP 和 FLIT 提供高效的加密、解密和身份驗證

密碼和哈希算法的寬度可配置以滿足方案的面積和延遲優化

超低延遲(對于 CXL.cache/mem 協議,低至 0 個周期)

高效的動態密鑰刷新,實現系統中密鑰的無縫更改

針對無保護流量的低延遲順序旁路模式

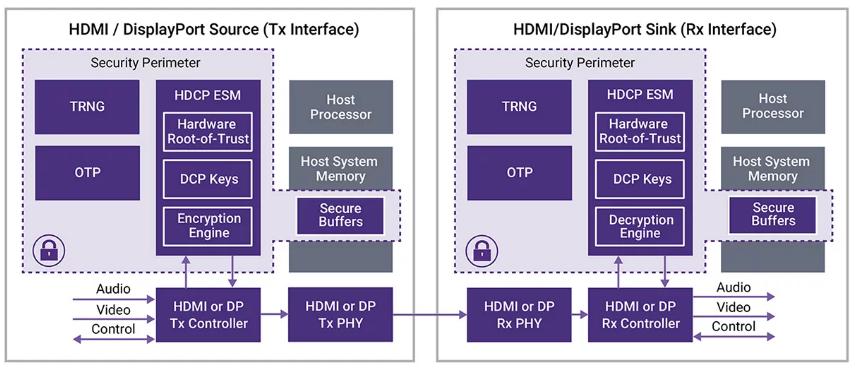

通過 HDCP 2.3 內容保護保護 HDMI 和顯示端口控制器

HDCP 是由英特爾開發,并獲得廣泛采用的鏈路安全規范,由 Digital Content Protection LLC (DCP) 授權,旨在保護在源設備(包括機頂盒或加密卡)與接收設備(例如數字電視)或其他顯示設備之間傳播的、有數字版權的音頻和視頻內容。HDMI 和 DisplayPort 接口的最新 HDCP 規范版本是 v2.3。在 2021 年 7 月,DCP LLC 發布了一份勘誤表,以更改需要更新的本地檢查協議,尤其是對于發送器相關應用。

新思科技HDCP 2.3 嵌入式安全模塊 (ESM) 是一個完整的安全解決方案,為設計人員在 HDMI 2.0/2.1、DisplayPort 1.4/2.0 和 USB Type-C 接口上實現 HDCP 內容保護提供強大、符合標準的技術支持。

HDCP ESM 包括身份驗證引擎和內容加密/解密引擎。強大的安全架構為 HDCP ESM 固件、DCP 密鑰管理和系統可更新性提供了硬件信任根、安全啟動和運行時篡改保護。

HDCP ESM 支持高清和超高清等高分辨率內容流的加密和解密,適用于眾多用例。產品系列包括單端口、雙端口和四端口解決方案。每個端口類型均可單獨配置為接收器 (Rx)、發送器 (Tx)、DisplayPort 1.4 或 2.0 單/多流 (SST/MST)、HDMI 2.0 或 2.1。多端口 ESM 還支持中繼器用例。例如,2 端口 ESM 可配置為支持 1 對 1 中繼器、DisplayPort 輸入至 DisplayPort 輸出、HDMI 輸入至 HDMI 輸出,或組合 HDMI 輸入至 DisplayPort 輸出、DisplayPort 輸入至 HDMI 輸出。

圖 3:新思科技HDCP 2.3 嵌入式安全模塊與控制器集成

當針對多端口用例進行配置時,HDCP ESM 包括單個身份驗證引擎,該引擎為內容加密/解密引擎中的多個端口提供服務,以實現最佳面積。每個內容端口單獨實例化加密內核,以支持 HDMI 2.0、HDMI 2.1、DisplayPort 1.4 和 DisplayPort 2.0 接口的最大傳輸速率。

結語

超級計算時代正在經歷重大變化,帶來了需要持續技術進步的新應用和功能。敏感數據呈指數級增長,而且法律、法規和不斷發展的標準要求對敏感數據的傳輸提供高級別保護,因此,安全問題成為了頭等大事。

高帶寬安全接口在 HPC、數據中心、汽車、IoT 和移動等市場日益普及。接口速度一代高于一代,加快了數據移動。安全解決方案需要高度優化,以支持相關接口的性能,并且需要盡可能降低對延遲、面積和功耗的影響。

新思科技為最廣泛使用的協議提供符合標準的完整安全接口解決方案,這些協議包括 DDR/LPDDR、PCIe、CXL、HDMI、DisplayPort、USB Type-C 和以太網。這些解決方案可滿足最具挑戰性的需求,使設計人員能夠快速在其 SoC 中實現所需的安全功能,降低風險并縮短上市時間。此外,新思科技還是 UCIe 和 MIPI 等標準組織的活躍成員,幫助開發在我們的控制器中進行集成所需的安全標準。

除了安全接口解決方案外,新思科技高度可配置的安全 IP 產品組合還包括具有信任根的硬件安全模塊、加密內核、真隨機數生成器和安全協議加速器,這些產品都可集成到 SoC 中。這些集成解決方案實現了許多安全標準的核心內容,支持機密性、數據完整性、用戶/系統身份驗證、不可否認性以及授權。新思科技的安全 IP 解決方案有助于防止連接的設備遭受各種威脅,例如盜竊、篡改、旁路通道攻擊、惡意軟件和數據泄露等。

審核編輯 :李倩

-

接口

+關注

關注

33文章

8706瀏覽量

151970 -

soc

+關注

關注

38文章

4208瀏覽量

219139 -

萬物互聯

+關注

關注

1文章

224瀏覽量

14172

原文標題:具有加密與驗證功能的超低延遲高帶寬安全接口解決方案

文章出處:【微信號:elecfans,微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

面向功能安全應用的汽車開源操作系統解決方案

CANFD芯片應用中關鍵功能和性能指標分析

TPD2S017具有串聯電阻器隔離功能的2通道、超低鉗位電壓ESD解決方案數據表

內網穿透延遲高怎么解決

基于 FPGA 的光纖混沌加密系統

E-Val Pro Plus有線驗證解決方案,功能升級,優化制藥流程,確保安全性和合規性!

具有可編程檢測和復位延遲功能的高電壓監控器TPS3760數據表

具有高級啟動功能的TPS2373高功率PoE PD接口數據表

美光科技開始量產HBM3E高帶寬內存解決方案

基于CMAC技術的安全啟動方案

具有加密與驗證功能的超低延遲高帶寬安全接口解決方案

具有加密與驗證功能的超低延遲高帶寬安全接口解決方案

評論