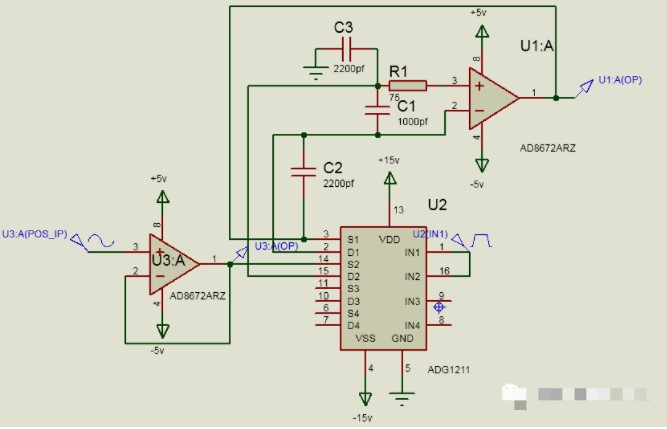

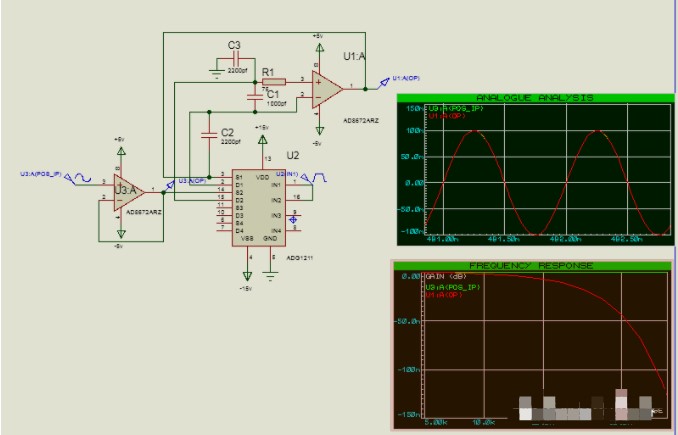

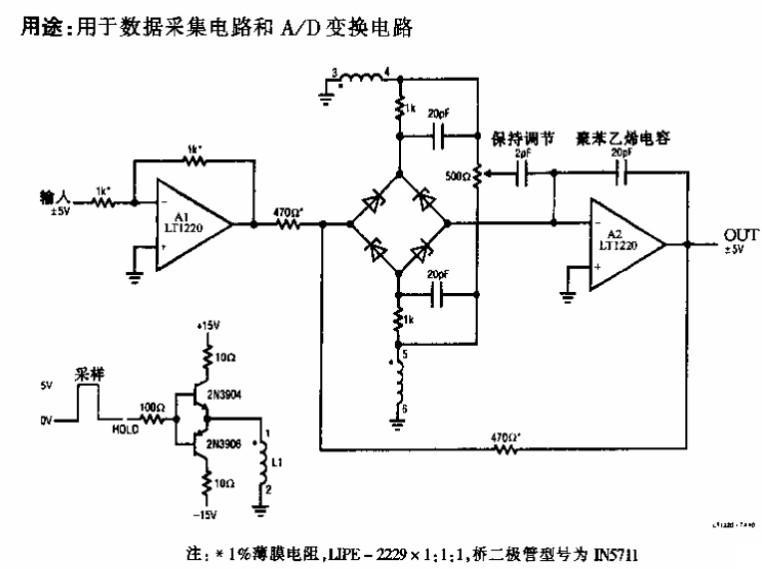

電路原理圖

在可編程邏輯控制器(PLC)輸出模塊中存在每通道采樣保持架構,它采用開關電容和緩沖器作為采樣保持放大器(SHA),以便存儲單通道高性能DAC的選定輸出樣本。這些樣本通過-一個模擬開關或多路復用器在不同保持電容之間切換。

開關和多路復用器在必須獲取瞬時模擬值的數據采集應用中很有用。模擬開關的輸人信號向-一個與運算放大器輸人相連的保持電容充電。理想情況下,閉合開關僅向電容傳送輸人信號。但在實際應用中,該開關也會傳送-一個電荷包,稱為電荷注人。ADG1211具有業界領先的1pC電荷注人性能,而市場上現有解決方案的電荷注人性能為10pC至20pC。ADG1211還具有出色的電容與泄漏性能,因而它是此電路的理想選擇。

電路功能

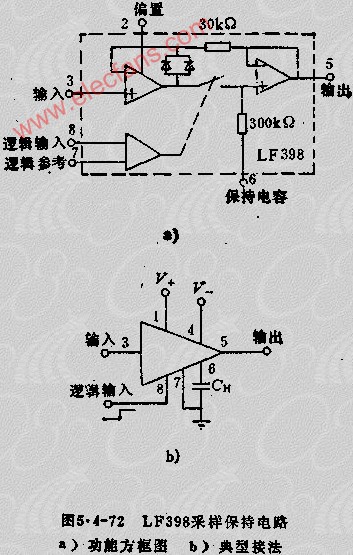

該電路是-個精密、快速的采樣保持電路。在采樣模式下,SW2閉合,輸出Vour跟隨輸人信號Vn。在保持模式下,SW2斷開,信號由保持電容CH保持。由于開關和電容泄漏影響,保持電容上的電壓會隨著時間而下降。ADG1211具有低泄漏特性,能使這種電壓下降最小。在25°C時,ADG1211的典型泄漏電流為20pA,最大泄漏電流為100pA。采用聚苯乙烯保持電容還可進--步使下降率更低。此電路還有另-一個開關SW1,它與SW2并聯工作,用來降低基底誤差。由于兩個開關處于相同電位,因此對運算放大器的輸出均具有差分效應,從而使電荷注入影響最小。補償網絡Rc和Cc也可降低基底誤差。該補償網絡還可減小保持時間尖峰,同時優化采集時間。利用上述電路可得到如下結果:下降率為2 mV/ms,基底誤差低于0.5 mV ,采集時間為3ms。

-

運算放大器

+關注

關注

217文章

5697瀏覽量

176343 -

電路原理圖

+關注

關注

40文章

352瀏覽量

39040 -

dac

+關注

關注

43文章

2397瀏覽量

193383 -

采樣保持電路

+關注

關注

3文章

13瀏覽量

20200 -

ADG1211

+關注

關注

0文章

5瀏覽量

1250

發布評論請先 登錄

【每天看電路第77期】采樣保持電路

ADG1211/ADG1212/ADG1213,pdf da

ADG1211_ADG1212_ADG1213 datasheet

低電容低電荷注入的CMOS四路SPST開關ADG1211/ADG1212/ADG1213數據表

ADG1211 低電容、低電荷注入、±15 V/+12 V iCMOS、四通道單刀單擲開關

ADG1211/ADG1212/ADG1213:低電容、低電荷注入、±15 V/+12 V<em>I</em>CMOS;四路SPST開關數據表

ADG1211開關實現采樣保持電路

ADG1211開關實現采樣保持電路

評論