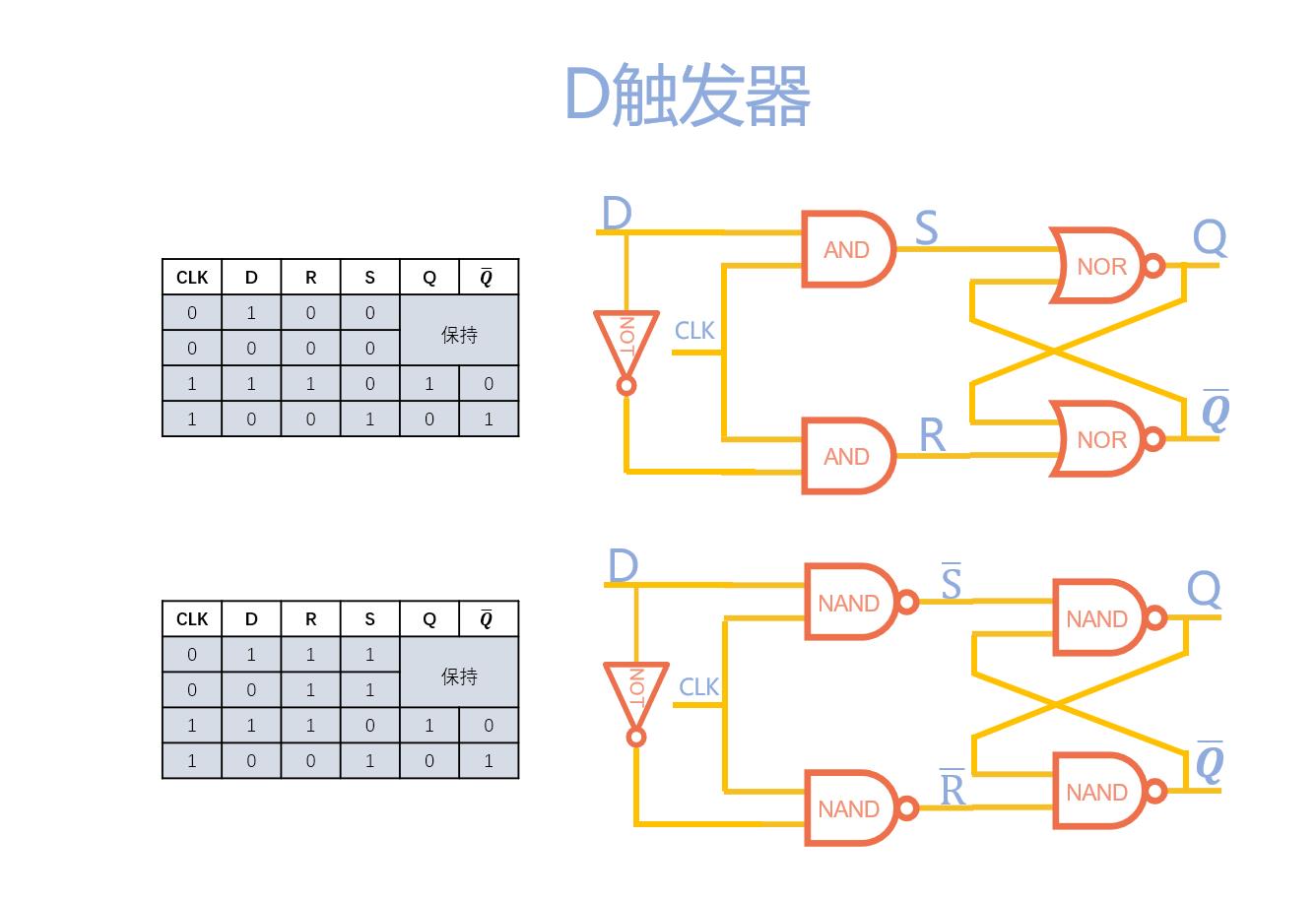

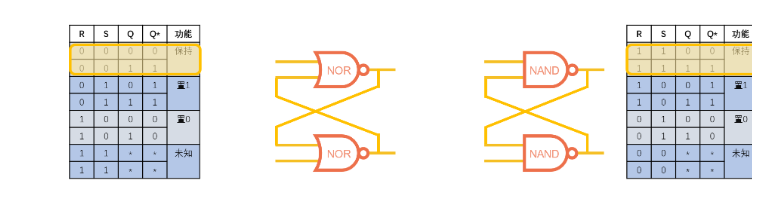

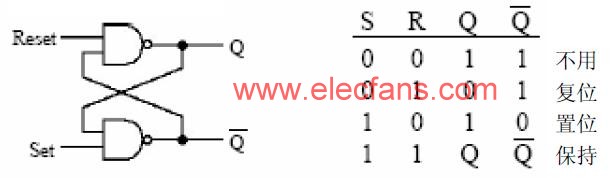

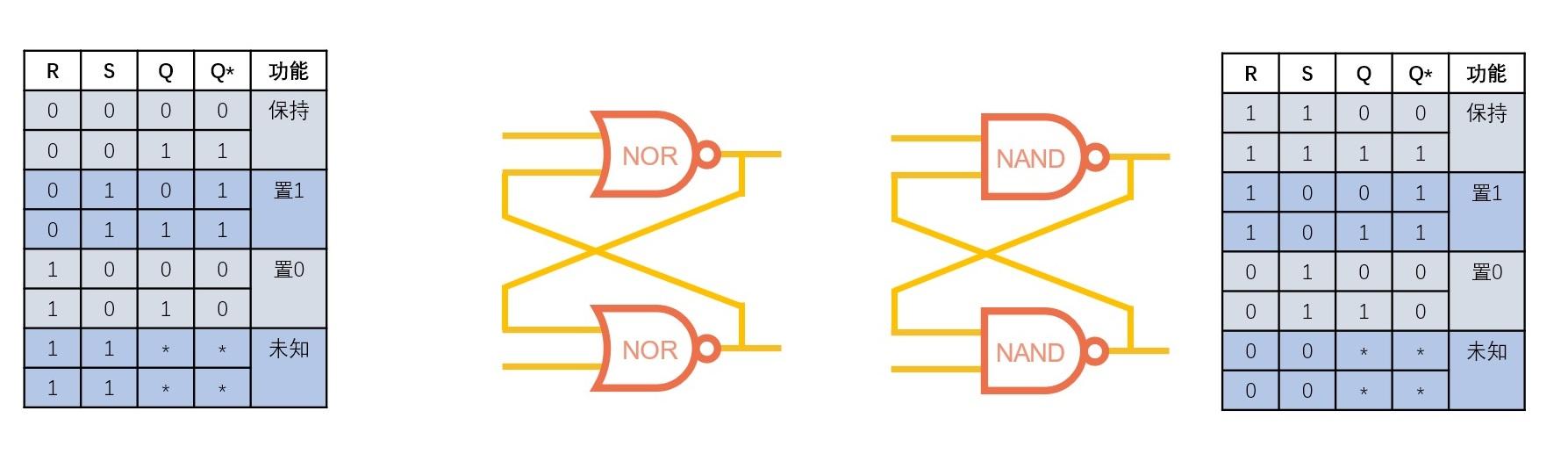

大家好,上次我們研究了D觸發器,今天我們繼續研究。在開始之前,先來做一點刪減,之前我們討論了用或非門或者與非門實現觸發器的方法,在功能上兩種實現方法完全相同,在輸入輸出和實現上略微有些差異。

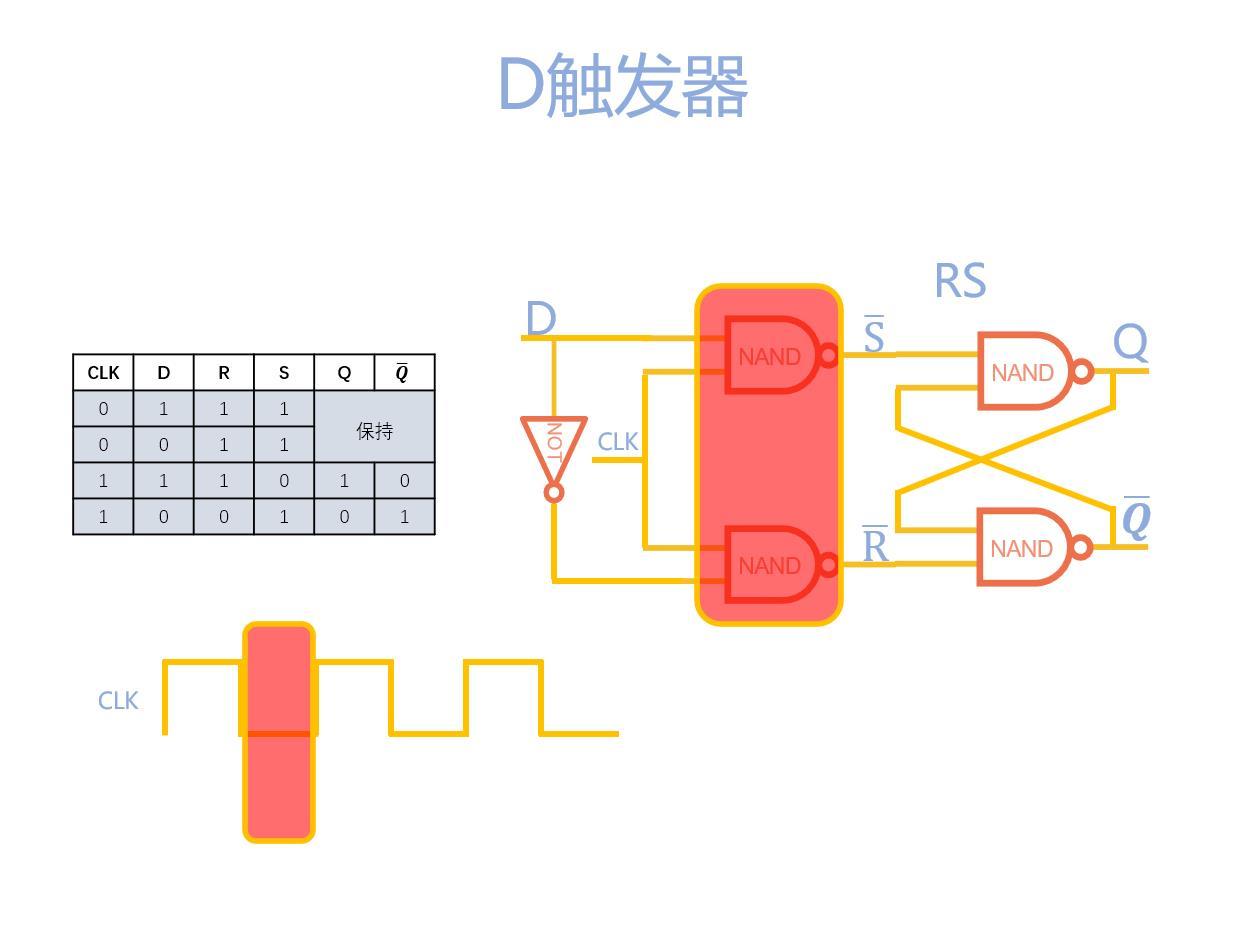

D觸發器

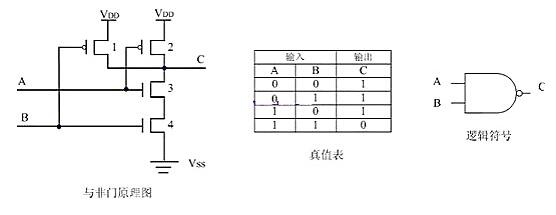

二輸入與非門或或非門用CMOS電路實現需要2個NMOS和2個PMOS,總共4個MOS管,用NMOS電路實現需要2個NMOS。

而二輸入與門用CMOS電路實現需要3個NMOS和3個PMOS,總共6個MOS管,用NMOS電路實現需要3個NMOS。

這樣一套下來,選擇與非門電路,可以只使用一種邏輯門,電路實現更加一致,還可以減少MOS管使用的數量。

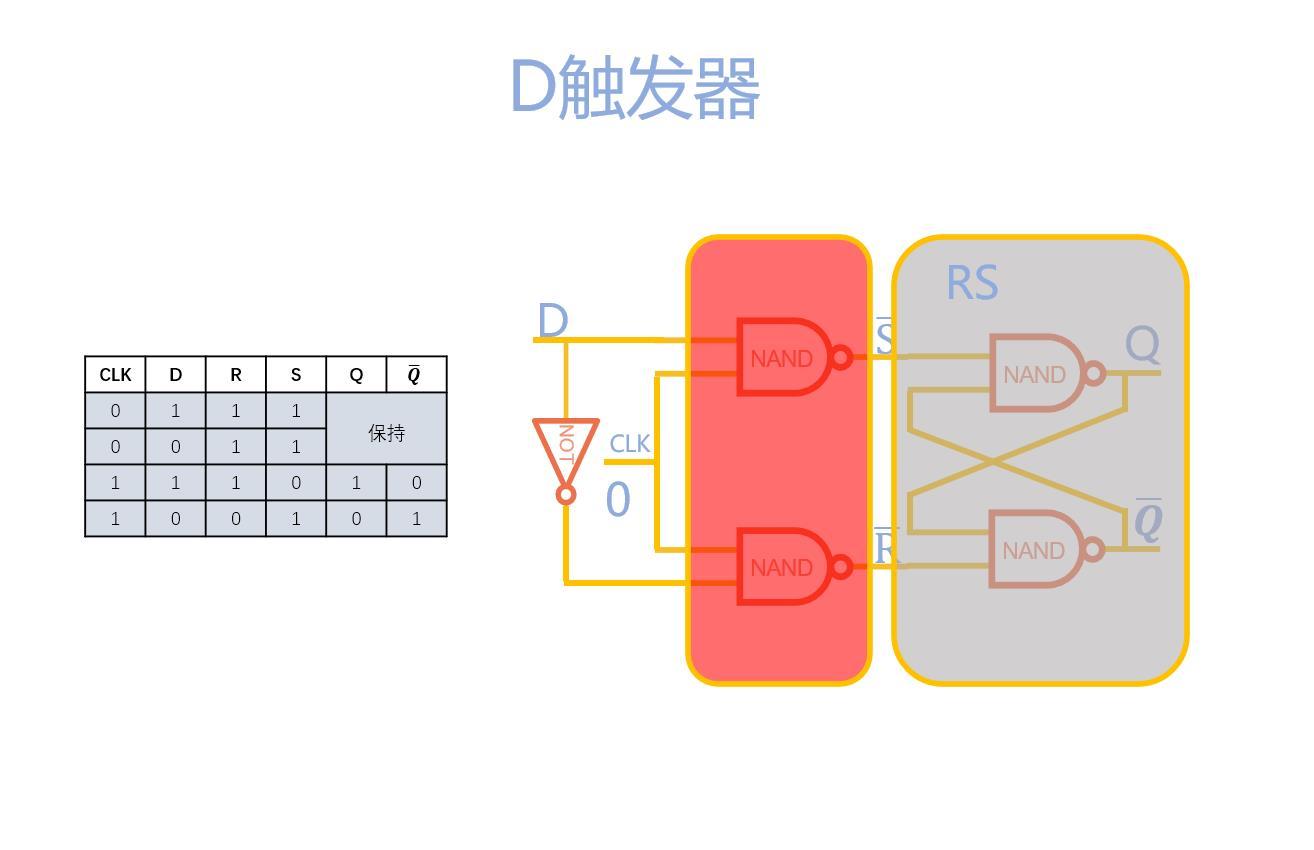

現在我們來看這個觸發器和他的真值表

我們可以看到,當CLK控制信號輸入為0時,D的信號是無法通過兩個(與非門)組成的屏障,因此屏障之后的RS觸發器的狀態不會發生改變

輸入信號D就被忽視掉了。

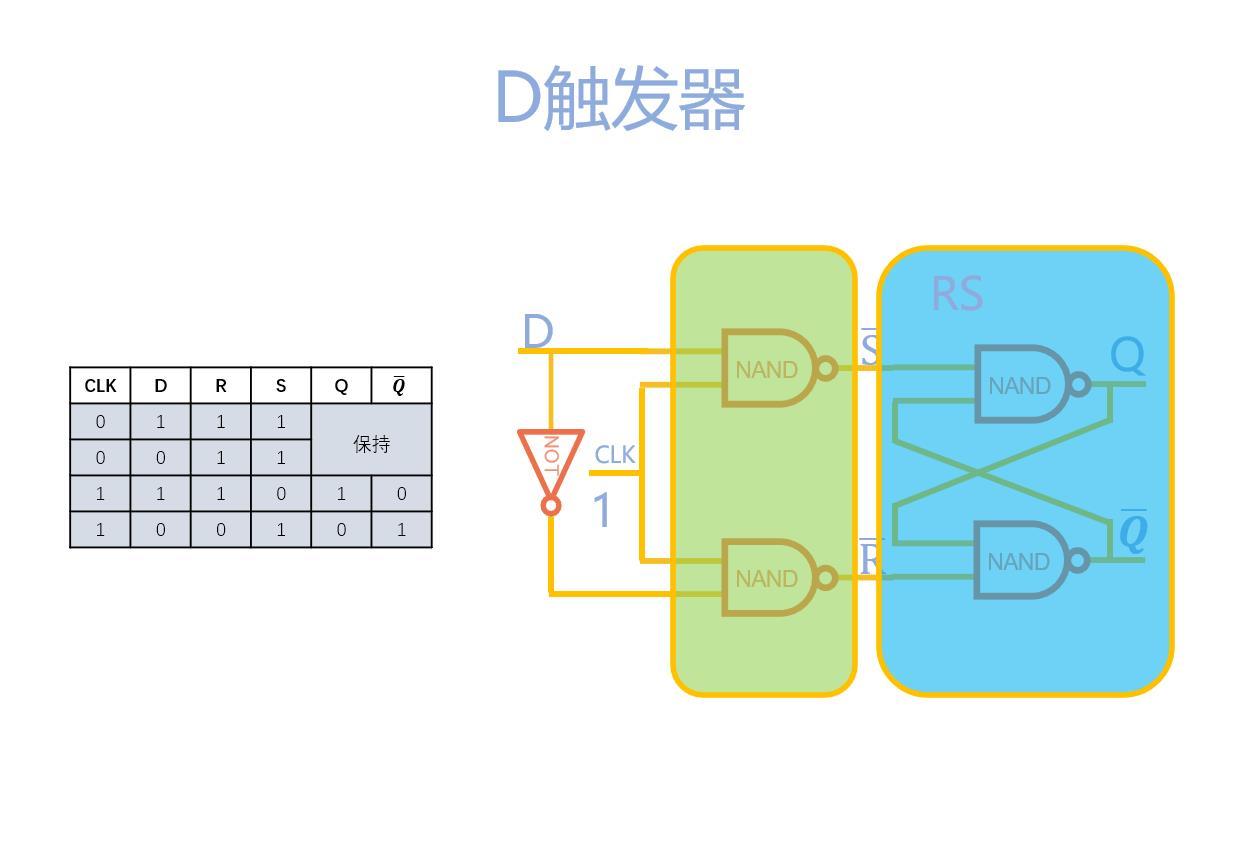

再來看,當CLK控制信號輸入為1時,(與非門)屏障被打開了,輸入信號D可以通過屏障直接改變RS觸發器的狀態

我們把一個時鐘信號作為CLK的輸入

那么,D的輸入信號,在時鐘處于高電平是有效的,低電平時,D的輸入則被無視。

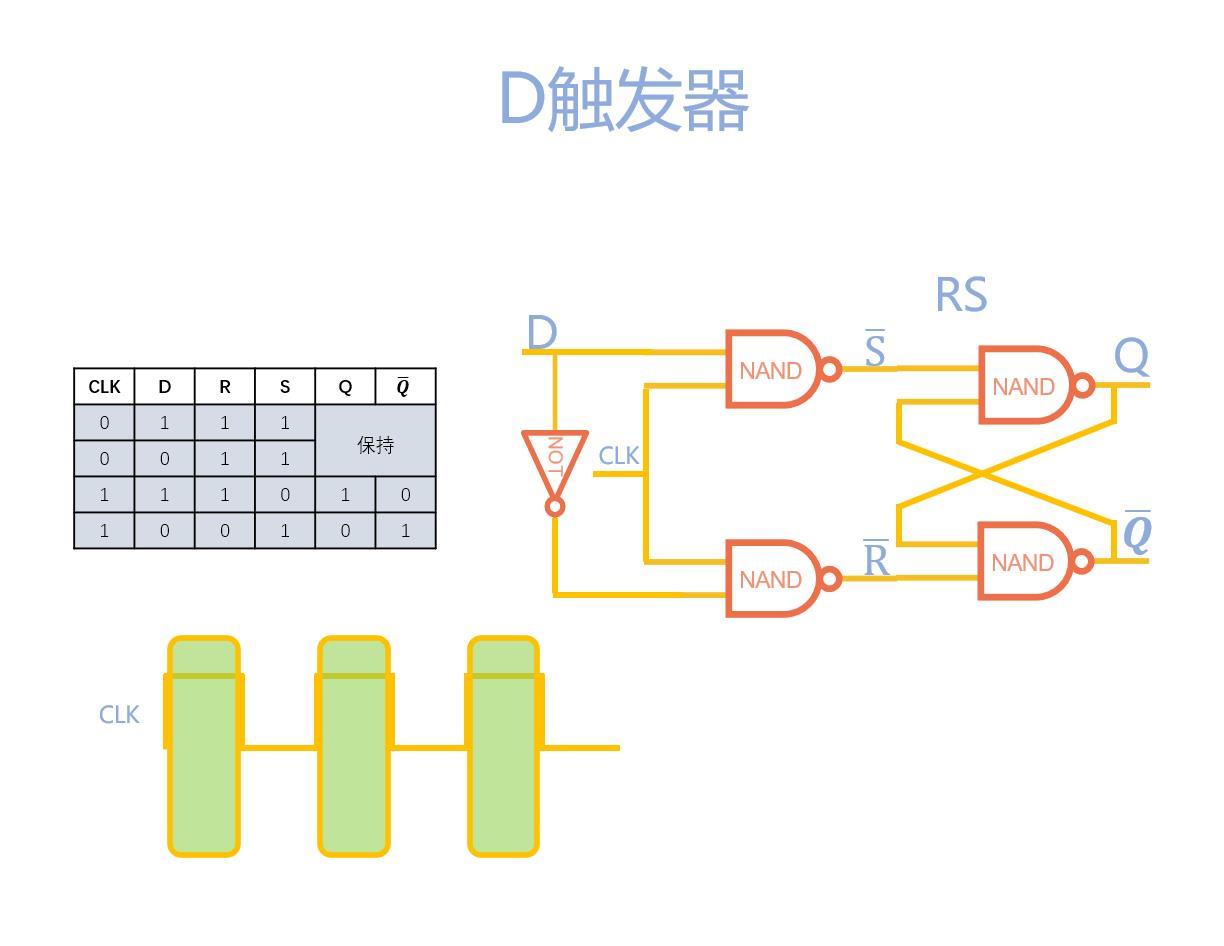

我們把這種在一種電平狀態中持續有效或無效的觸發器叫做(電平觸發D觸發器。)

對一個電平觸發D觸發器來說,當CLK為高電平時,D的輸入會忠實的反饋在輸出Q和Q!上,即便是D信號上的噪聲也一樣會被輸出到Q。大門打開的時間太長了,房子里的RS觸發器很沒有安全感。

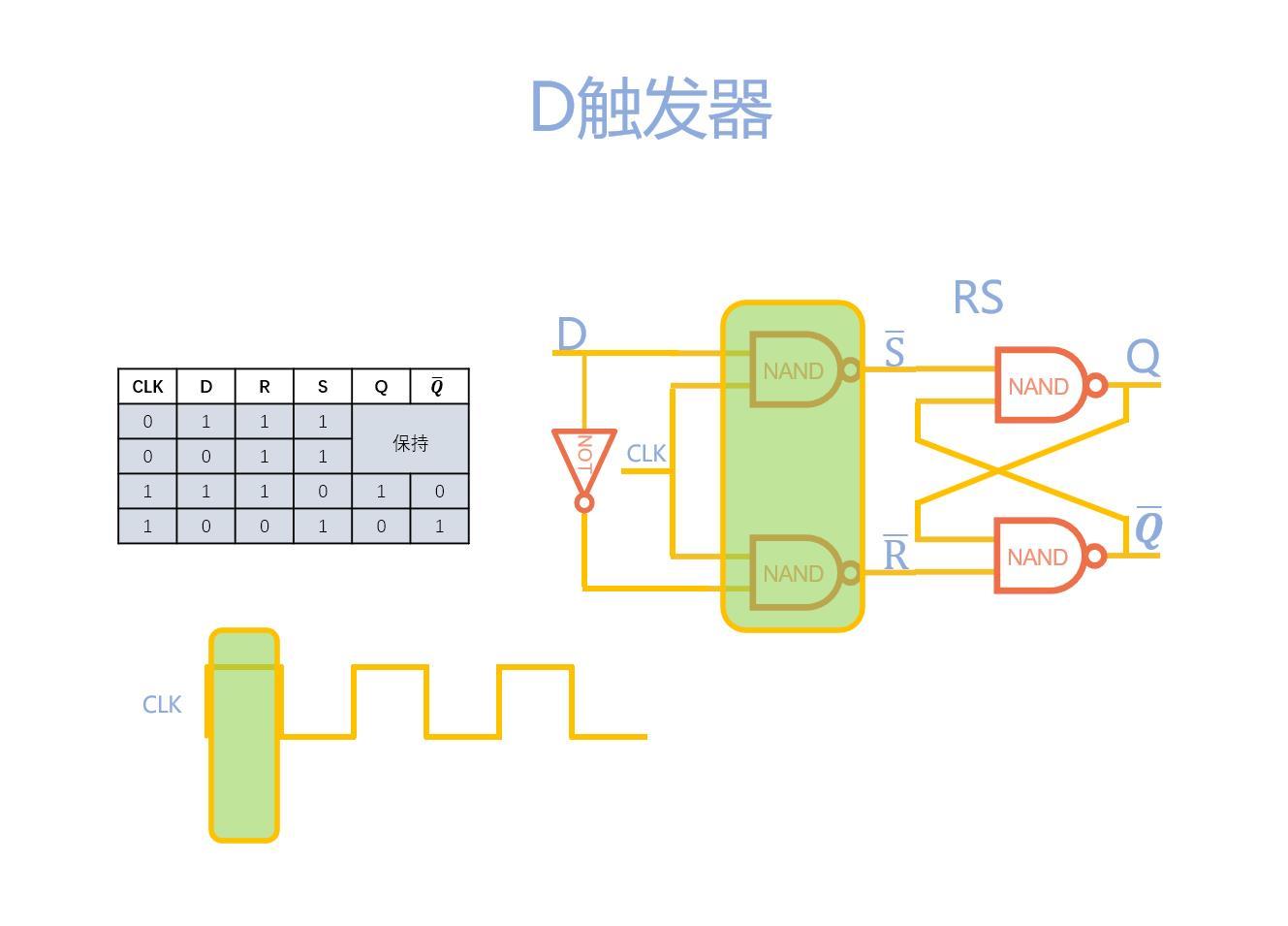

接下來就回到我們今天的主題,怎么讓大門開的時間短一點,減少壞人進來的風險。

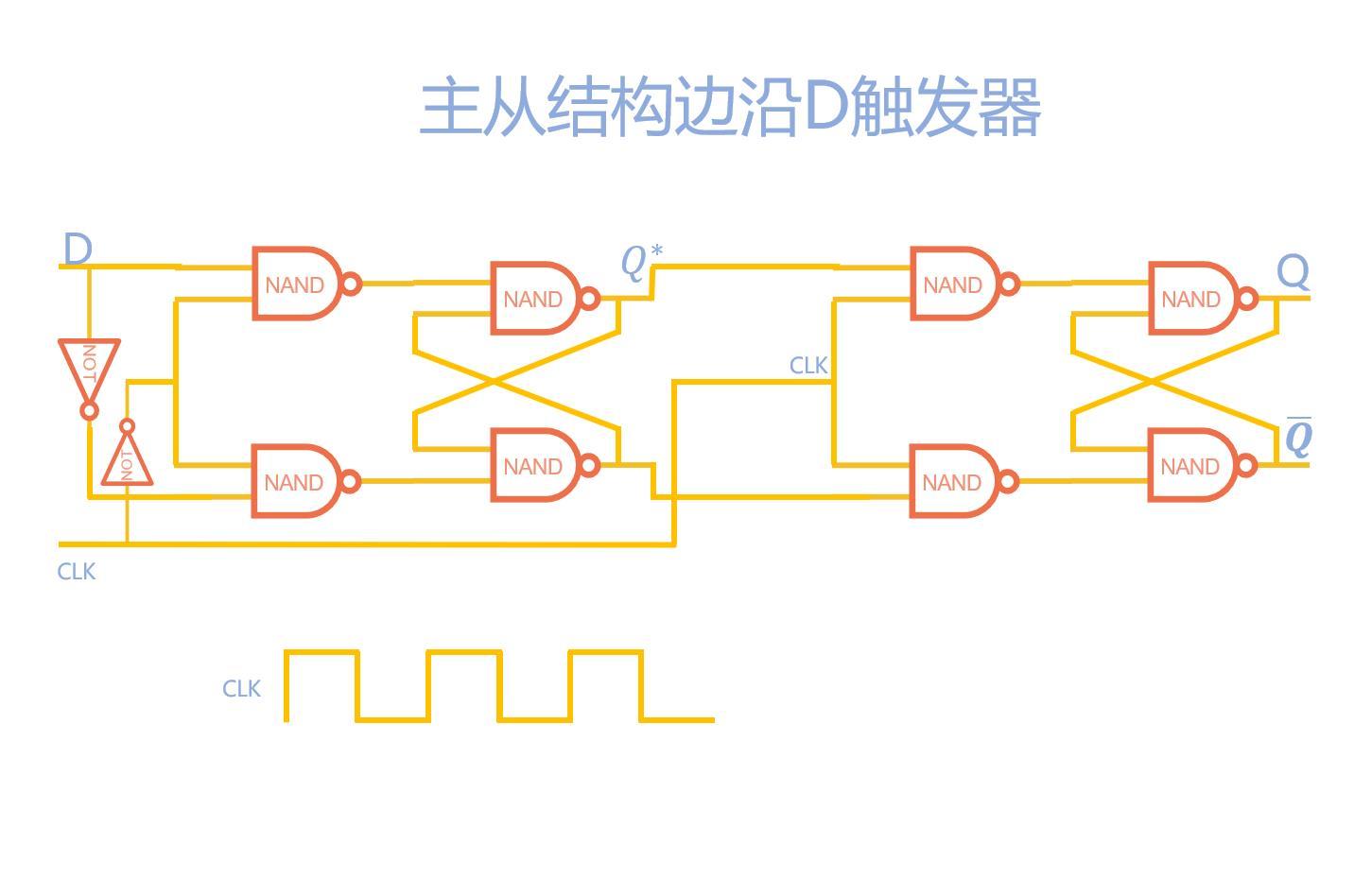

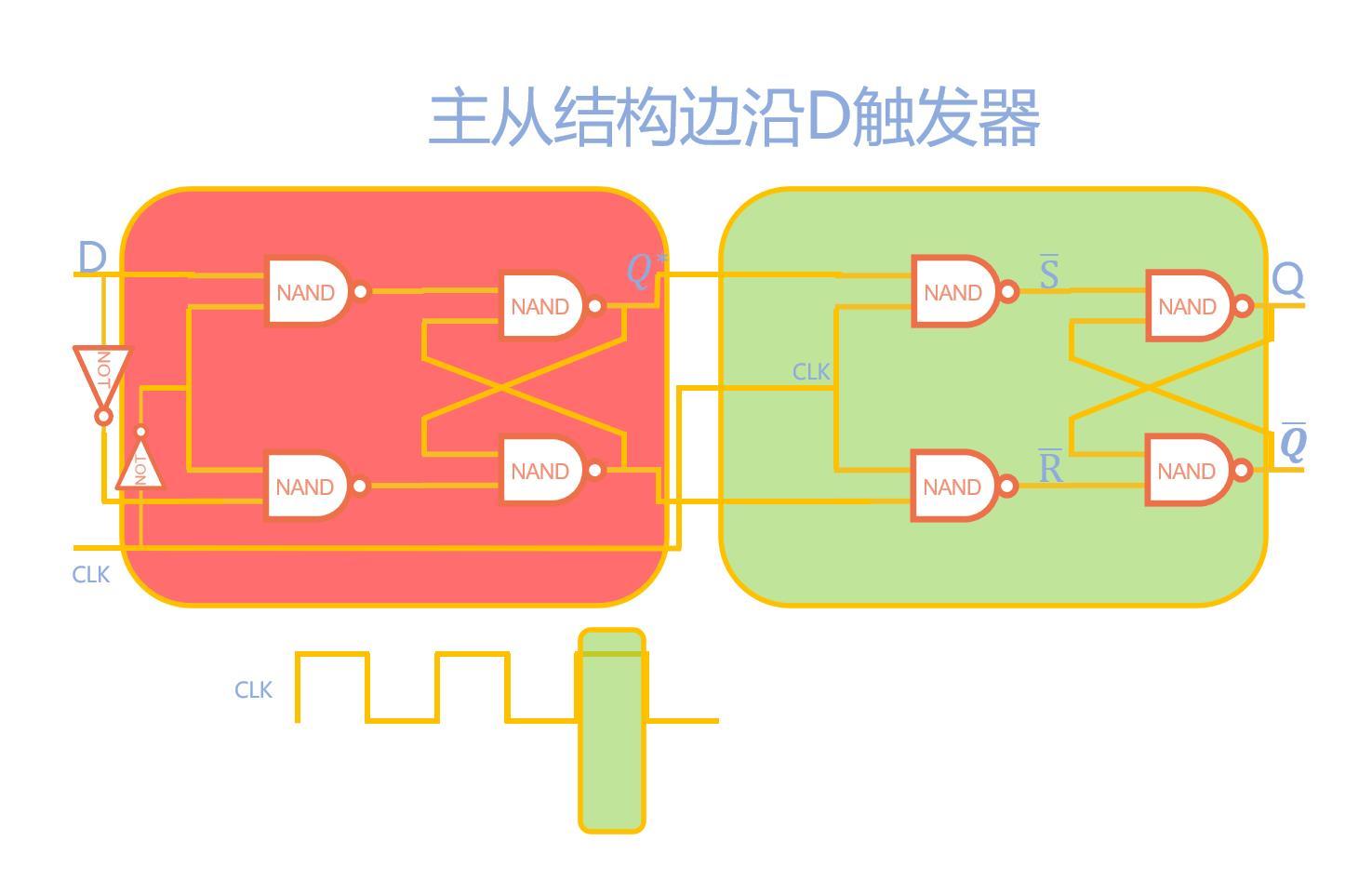

真值表和非門先拿走,再復制一個觸發器出來。

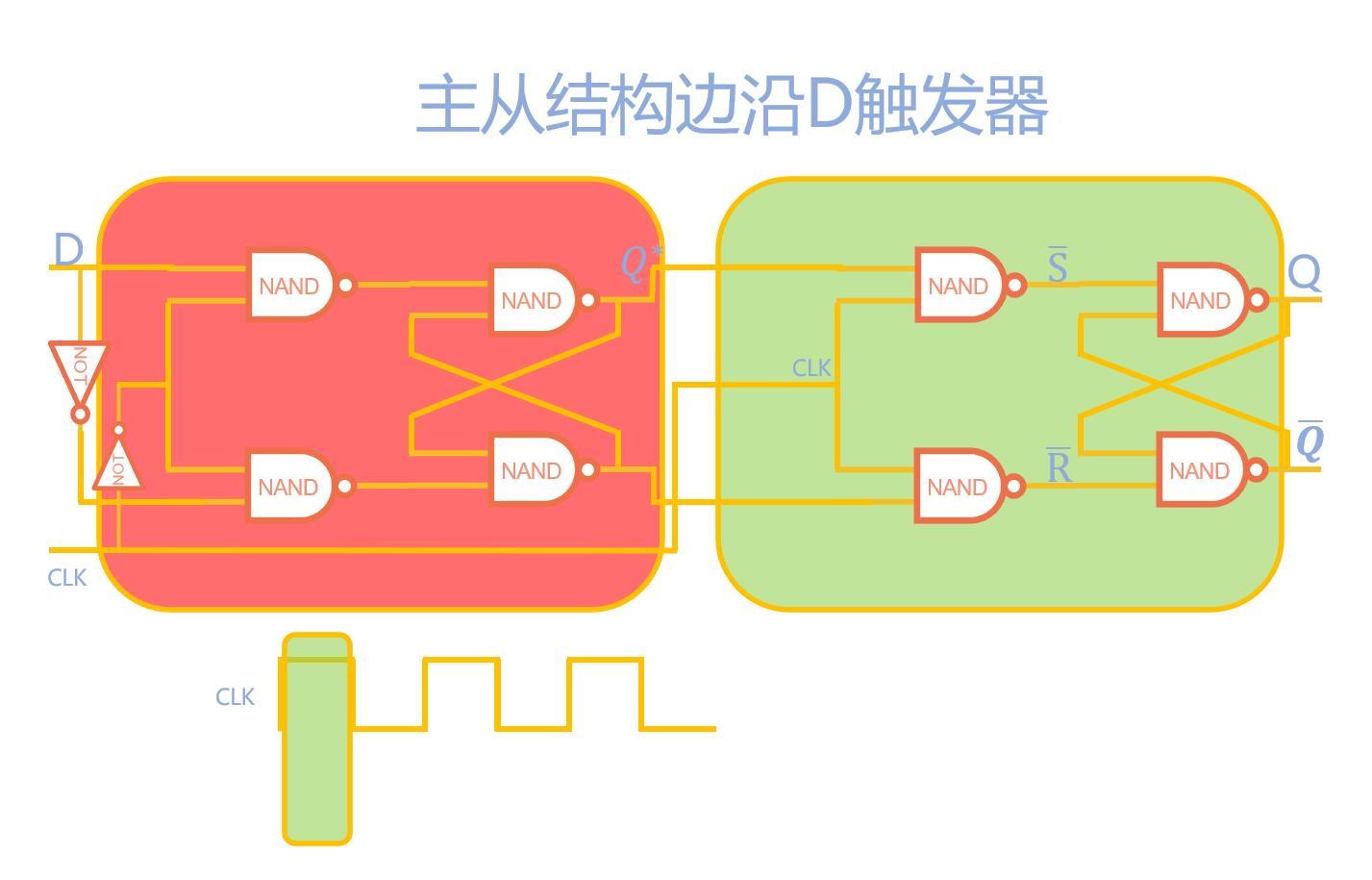

把左邊觸發器的輸出和右邊觸發器的輸入相連,再在兩個觸發器的CLK之間接入一個非門。再把原先觸發器D上的非門還回來。

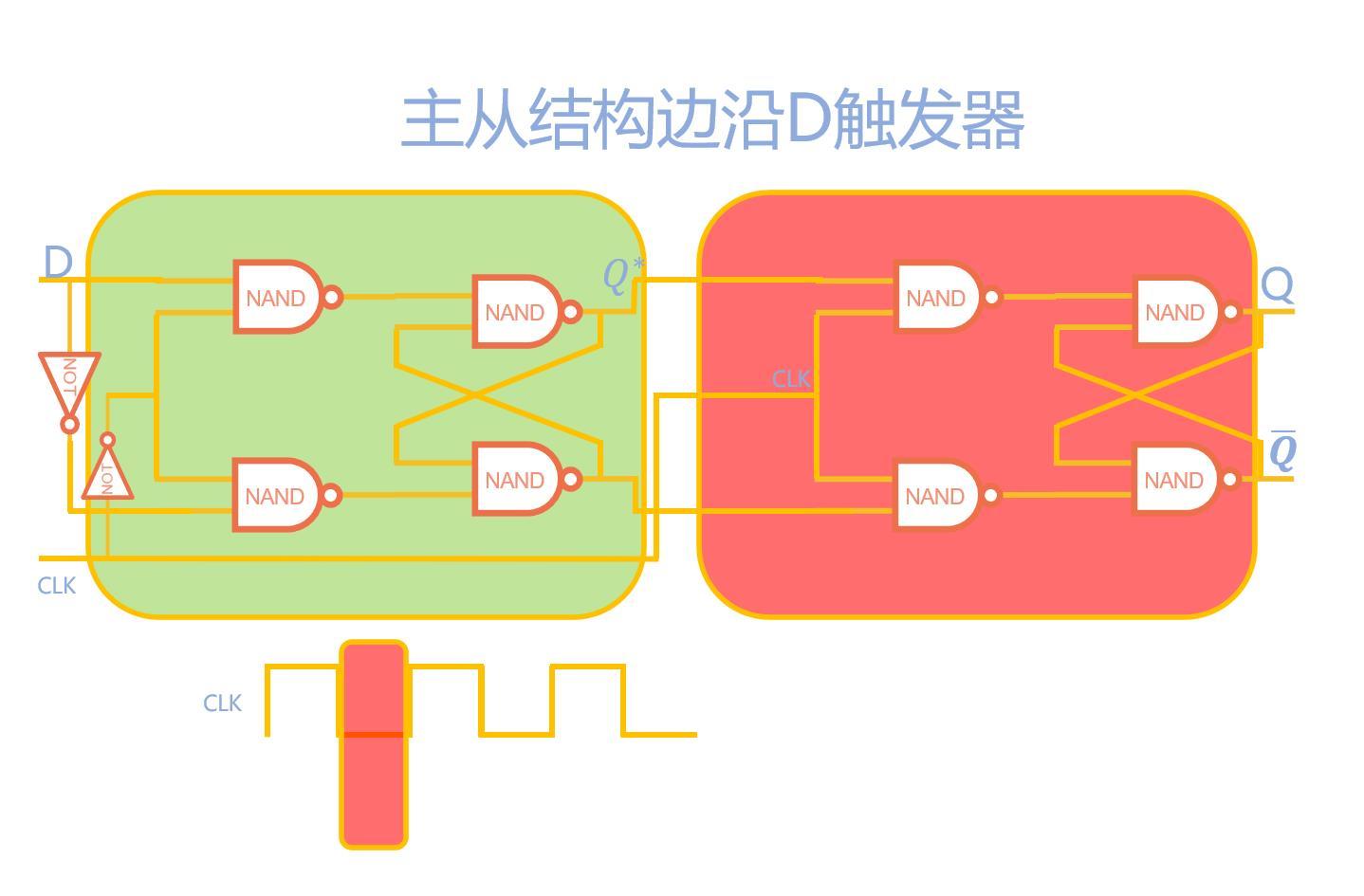

這樣,一個主從結構的D觸發器就做好了。我們叫這個觸發器為 (主從邊沿D觸發器)

我們來看一下這個觸發器的工作狀態。

我們把左邊的觸發器叫主觸發器,右邊的觸發器叫從觸發器

首先當第一個時鐘高電平周期到來的時候,主觸發器是關閉的,輸入D進入主觸發器,然而這時的觸發器輸出Q*的值,可能是0,也可能是1。這個值由主觸發器的初始值決定。

這個不確定的主Q*值會被傳遞到從觸發器,因為這時的從觸發器大門是打開的。

Q的輸出也不確定

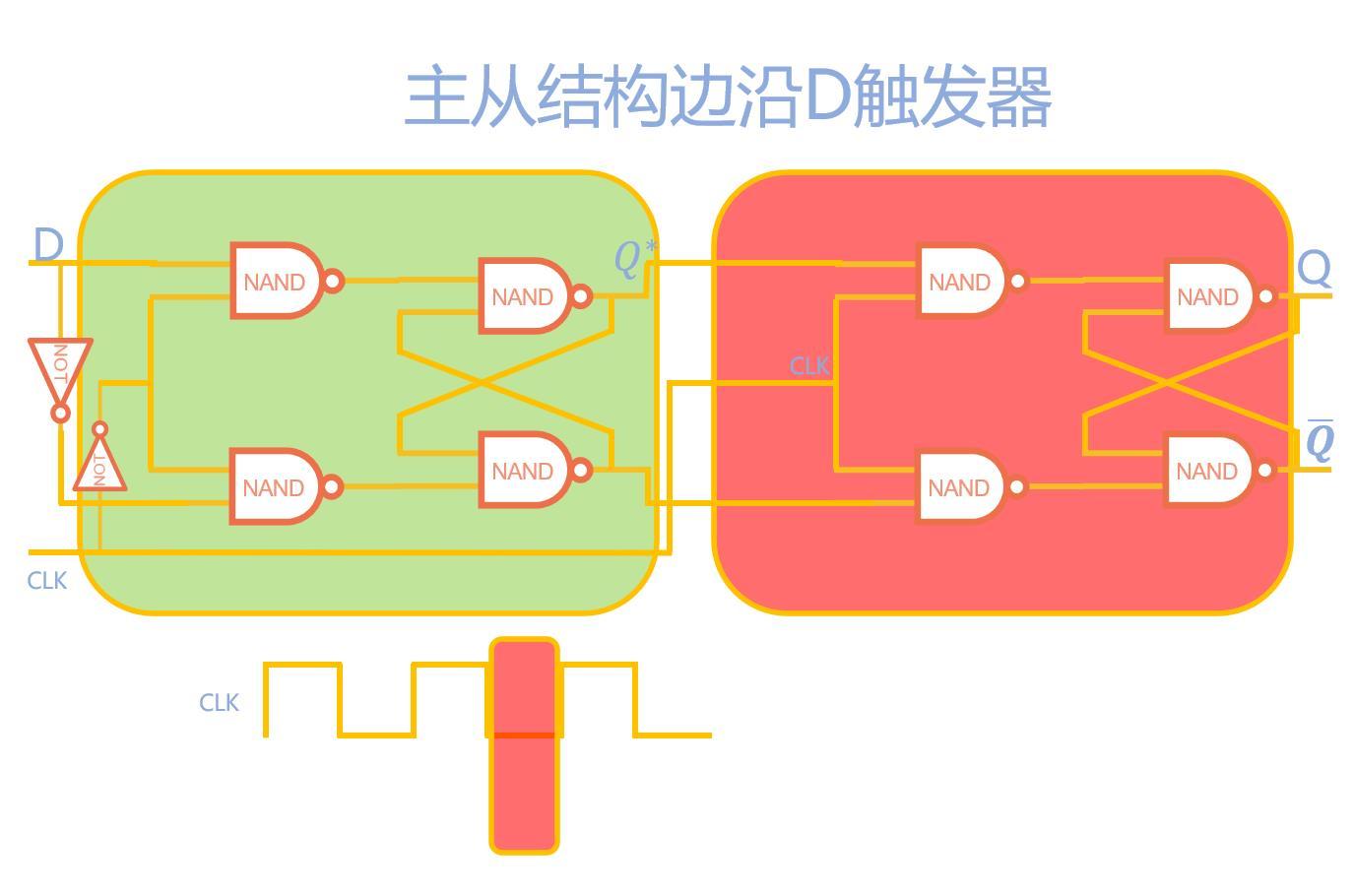

接下來,時鐘進入底電平周期,主觸發器大門打開,從觸發器大門關閉,D傳遞到Q*,但此時Q輸出沒有變化,因為從觸發器處于關閉狀態。

又到了下一個高電平周期,這里要注意,當CLK信號從低電平向高電平反轉的這一刻,輸出Q的狀態變成Q*的狀態,而且由于主觸發器此時處于關閉狀態,D的任何變化都影響不到Q的輸出。并且從這一刻開始Q的輸出是穩定的輸出。

繼續往下走,主改變,從不改變,Q輸出不變

好,再往下,主不變,從改變。

通過上面的分析,我們可以得出2個結論

第一個、主從觸發器輸出狀態的改變,只發生在控制信號發生轉變的時刻,在我們這個圖里,是發生在時鐘上升沿的時候。我們也可以移動兩個觸發器CLK之間的非門,讓他變成只在下降沿響應。

第二個、主從結構的邊沿觸發器,啟動有一個時鐘周期的延遲。從第二個時鐘周期才開始有穩定的輸出。

-

CMOS

+關注

關注

58文章

5993瀏覽量

238088 -

或非門

+關注

關注

0文章

33瀏覽量

15528 -

D觸發器

+關注

關注

3文章

165瀏覽量

48529 -

觸發器

+關注

關注

14文章

2032瀏覽量

61880 -

與非門

+關注

關注

1文章

129瀏覽量

13047

發布評論請先 登錄

求助,關于D觸發器SN74LVC1G374與與非門SN74AUP1G00組合問題求解

搭D觸發器時,反相器與后面的與非門相接點問題

MOS與非門或非門構成原理

RS觸發器是什么?解讀rs觸發器的作用和數字電路中的rs觸發器的作用

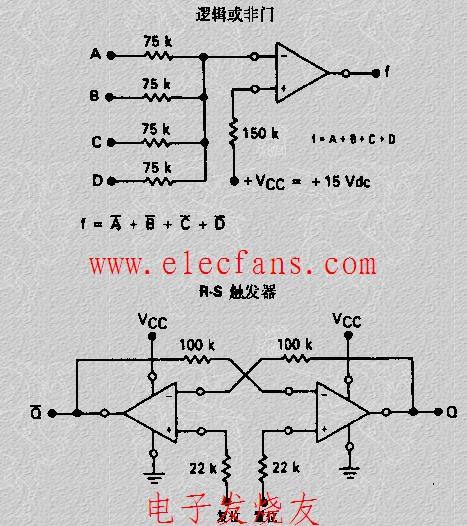

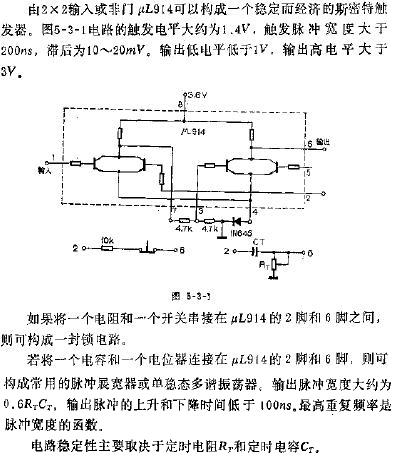

使用或非門和與非門實現觸發器

使用或非門和與非門實現觸發器

評論