在如今不斷小型化的電子設(shè)計領(lǐng)域,具有極精細節(jié)距特征的BGA部件越來越受歡迎。隨著這些細節(jié)距BGA復(fù)雜性和用戶I/O(焊料球數(shù)量)的不斷增加,尋找逃逸布線和扇出模式的難度也在逐步增加。

此外,隨著硅幾何尺寸的縮小,通道長度會更小,導(dǎo)致了信號完整性問題增加,需要重新探究和/或調(diào)整一些傳統(tǒng)的BGA逃逸布線方法,不僅能夠使BGA設(shè)計的I/O成功扇出,而且能夠使BGA設(shè)計的電路成功運行。

過去可以使用傳統(tǒng)的全貫穿通孔結(jié)構(gòu)布線BGA,采用離開BGA焊盤的狗骨狀走線。這些BGA的節(jié)距通常為1.27 mm,且焊盤之間有足夠的間隙,可以在不違反任何設(shè)計規(guī)則的情況下放置3級產(chǎn)品要求的A級通孔。此外這些封裝的特征尺寸可用1盎司銅制造,不會產(chǎn)生任何問題。

隨著芯片復(fù)雜度和I/O密度的增加,目前大多數(shù)BGA封裝的節(jié)距都在1 mm以下,有些封裝的節(jié)距甚至小到0.4 mm。由于這些更精細節(jié)距的BGA封裝,無法在BGA下使用傳統(tǒng)的全貫穿通孔結(jié)構(gòu)。

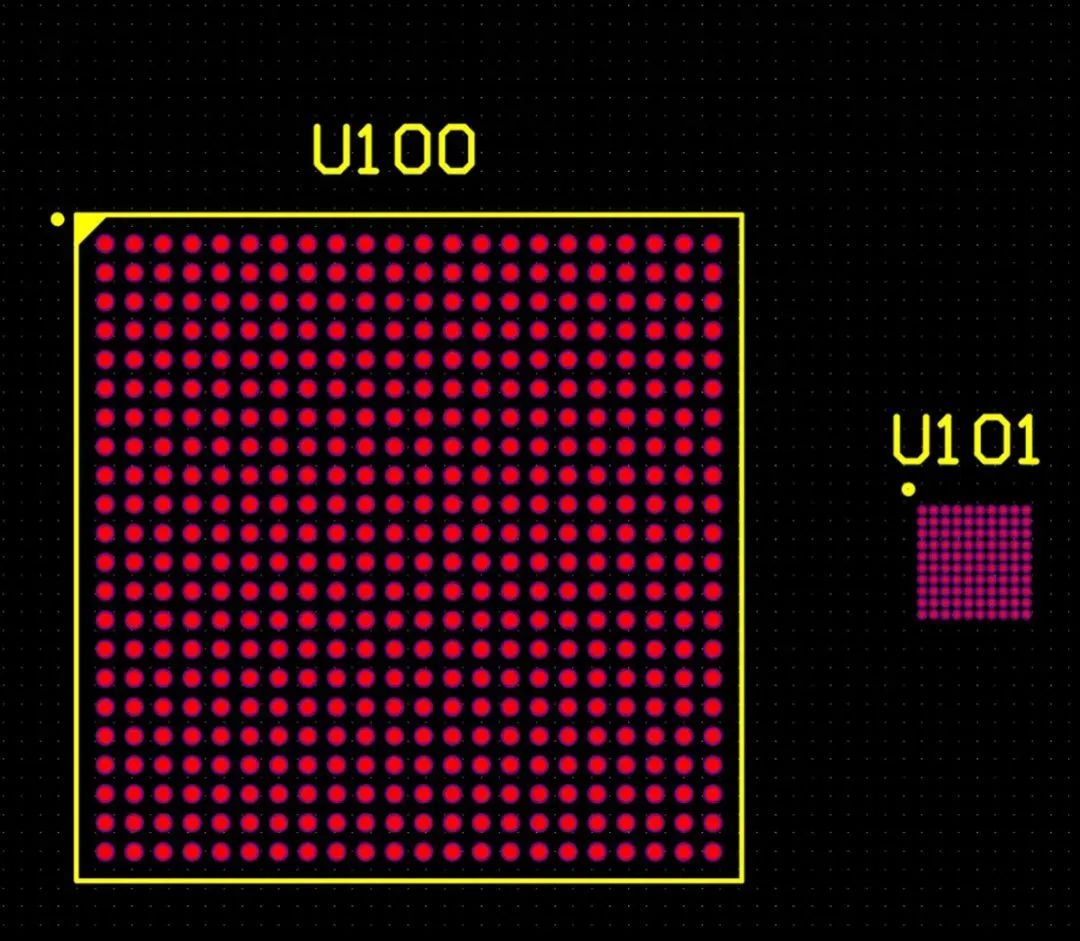

反過來,需要使用多次層壓和微通孔結(jié)構(gòu),以便成功地逃逸布線BGA。圖1對比了具有484個焊料球、1mm節(jié)距BGA(U100)和具有100個焊料球、0.4mm節(jié)距BGA(U101)的封裝和特征尺寸。

圖1:具有484個焊料球、1 mm間距BGA (U100)和具有100個焊料球、0.4 mm間距BGA (U101)的封裝和特征尺寸的對比。

首先,我們來看1mm節(jié)距的部件,然后評估如何將所有焊料球逃逸到BGA的外圍。對于該評估,只考慮使用堆疊微通孔。交錯排布微通孔也可以,但顯然需要更大的電路板面積。此外,疊層將為所有內(nèi)部信號層采用雙帶狀線。

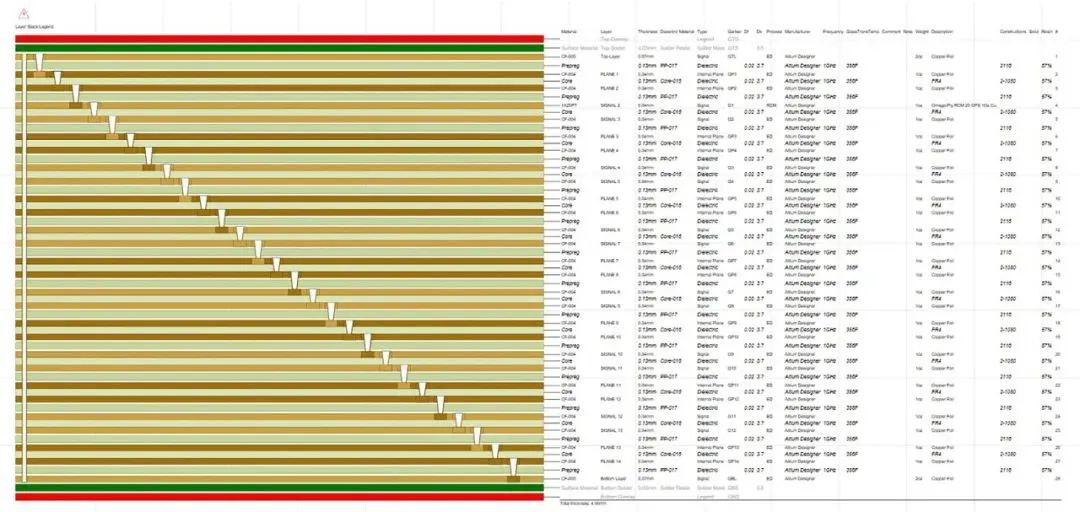

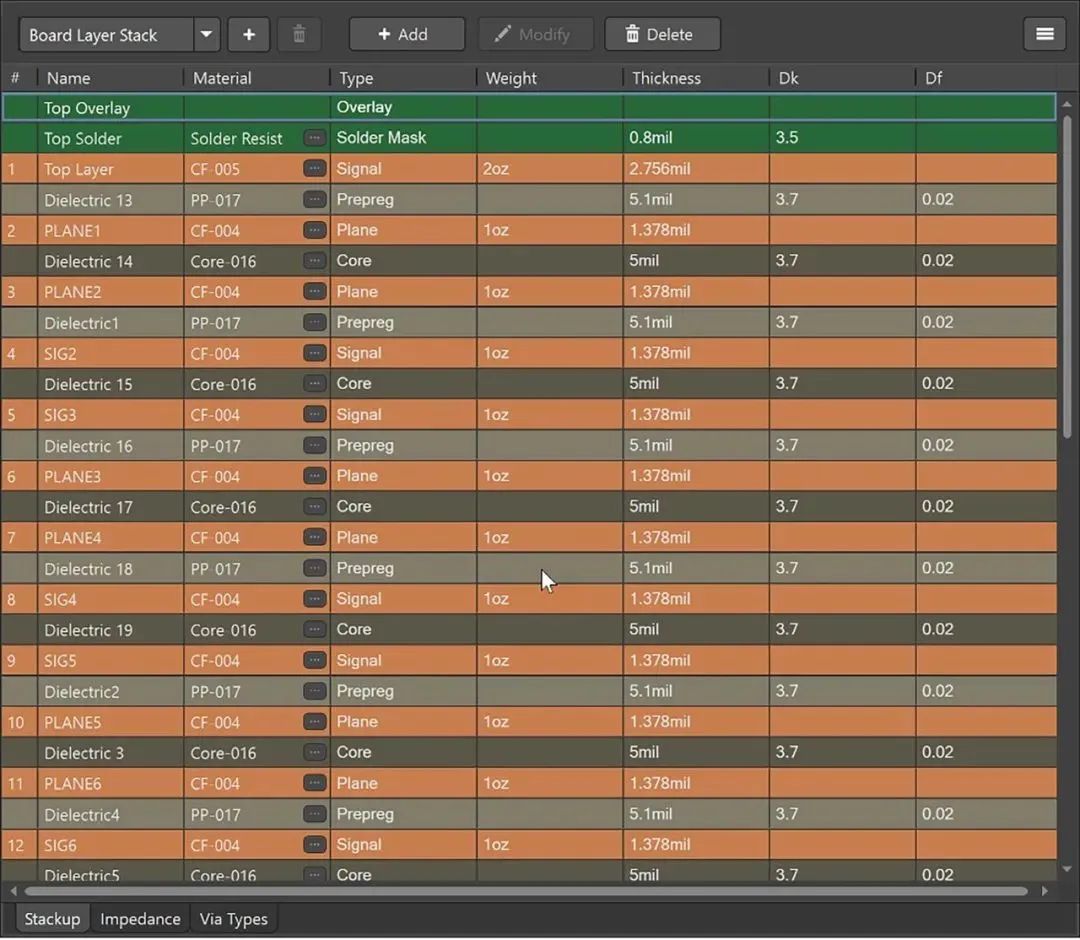

布線BGA的第一個挑戰(zhàn)是確定需要多少HDI(順序?qū)訅?微通孔)層。圖 2 顯示了每一層都是 HDI 層的28 層板結(jié)構(gòu)。但是當(dāng)前的HDI制造技術(shù)無法生產(chǎn)這樣的結(jié)構(gòu)。

圖 2:每層都是 HDI 層的 28 層板結(jié)構(gòu),目前的制造工藝無法實現(xiàn)。

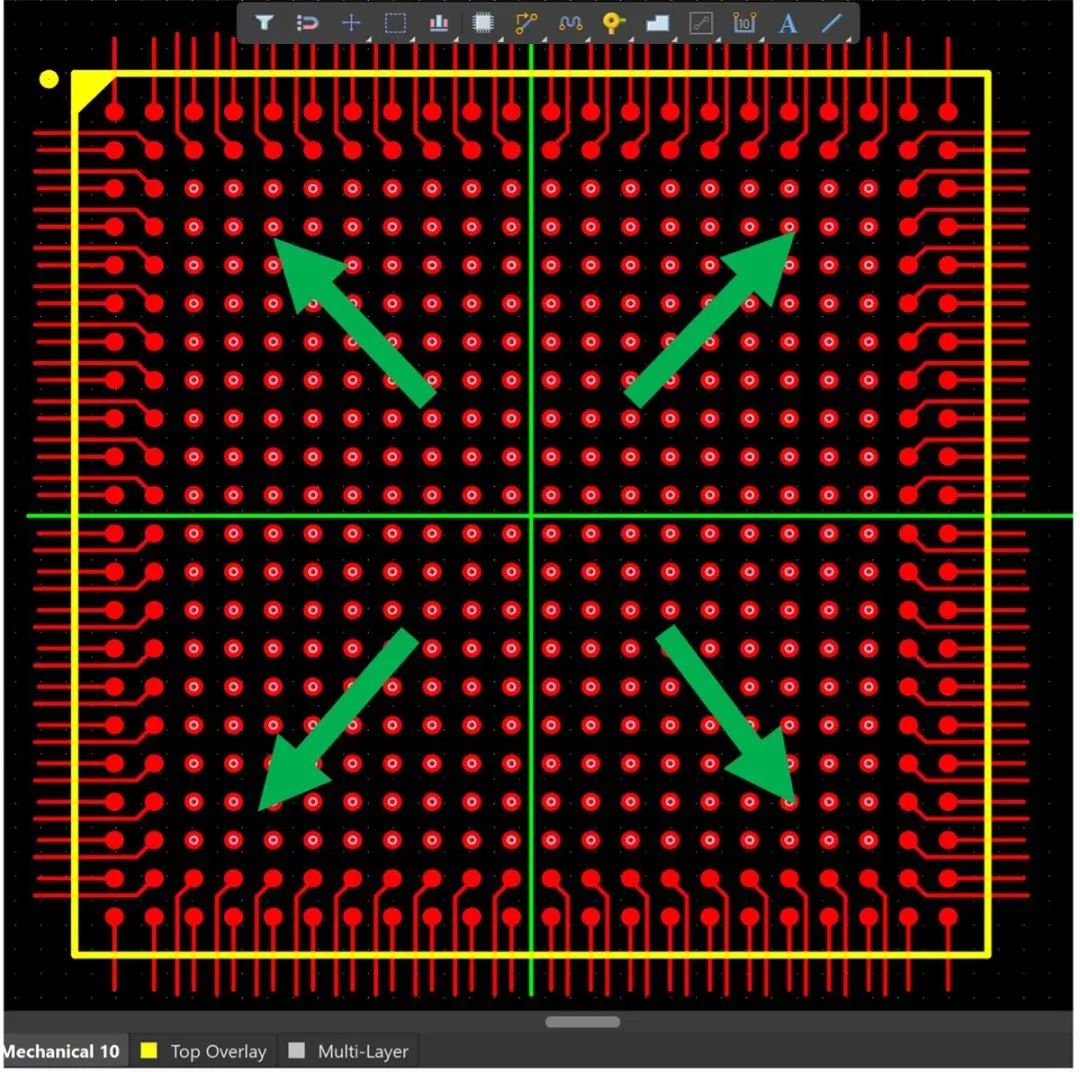

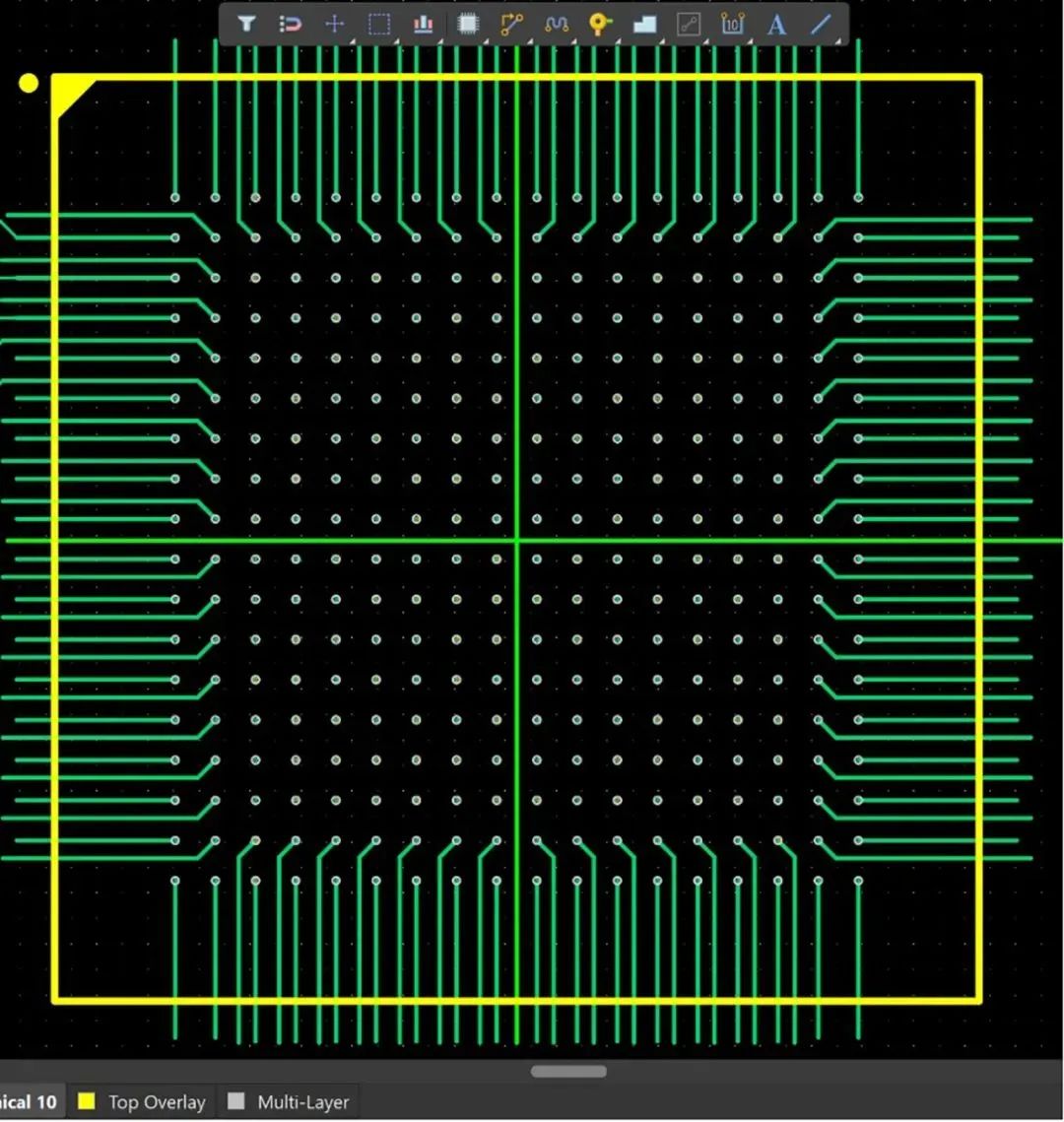

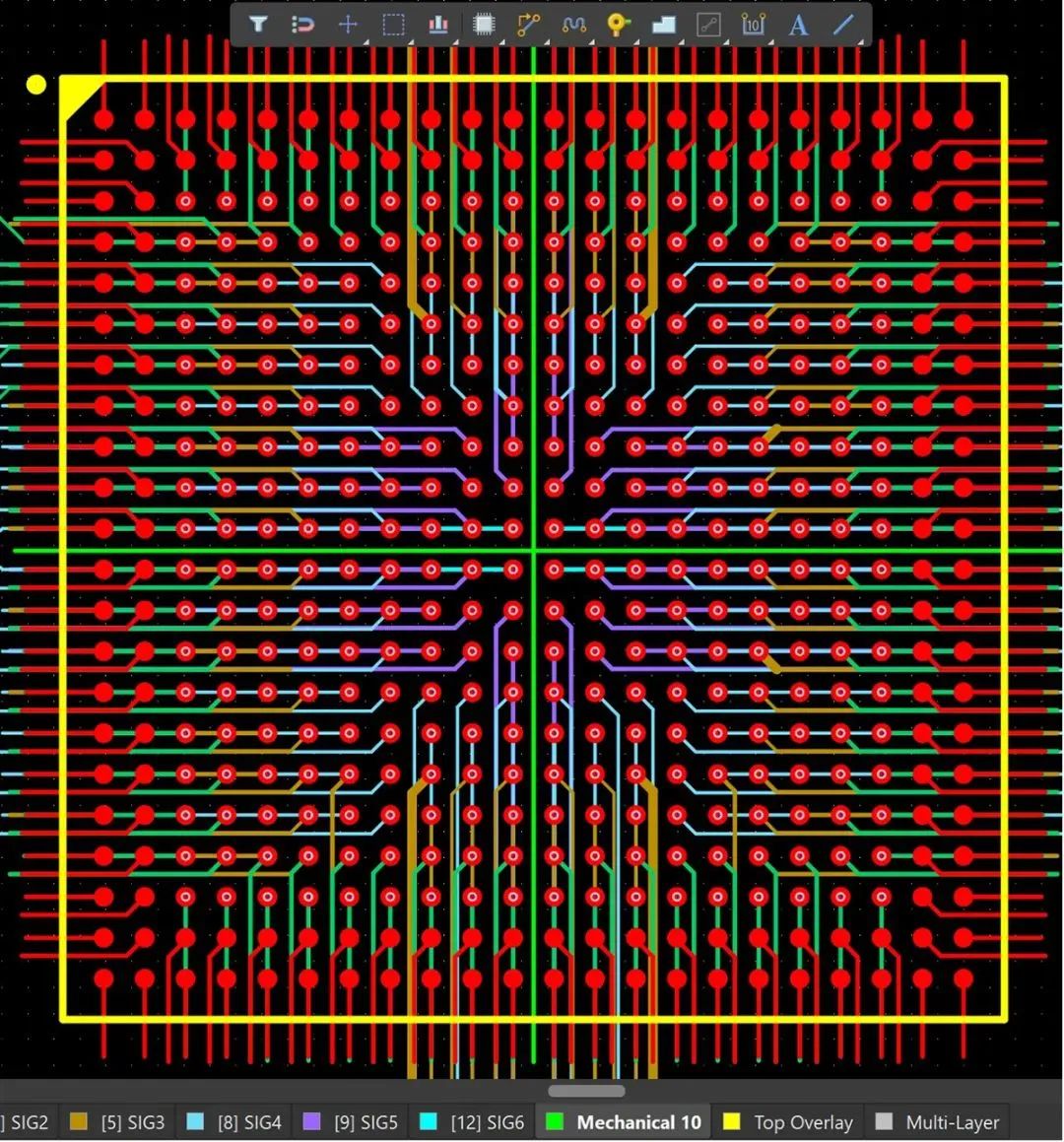

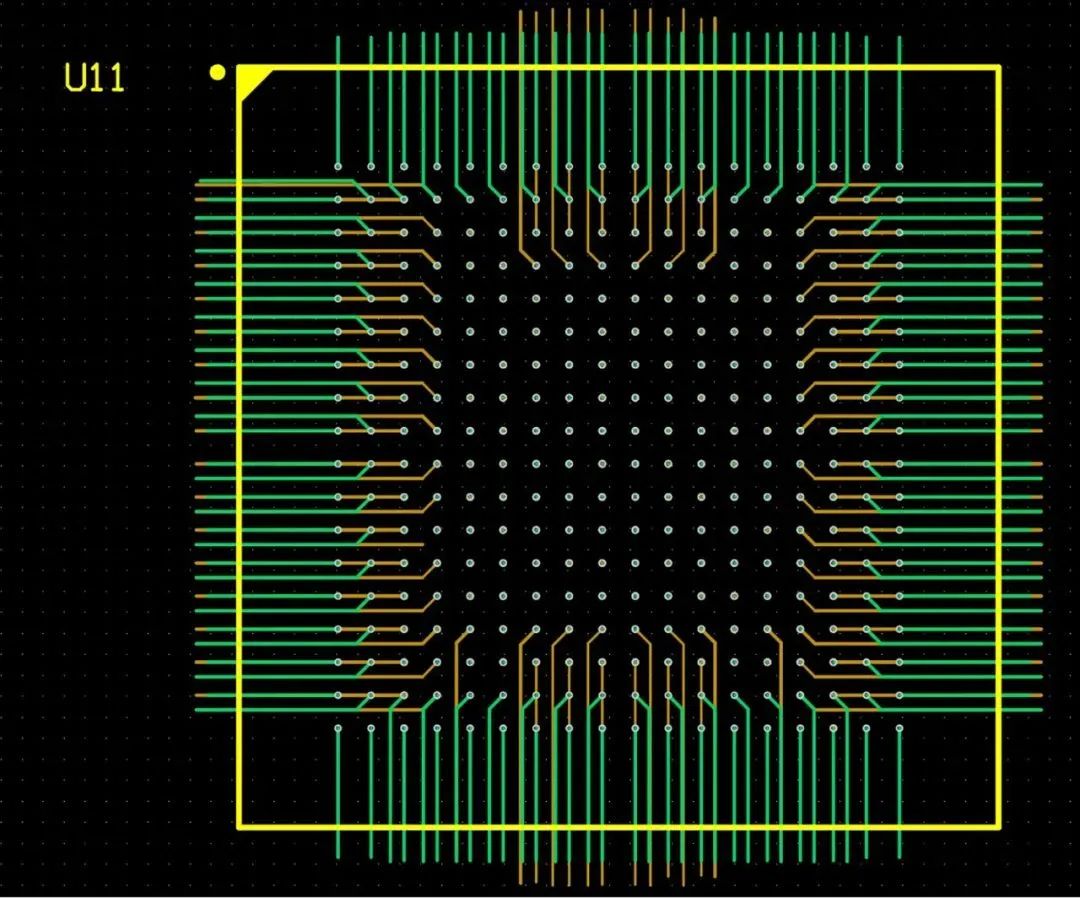

BGA逃逸布線的基本方法是四象限法。通過該方法,我們將BGA劃分為4個象限,然后在每個象限中使用標(biāo)準(zhǔn)模式。圖3顯示了基本象限圖形。

圖 3:用于逃逸布線BGA的象限圖形

界定象限后,將以兩行模式布線BGA。最靠外的行可直接布線。靠內(nèi)的行將沿著象限方向布線,然后直線布線。這里最靠外的兩行將在頂層布線。

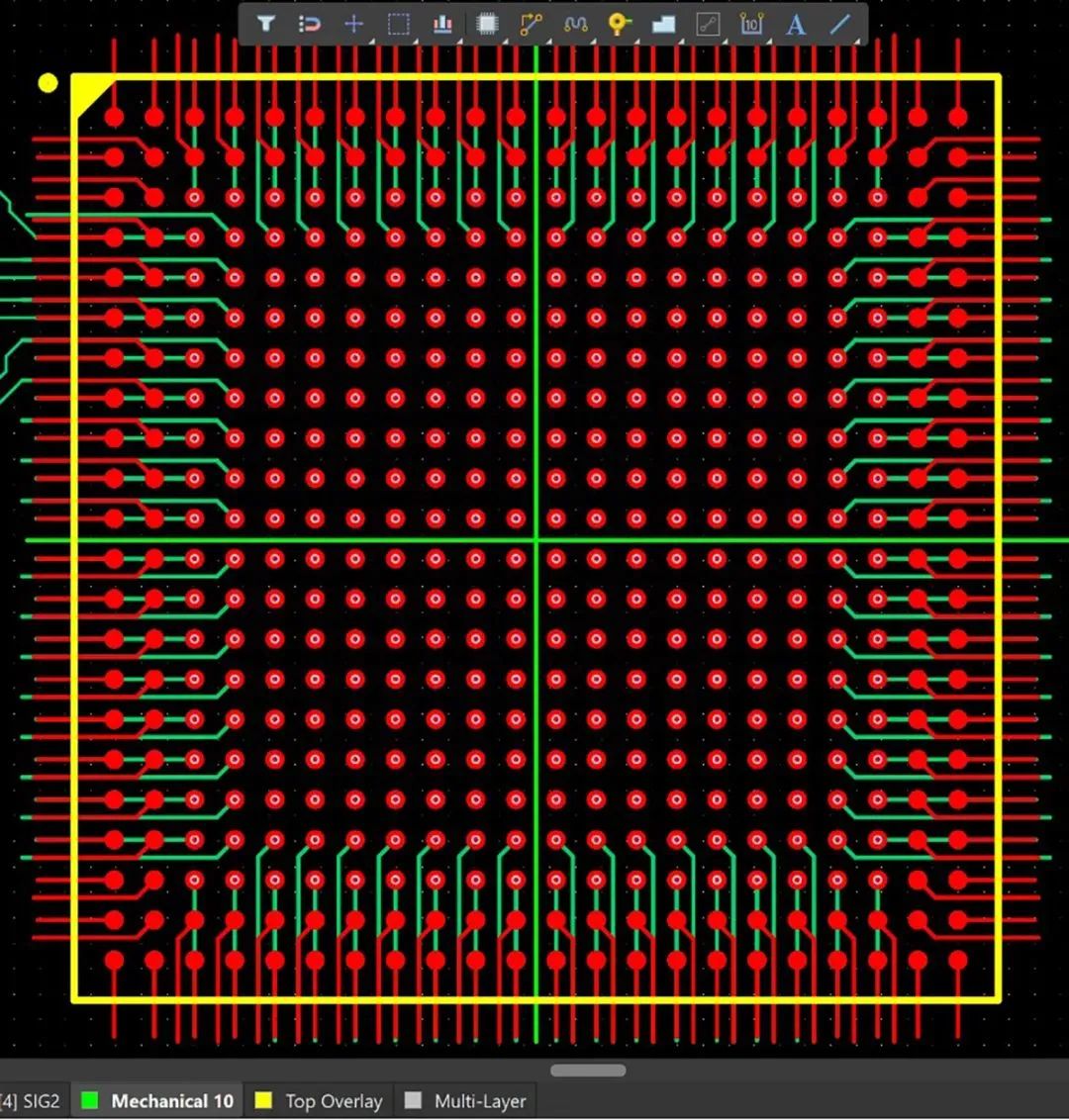

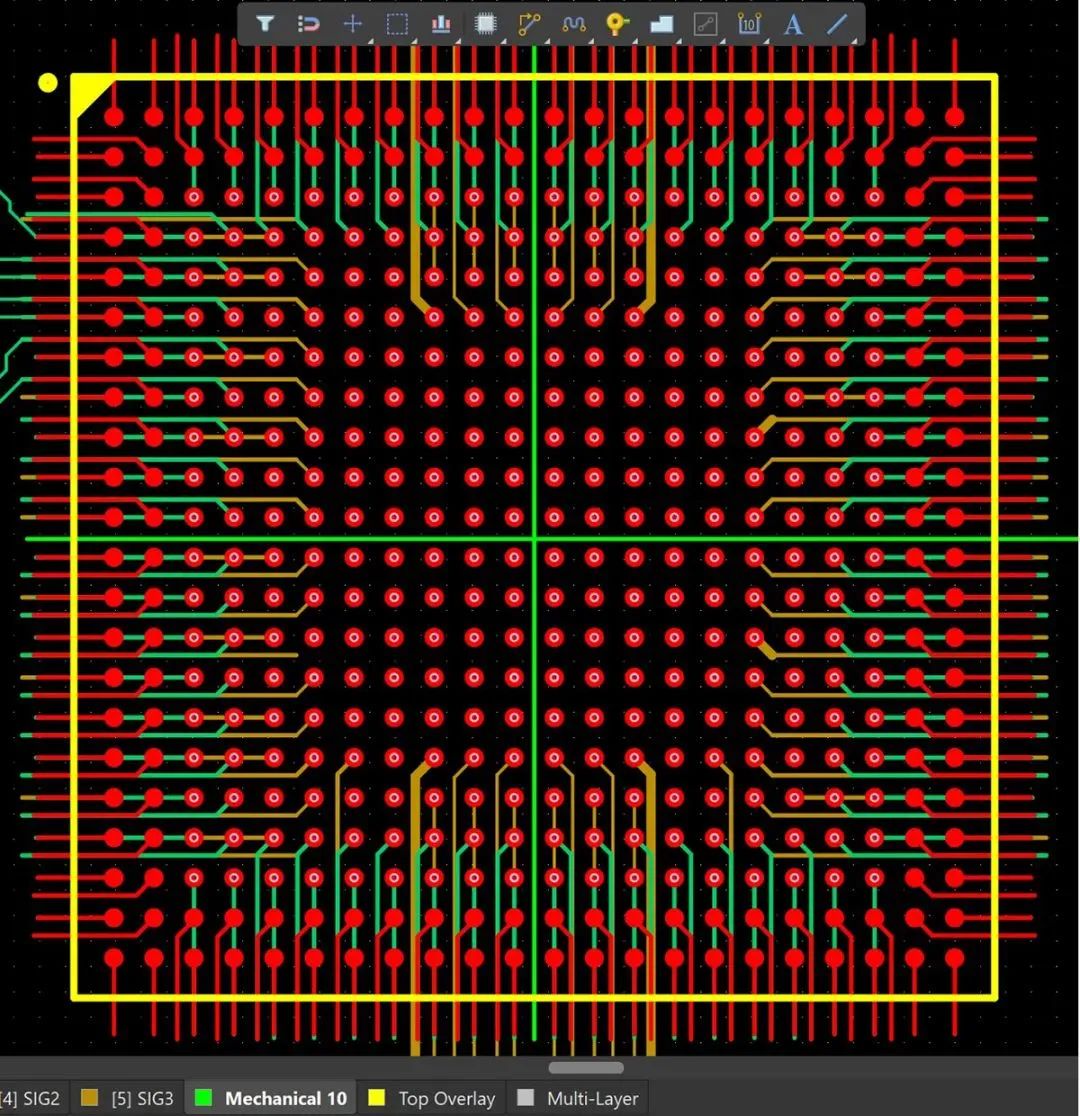

接下來的兩行將布線在第一層內(nèi)部信號層上,依此類推。圖 4 和圖 5 顯示了第一層內(nèi)部信號層的布線。

圖4:第一層內(nèi)部

信號層的布線

圖5:第一層內(nèi)部

信號層的布線(續(xù))

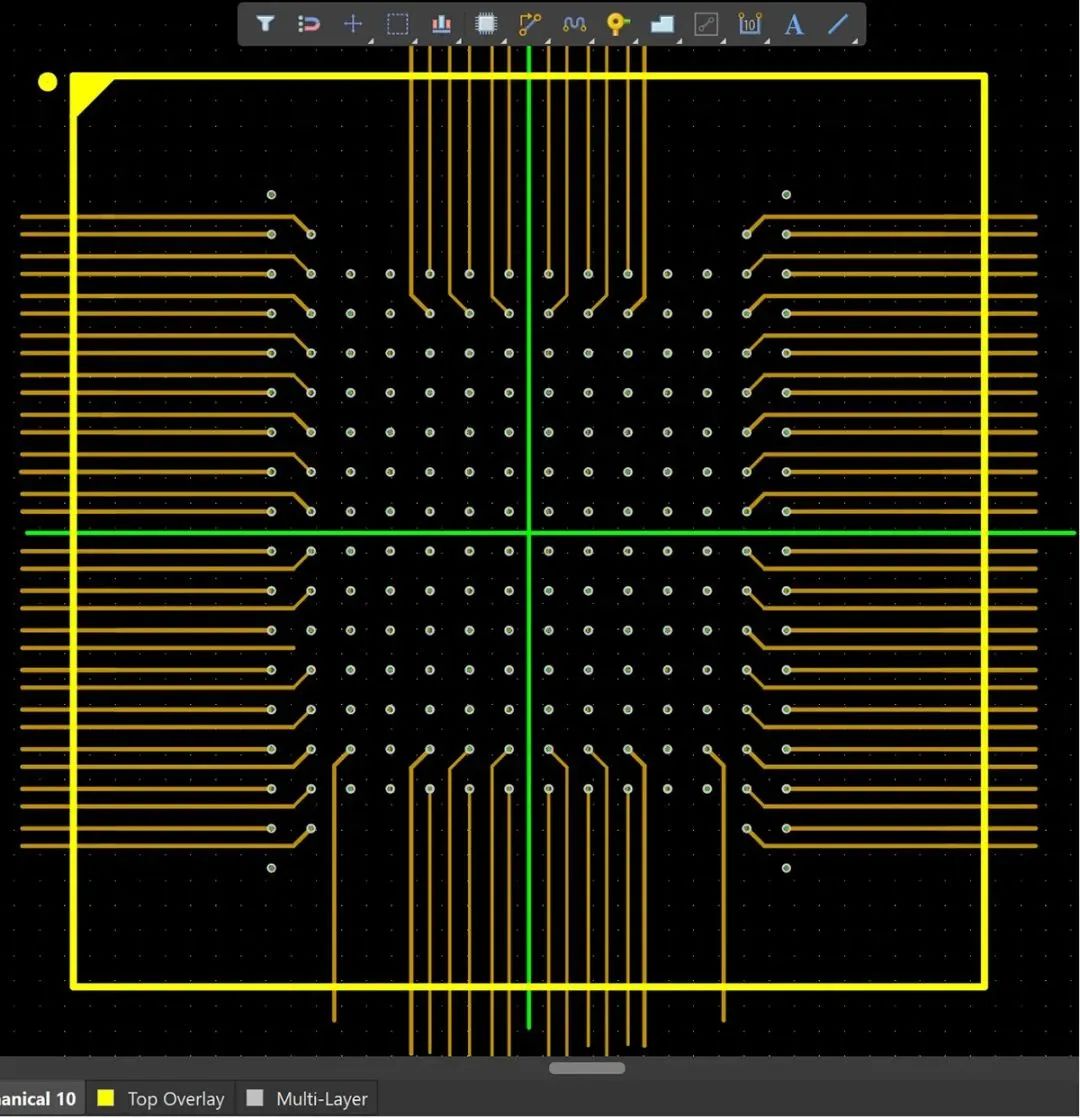

圖6:該排序的前12層

圖7:排序中另一個步驟

的屏幕截圖

圖8:逃逸布線順序

(續(xù))

圖 9:逃逸布線屏幕截圖說明了如今BGA布線的復(fù)雜性。

圖10:兩個相鄰的信號層——雙帶狀線結(jié)構(gòu)

在這個階段,從信號完整性的角度來看,應(yīng)該指出所采用的疊層是適當(dāng)?shù)模ㄉ院髮⒃敿毥榻BSI)。圖6顯示了排序的前12層。在該圖中,可以看到需要3個微通孔轉(zhuǎn)換來從頂層過渡到第2層信號層,第一層內(nèi)部信號層,頂層到平面1,平面1到平面2,平面2-第2層信號層。需要平面作為信號層對之間的屏蔽,并且需要平面作為對添加,形成平面電容,以處理數(shù)字電路的高速開關(guān)電流需求。

關(guān)于使用該方法可能遇到的一些信號完整性問題,我們將研究兩個相鄰的信號層——雙帶狀線結(jié)構(gòu)(圖10)。首先,注意同一信號層上走線之間的平行性,以及雙帶狀線的相鄰信號層上走線的平行性。對于信號完整性,相鄰層上的平行性是更大的問題,因為超過臨界長度,可能會導(dǎo)致串?dāng)_。

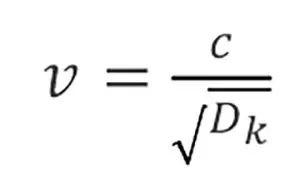

為了這個問題,我們必須了解臨界長度是過渡電氣長度(Transition Electrical Length,簡稱TEL)的一半,且TEL是信號在主動驅(qū)動期間在傳輸線(走線)上傳播的距離。這就是數(shù)字信號的上升/下降時間。為了計算TEL,我們必須用下面的公式確定傳輸線上的傳播速度。

(1)

其中:

Dk = 介電常數(shù)

c = 光速

v = 傳播速度

通過一點代數(shù)運算,公式1變?yōu)椋?/p>

(2)

現(xiàn)在假設(shè)標(biāo)準(zhǔn)FR-4的Dk為4.0,并使用英制單位(英寸),我們得到以下結(jié)果:

c = 983.6 x 106 ft/s

√Dk = √4 = 2

V = (983.6 x 106 ft/s) / 2 = 491.8 x 106 ft/s

(491.8 x 106 ft/s) x (12 in/ft) = 5.901 x 109 in/s

(5.901 x 109 in/s) x (1 x 10-9 ns/s) = 5.901 in/ns

由此可以看出,如果上升時間/下降時間為1ns,TEL約為6英寸,因此半TEL的臨界長度約為3英寸。由此可以看出,在需要添加串聯(lián)端接電阻之前,可以非常容易地逃逸FPGA,而不會出現(xiàn)嚴(yán)重的SI問題。

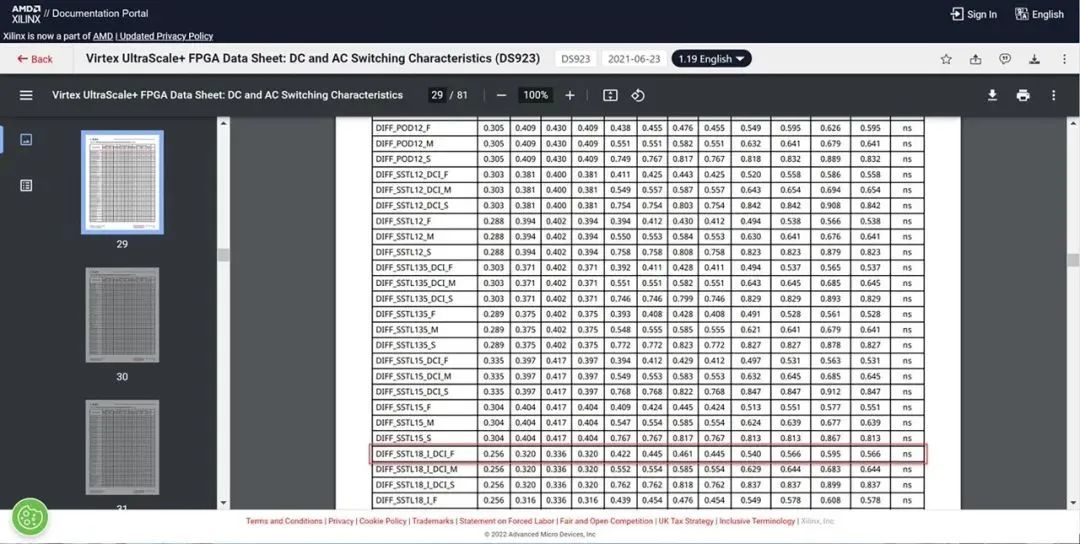

現(xiàn)代FPGA,如16 nm工藝的AMD Xilinx Virtex UltraSCALE+FPGA,切換速度高達0.250 ns(圖11)。由此,再次回到公式2,我們得到的TEL為1.475英寸,臨界長度為0.738英寸。

圖11:現(xiàn)代FPGA的開關(guān)速度高達0.250ns。

在以個位數(shù)納米通道長度的制程節(jié)點制造的下一代設(shè)備中,看到上升/下降時間為0.1ns (100 ps)或更快。這為我們提供了約0.6英寸的TEL和0.3英寸或更短的臨界長度。由此可以看到,在添加串聯(lián)端接電阻以獲得成功的信號完整性性能之前,不能期望將FPGA走線布線到FPGA主體的外圍。

為了成功地解決這個問題,電路板設(shè)計者需要在PCB結(jié)構(gòu)中使用成型的嵌入式電阻器。該方法使用PCB結(jié)構(gòu)的特殊層,即在同一層上具有兩種不同導(dǎo)電材料。一種是傳統(tǒng)的銅,另一種是鎳磷(Ni-P)等電阻材料,用于制造與FPGA/BGA焊料球的引腳/通孔一致的電阻器。

工藝節(jié)點是指MOSFET的柵極在MOSFET的漏極和源極之間形成的通道長度。圖12顯示了傳統(tǒng)MOSFET結(jié)構(gòu)的示例。隨著通道長度變短,電子從漏極移動到源極所需的時間變短(更快);這反過來又導(dǎo)致了現(xiàn)代設(shè)備中越來越快的上升時間/下降時間。這也是為什么我們說上升時間/下降時間而不是時鐘頻率是信號完整性規(guī)則必須應(yīng)用于設(shè)計的決定因素。

關(guān)于如何從現(xiàn)代FPGAs中逃逸布線的問題,為信號完整性所需的串聯(lián)端接集成了埋入電阻之后,仍然存在相鄰層上平行走線的串?dāng)_。使用的主要方法是z軸的走線分離。

如果無法在相鄰層的走線之間獲得足夠的間隔/偏移量,則需要添加額外的平面層,以在走線層之間提供屏蔽/隔離。這種方法有其自身的問題,因為需要向電路板添加許多層,這會由于增加的層數(shù)而增加質(zhì)量和整個制造復(fù)雜度,以及信號完整性需要始終添加平面作為Vcc/RTN的對,以為實現(xiàn)信號完整性增加平面電容,為實現(xiàn)可制造性提供適當(dāng)Z軸銅平衡。

正如我們所看到的,隨著封裝尺寸的減小和器件速度的提高,逃逸布線FPGA/BGA將持續(xù)給現(xiàn)代PCB設(shè)計師帶來重大挑戰(zhàn)。

Kris Moyer具有互連設(shè)計師/高級互連設(shè)計師資格,是IPC設(shè)計講師,任IPC 1-13委員會主席。

審核編輯:劉清

-

信號完整性

+關(guān)注

關(guān)注

68文章

1437瀏覽量

96490 -

BGA封裝

+關(guān)注

關(guān)注

4文章

121瀏覽量

18439 -

HDI

+關(guān)注

關(guān)注

7文章

212瀏覽量

21752 -

Tel

+關(guān)注

關(guān)注

0文章

8瀏覽量

9704

原文標(biāo)題:高階封裝意味著復(fù)雜的布線

文章出處:【微信號:actSMTC,微信公眾號:actSMTC】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

高階封裝意味著復(fù)雜的布線簡析

高階封裝意味著復(fù)雜的布線簡析

評論