當(dāng)一個(gè)SoC芯片項(xiàng)目將要切入到FPGA原型驗(yàn)證階段時(shí),F(xiàn)PGA原型驗(yàn)證團(tuán)隊(duì)如何評(píng)估是否可以進(jìn)入原型驗(yàn)證階段進(jìn)行新一個(gè)階段的驗(yàn)證工作呢?

1. SoC代碼是否成熟?

我們當(dāng)然希望在項(xiàng)目中盡快準(zhǔn)備好基于FPGA原型驗(yàn)證的代碼,以便最大限度地為軟件團(tuán)隊(duì)和RTL驗(yàn)證人員帶來更客觀的收益。然而,假如過早地開始FPGA原型驗(yàn)證工作,由于RTL代碼在Simulation階段驗(yàn)證不成熟或不充分,那么將會(huì)浪費(fèi)大量的時(shí)間(因?yàn)镕PGA原型驗(yàn)證過程中debug的難度數(shù)倍與Simulation)而只發(fā)現(xiàn)簡單的RTL的bug,如果使用Simulation仿真,其實(shí)容易發(fā)現(xiàn)這些簡單bug,這樣原型驗(yàn)證的時(shí)間、技能和設(shè)備都沒有得到有效利用。

所有SoC芯片項(xiàng)目組將在項(xiàng)目的各個(gè)階段制定一份SoC驗(yàn)證設(shè)計(jì)。該計(jì)劃的目標(biāo)始終是100%驗(yàn)證SoC并自我確認(rèn)已實(shí)現(xiàn)。一般包含Simulation驗(yàn)證計(jì)劃,F(xiàn)PGA原型驗(yàn)證計(jì)劃,Emulation驗(yàn)證計(jì)劃等。一些驗(yàn)證團(tuán)隊(duì)采用高效且通用的Simulation驗(yàn)證方法,如UVM,主要用于System Verilog中編寫的復(fù)雜測試環(huán)境,此驗(yàn)證計(jì)劃記錄了驗(yàn)證工程師對(duì)于相關(guān)功能測試點(diǎn)進(jìn)行的驗(yàn)證,以及每個(gè)測試的當(dāng)前設(shè)計(jì)狀態(tài),相關(guān)的工程師會(huì)采用收集覆蓋率的方法保證基本的bug在Simulation階段都已經(jīng)驗(yàn)證完備了。此時(shí)整個(gè)RTL的成熟度可以認(rèn)為是90%了,剩下的10%要通過FPGA原型驗(yàn)證或者Emulation才能保證驗(yàn)證完備。此時(shí),恭喜你,可以進(jìn)行ASIC代碼到FPGA代碼的移植工作了!

2. SoC的功能有多少可以通過FPGA原型驗(yàn)證平臺(tái)來驗(yàn)證?

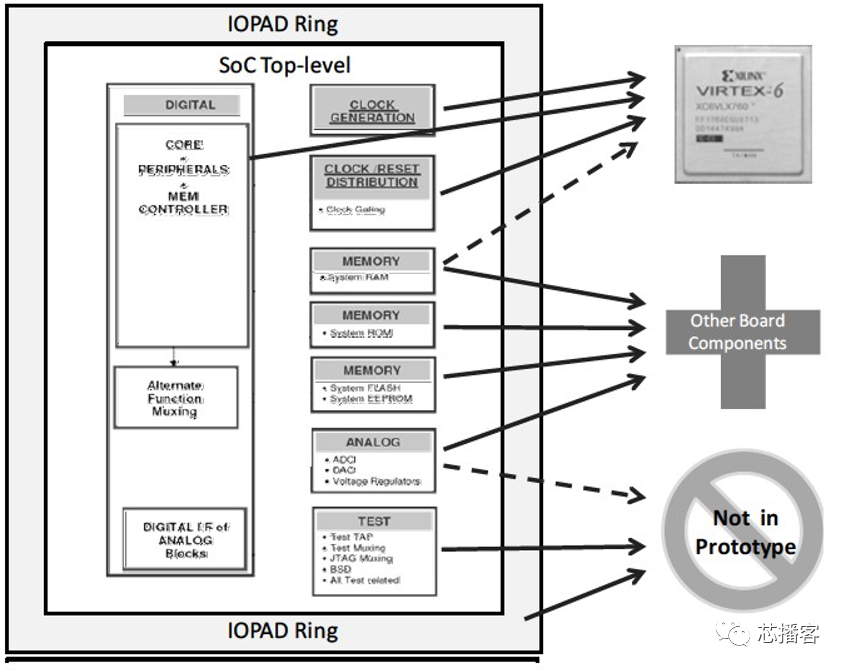

在早期規(guī)劃階段,我們需要確認(rèn)進(jìn)行FPGA原型驗(yàn)證的范圍。當(dāng)然,通常而言,團(tuán)隊(duì)決策者是貪心的,一般都想將整個(gè)SoC的功能都進(jìn)行驗(yàn)證,所以有團(tuán)隊(duì)甚至一上來就規(guī)劃幾十片F(xiàn)PGA甚至上百片F(xiàn)PGA原型驗(yàn)證的計(jì)劃,其實(shí)都不算很合理。我們需要從SoC的架構(gòu)以及能實(shí)現(xiàn)FPGA原型驗(yàn)證的規(guī)模通篇考慮,因?yàn)槌晒Υ罱◣资习倨現(xiàn)PGA的原型驗(yàn)證系統(tǒng)實(shí)屬不易。

在考慮分多片F(xiàn)PGA原型驗(yàn)證系統(tǒng)之前,我們需要權(quán)衡哪些一定功能點(diǎn)相關(guān)設(shè)計(jì)一定要放在FPGA原型驗(yàn)證系統(tǒng)中,哪些功能點(diǎn)可以放在其他片外或者Emulation階段去保證,也就是在項(xiàng)目中通常所說的“閹割”版本的FPGA原型驗(yàn)證系統(tǒng),不管是規(guī)模還是功能,都建議從小到大,由簡到難的順序去做相關(guān)的移植工作,當(dāng)然這樣的版本不宜太多。簡單來講:哪些可以進(jìn)入FPGA原型驗(yàn)證來做,哪些不能進(jìn)入FPGA原型驗(yàn)證來做。

對(duì)于給定的平臺(tái),較小的設(shè)計(jì)通常以更快的時(shí)鐘速率運(yùn)行,并且比較大的設(shè)計(jì)花費(fèi)更少的時(shí)間來處理。因此,我們應(yīng)該謹(jǐn)慎地將更多的SoC設(shè)計(jì)納入到原型中。我們可以通過哪些方式減少原型的規(guī)模,而不會(huì)過度降低其有用性或準(zhǔn)確性?

為了減小設(shè)計(jì)尺寸并緩解容量限制,可以考慮以下選項(xiàng):

永久性邏輯移除:當(dāng)SoC設(shè)計(jì)中的塊具有可添加到FPGA平臺(tái)的硬件等效物(物理SoC、評(píng)估平臺(tái)等)時(shí),它是從將映射到FPGA的邏輯中移除的好候選。除了節(jié)省空間外,這些塊可以以比FPGA平臺(tái)中可達(dá)到的速度更快的速度運(yùn)行。此類塊的典型示例是第三方IP,例如處理器或?qū)S?a target="_blank">控制器。

臨時(shí)邏輯“閹割”:當(dāng)邏輯量超過FPGA平臺(tái)中的可行空間時(shí),可以考慮臨時(shí)移除一些塊。當(dāng)SoC的一部分可以被原型化時(shí),這可以起作用。例如,如果一個(gè)SoC有多個(gè)可能的內(nèi)存接口,但實(shí)際應(yīng)用中只使用一個(gè),那么一次一個(gè)地對(duì)它們進(jìn)行原型化,而其他的則被移除,這將單獨(dú)驗(yàn)證每一個(gè)。

整體功能縮放:當(dāng)SoC中的塊大小將超過整個(gè)FPGA平臺(tái)中的可用可行空間時(shí),可以考慮縮小它們。例如,SoC存儲(chǔ)器塊可按比例縮小以在任何給定時(shí)間運(yùn)行代碼的子集,或者可替代地,多通道設(shè)計(jì)的一個(gè)通道可能足以代表用于原型化通道驅(qū)動(dòng)器軟件的足夠功能。

3. 評(píng)估配合FPGA完成相關(guān)功能的外接設(shè)備卡

雖然FPGA原型驗(yàn)證平臺(tái)中,主要起作用的一定是這個(gè)系統(tǒng)中最主要的FPGA,但是,現(xiàn)代SoC中的功能非常豐富,單純的FPGA資源一般不能完全滿足SoC的驗(yàn)證需求,所以要考慮外接設(shè)備卡進(jìn)行整系統(tǒng)的驗(yàn)證。

一般情況下,出于評(píng)估目的,SoC芯片的IP供應(yīng)商通常提供在在FPGA上可實(shí)現(xiàn)的IP,以供客戶進(jìn)行FPGA原型驗(yàn)證。在其他情況下,項(xiàng)目組的FPGA原型團(tuán)隊(duì)可以設(shè)計(jì)或者構(gòu)建功能上等同于未映射到FPGA的IP塊的電路板,當(dāng)然現(xiàn)今的FPGA原型驗(yàn)證供應(yīng)商會(huì)提供各種類型的功能子卡。為了適應(yīng)這些外部硬件選項(xiàng),我們需要驗(yàn)證/執(zhí)行以下操作:

a. 在RTL中提供與FPGA外部模塊的連接。

b. 確保FPGA和外部硬件模塊之間的IO的信號(hào)級(jí)別彼此兼容。

c. 確保外部硬件的信號(hào)完整性可被FPGA和硬件模塊接受。典型的FPGA 的IO有許多選項(xiàng),如信號(hào)電平、速度以及驅(qū)動(dòng)強(qiáng)度。我們應(yīng)該熟悉這些選項(xiàng),以及如何在特定的原型環(huán)境中最佳地使用它們。

d. 提供所需的時(shí)鐘,考慮時(shí)鐘延遲,能夠計(jì)算FPGA系統(tǒng)和外部硬件之間的互連定時(shí)。

e. 固定硬件的啟動(dòng)時(shí)間可能比FPGA系統(tǒng)啟動(dòng)時(shí)間短得多,因?yàn)镕PGA需要在開始工作之前加載。早期啟動(dòng)可能導(dǎo)致硬件模塊和FPGA系統(tǒng)之間的同步問題。

f. 外部硬件模塊如何物理連接到FPGA系統(tǒng),以及如何供電。必須注意布線和與FPGA系統(tǒng)的重復(fù)連接,以保護(hù)FPGA和硬件模塊。當(dāng)需要將原型運(yùn)送到遠(yuǎn)程實(shí)驗(yàn)室或客戶時(shí),一個(gè)好的機(jī)械計(jì)劃將使其更容易。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1640文章

21896瀏覽量

611188 -

asic

+關(guān)注

關(guān)注

34文章

1237瀏覽量

121636 -

soc

+關(guān)注

關(guān)注

38文章

4288瀏覽量

220891 -

RTL

+關(guān)注

關(guān)注

1文章

387瀏覽量

60459

原文標(biāo)題:從SoC仿真驗(yàn)證到FPGA原型驗(yàn)證的時(shí)機(jī)

文章出處:【微信號(hào):于博士Jacky,微信公眾號(hào):于博士Jacky】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

驗(yàn)證中的FPGA原型驗(yàn)證 FPGA原型設(shè)計(jì)面臨的挑戰(zhàn)是什么?

大規(guī)模 SoC 原型驗(yàn)證面臨哪些技術(shù)挑戰(zhàn)?

高頻RFID芯片的FPGA原型驗(yàn)證平臺(tái)設(shè)計(jì)及驗(yàn)證

SoC驗(yàn)證平臺(tái)的FPGA綜合怎么實(shí)現(xiàn)?

FPGA原型驗(yàn)證的技術(shù)進(jìn)階之路

基于FPGA的驗(yàn)證平臺(tái)及有效的SoC驗(yàn)證過程和方法

關(guān)于無源高頻電子標(biāo)簽芯片功能驗(yàn)證的FPGA原型驗(yàn)證平臺(tái)設(shè)計(jì)

為什么SoC驗(yàn)證一定需要FPGA原型驗(yàn)證呢??

如何建立適合團(tuán)隊(duì)的FPGA原型驗(yàn)證系統(tǒng)平臺(tái)與技術(shù)?

什么是FPGA原型驗(yàn)證?如何用FPGA對(duì)ASIC進(jìn)行原型驗(yàn)證

SoC設(shè)計(jì)的IO PAD怎么移植到FPGA原型驗(yàn)證

正確認(rèn)識(shí)原型驗(yàn)證多片FPGA自動(dòng)分割工具

SoC設(shè)計(jì)的IO PAD怎么移植到FPGA原型驗(yàn)證

為什么SoC驗(yàn)證一定需要FPGA原型驗(yàn)證呢?

SoC的功能有多少可以通過FPGA原型驗(yàn)證平臺(tái)來驗(yàn)證?

SoC的功能有多少可以通過FPGA原型驗(yàn)證平臺(tái)來驗(yàn)證?

評(píng)論