ANSI EIA/TIA-644 低壓差分信號 (LVDS) 標(biāo)準(zhǔn)比更傳統(tǒng)的 ECL、PECL 和 CML 標(biāo)準(zhǔn)提供更低的功率和更低的噪聲發(fā)射,用于高速信號分配。本應(yīng)用筆記比較了這些通信標(biāo)準(zhǔn)的一些特性,并討論了LVDS標(biāo)準(zhǔn)的一些優(yōu)點。

介紹

隨著微處理器、DSP和數(shù)字ASIC時鐘頻率的增加,背板信號的速度也在增加。更快的時鐘速率限制了基于單端TTL的信令的限制。反過來,這種應(yīng)變又會增加功耗;振鈴,導(dǎo)致位錯誤;高水平的輻射發(fā)射;傳輸線效應(yīng),如阻抗失配和串?dāng)_;電源解耦困難等問題。盡管有報道稱使用該技術(shù)可以保持大于50MHz的速度,但其他信令技術(shù)值得考慮。

增加總線和/或背板帶寬的一種方法是增加總線寬度。然而,這種方法使PC板布局復(fù)雜化,并且需要高引腳數(shù)連接器,這些連接器既昂貴又笨重。當(dāng)距離超過幾厘米時,串行數(shù)據(jù)流很有吸引力。可以從串行數(shù)據(jù)流中受益的高速數(shù)據(jù)通信系統(tǒng)包括第三代基站、路由器、分插復(fù)用器和其他設(shè)備。

低壓差分信號(LVDS)可以取代TTL,實現(xiàn)低錯誤率、低串?dāng)_和低輻射發(fā)射的背板通信。

LVDS、ECL、PECL 和 CML 的特征

LVDS在高速系統(tǒng)中的應(yīng)用越來越多,這些系統(tǒng)需要信號完整性、低抖動(抖動可以定義為信號輸出轉(zhuǎn)換與其理想位置在時間上的偏差)和良好的共模性能。LVDS是用于高速串行接口的信令技術(shù)之一。

其他信令技術(shù)(按速度從最慢到最快的大致順序排列)是ECL(發(fā)射極耦合邏輯),PECL(正ECL)和CML(電流模式邏輯)。請注意,這些信令技術(shù)中的每一種都是差分的。

ECL是傳統(tǒng)的高速邏輯技術(shù),最初基于雙極晶體管差分對。在其初始形式中,它使用負(fù)偏置電源。PECL是ECL的一種形式,以正電源為參考。最新一代的ECL器件表現(xiàn)出200ps的傳播延遲,切換頻率超過3GHz。

在目前可用的所有接口中,CML以最高速度運行,用于需要千兆位數(shù)據(jù)速率的應(yīng)用。與其他技術(shù)相比,CML還有一個額外的優(yōu)勢:它包括一個集成的50Ω端接,這大大簡化了確保與硅片良好匹配的任務(wù)。但是,如果鏈路的每一端在不同的電源電壓下工作,則需要一些外部耦合元件。

本文重點介紹LVDS的特性及其可能的應(yīng)用。表1列出了其中一些特征,并將它們與ECL、PECL和CML系統(tǒng)中的特征進(jìn)行了比較。根據(jù)EIA/TIA-644 LVDS和IEEE 1596.3標(biāo)準(zhǔn)的規(guī)定,LVDS使用幅度范圍為250mV至400mV的差分信號,失調(diào)為1.2V。?

| LVDS | 預(yù)期信用損失 | PECL | 三氯聯(lián) | |

| 差分電壓擺幅 | 250mV 至 400mV | ~0.8V | ~0.8V | 0.4V |

| 直流偏移 | 1.2V | -1.3V | V抄送- 1.3V | V抄送- 0.2V |

| 傳播延遲 | ~1ns | 200點 | 200點 | 取決于技術(shù) |

| *ECL和PECL發(fā)射器輸出信號擺幅高于LVDS發(fā)射器。ECL和PECL器件表現(xiàn)出更高的信號擺幅和更短的傳播延遲,但代價是更高的功耗。 | ||||

LVDS的優(yōu)勢

LVDS的許多優(yōu)點源于其差分特性:它不受共模噪聲的影響,理論上,它本身不發(fā)射噪聲。(這假設(shè)差分信號完全對稱,即正輸出和負(fù)輸出之間沒有偏差。LVDS可以在CMOS中實現(xiàn),從而簡化了其與其他電路的集成。

由于LVDS是差分的,因此從其電源汲取的電流尖峰幅度較小,并且使用適當(dāng)放置的合理值去耦電容可以更容易地處理。此外,LVDS通常比ECL和CML消耗更少的功率,盡管這在一定程度上取決于所使用的端接技術(shù)。

LVDS的應(yīng)用

LVDS非常適合的眾多應(yīng)用包括時鐘分配和多點對點信號分配。時鐘分配在數(shù)字系統(tǒng)中非常重要,因為數(shù)字系統(tǒng)需要不同的子系統(tǒng)使用相同的時鐘參考。例如,在大多數(shù)情況下,基站的DSP部分必須與射頻信號處理部分同步,鎖相環(huán)(PLL)產(chǎn)生所需的本地振蕩器頻率,ADC鎖定到中央時鐘基準(zhǔn)。此外,當(dāng)使用包含無線電接收器的應(yīng)用時,時鐘(和信號)必須以盡可能低的發(fā)射水平分配,以避免干擾低電平信號路徑。

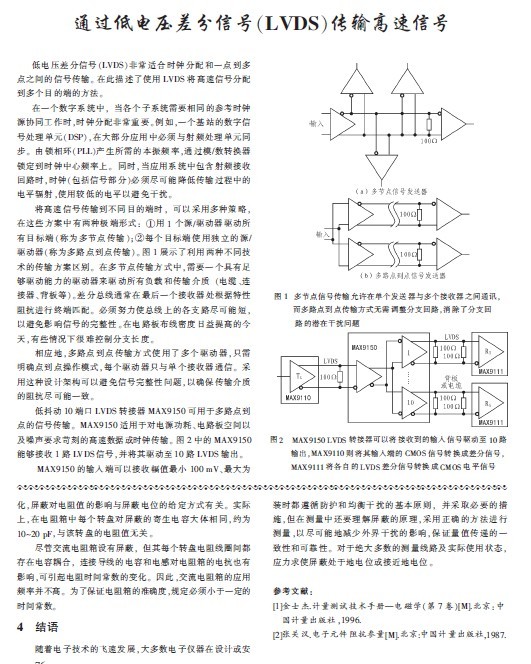

當(dāng)將高速信號分配到不同的目的地時,可以采用各種策略。兩種方法表示您可以找到策略范圍的極端情況:一種,從單個源/驅(qū)動因素驅(qū)動所有目標(biāo)(稱為多點分布);第二,為每個目標(biāo)使用單獨的驅(qū)動程序(稱為多點對點分布)。圖 1 顯示了這兩種類型分布方案與兩種典型技術(shù)之間的差異。在多點分配中,具有足夠驅(qū)動能力的驅(qū)動器驅(qū)動所有接收器和中間介質(zhì)(電纜、連接器、背板)。總線通常以其特性阻抗端接在最終接收器處。必須努力使總線上的所有“存根”或分支盡可能短,以避免可能的信號完整性問題。在當(dāng)今的高密度印刷電路板上,控制短截線長度并不總是那么簡單。

圖1.多點信號分配允許一個發(fā)射器和多個接收器之間進(jìn)行通信。多個點對點信號分配不需要調(diào)諧短截線,消除了這些短截線可能產(chǎn)生的干擾。

多點對點策略采用多個驅(qū)動器,只需為點對點操作指定這些驅(qū)動器,因為每個驅(qū)動器都與單個本地端接接收器通信。通過這種方案,減少了信號完整性的問題,以確保介質(zhì)的阻抗盡可能均勻。消除了存根可能造成的干擾。

審核編輯:郭婷

-

連接器

+關(guān)注

關(guān)注

99文章

15283瀏覽量

139647 -

微處理器

+關(guān)注

關(guān)注

11文章

2373瀏覽量

83942 -

lvds

+關(guān)注

關(guān)注

2文章

1120瀏覽量

67220

發(fā)布評論請先 登錄

光分路器是什么?PLC分路器都有哪些類型?

什么是光分路器,有哪些重要技術(shù)指標(biāo)?

AdvancedTCA熱插拔控制器簡化了功率分配

LVDS分離器簡化高速信號分配

通過低電壓差分信號(LVDS)傳輸高速信號

通過低電壓差分信號(LVDS)傳輸高速信號

使用低壓差分信號LVDS進(jìn)行高速信號分配

LVDS支持3G基站的高速信號分配

LVDS分路器簡化了高速信號分配

LVDS分路器簡化了高速信號分配

評論