1 運行平臺

硬件:CRD500數字信號處理板

系統:win7/64;win7/32;win10/64

軟件:Quartus/ModelSimSE/Verilog/Matlab

2 主要功能及性能指標

2.2.1主要功能

1)產生基帶原始數據

2)完成2FSK調制

3)完成2FSK解調

2.2.2主要性能指標

1) 調制端

系統時鐘:50MHz

基帶數據碼率:390.625kbps

載波頻率:3MHz

調制度:3.5

2) 解調端

系統時鐘:50MHz

采樣頻率:25MHz

解調方式:非相干

位同步:超前-滯后型數字鎖相環位同步

3 程序結構框圖說明

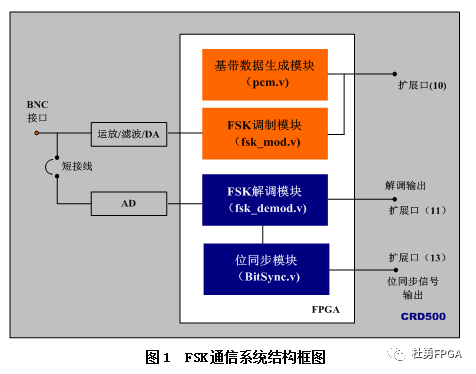

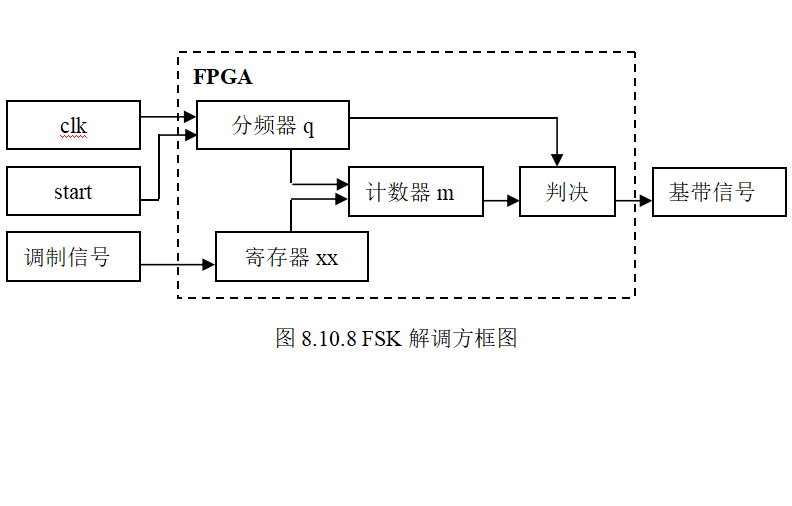

FSK通信系統主要由基帶數據生成模塊(pcm.v)、FSK調制模塊(fsk_mod.v) 、FSK解調模塊(fsk_demod.v)和鎖相環位同步模塊(BitSync.v)組成。

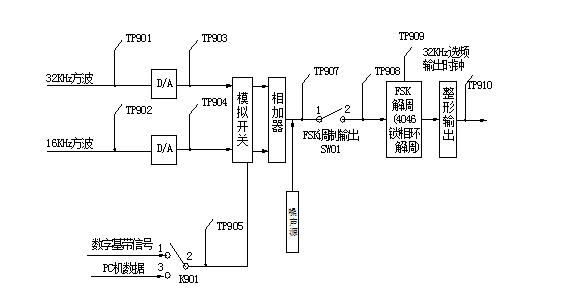

基帶數據生成模塊生成的原始數據(390.625kbps)送至FSK調制模塊完成連續相位FSK調制,同時將原始數據流送至CRD500開發板上擴展口的第10腳,便于用示波器測試。FSK調制模塊對接收到的原始數據進行FSK調制。調制度為3.5,載波頻率為3MHz,則碼元0對應的頻率為3M-3.5/2*390.625k=2.31640625MHz, 碼元1對應的頻率為3M+3.5/2*390.625k=3.68359375MHz。

調制后的數據經CRD500的DA/濾波/運放電路轉換成模似信號經跳線送出;采用短接帽將調制后的模擬信號送至CRD500的AD采樣電路,轉換成數字信號后送至FPGA處理;FSK解調模塊完成FSK信號解調,并將解調出的數據送至擴展口的第11腳。

解調判決后的數據送至位同步模塊提取位同步信號,將提取出的位同步信號送至擴展口的第13腳輸出。為真實驗證FSK通信功能,發送端(pcm.v和fsk_mod.v)的時鐘由CRD500開發板上的X1晶振驅動,接收端(fsk_demod.v)的時鐘由X2晶振驅動。

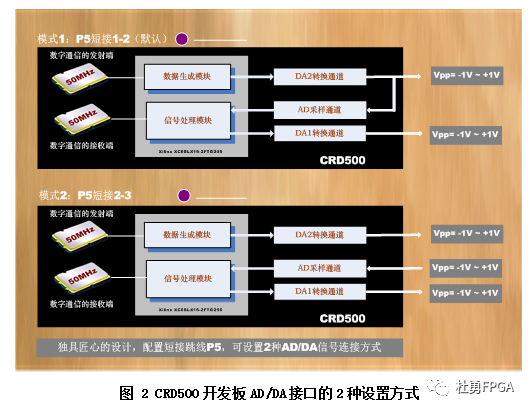

CRD500板上AD/DA接口有多種設置方式,如圖2所示。

本次工程實例采用圖2中的模式1連接方式。如果采用圖2中的第2種模式,則需要采用雙頭BNC線將AD接口與DA接口連接起來。

審核編輯:劉清

-

FPGA

+關注

關注

1643文章

21974瀏覽量

614362 -

鎖相環

+關注

關注

35文章

594瀏覽量

88490 -

數字信號處理

+關注

關注

16文章

567瀏覽量

46563 -

FSK

+關注

關注

14文章

115瀏覽量

58965

原文標題:FSK調制解調(Quartus/Verilog/CRD500)

文章出處:【微信號:杜勇FPGA,微信公眾號:杜勇FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于MSP430的FSK調制解調器

關于fsk調制解調原理的一些困惑

Quartus II平臺下實現全數字FSK調制解調器

采用C54 DSP的FSK調制解調的實現

FSK調制解調方法簡析

FSK調制解調方法簡析

評論