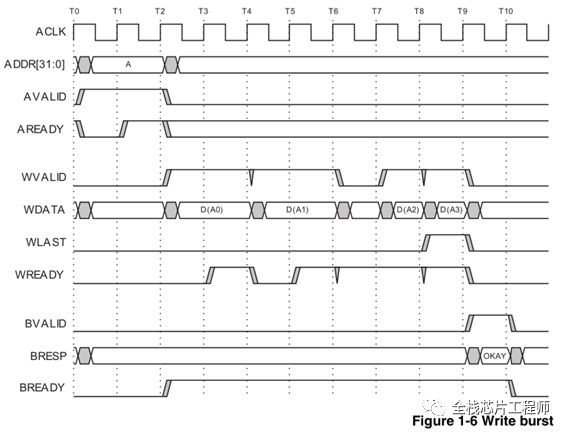

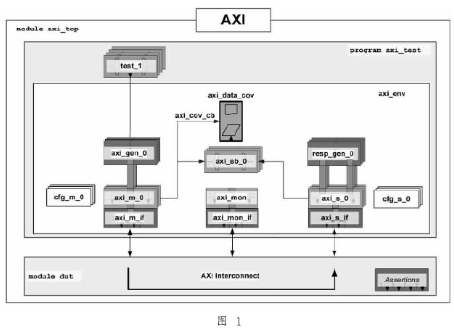

生成的IIP代碼用AMBA VIP進(jìn)行仿真,發(fā)現(xiàn)突發(fā)寫應(yīng)答不符合協(xié)議,按照協(xié)議,突發(fā)寫只需要在寫完成后,回復(fù)一個應(yīng)答信號即可。

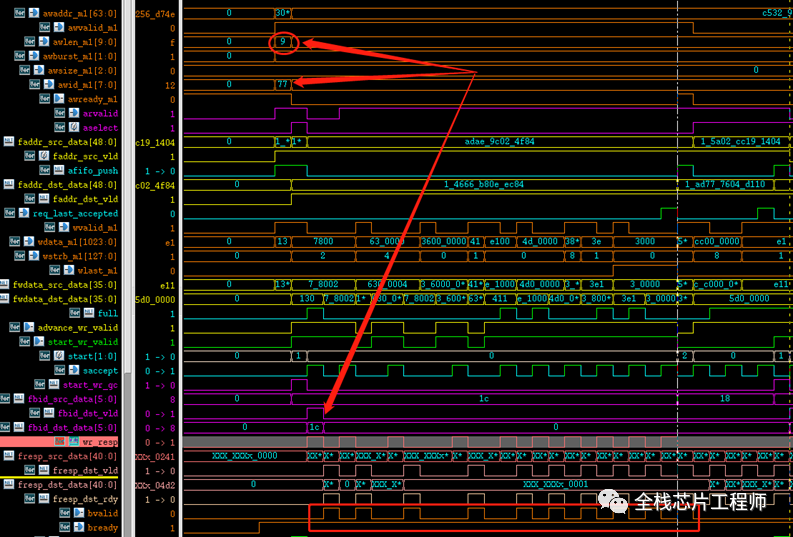

而波形是burst每個寫操作響應(yīng)通道都在應(yīng)答,且只有第一個應(yīng)答有正確的ID。

可以看到仿真波形是burst寫期間,寫通道一直在回復(fù)bvalid,而且只有第一個回復(fù)的ID是正確的,原因是每寫一次resp_fifo就會把bid_fifo的值給清掉。

我們應(yīng)該改成最后一次寫wlast時,才清掉bid_fifo并同時給一次resp信號即可。

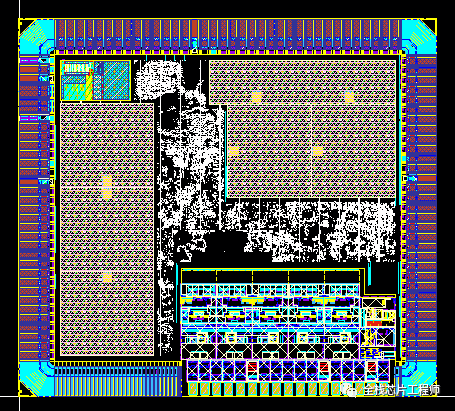

實戰(zhàn)MCU+ISP圖像處理芯片版圖

實戰(zhàn)ISP圖像算法效果

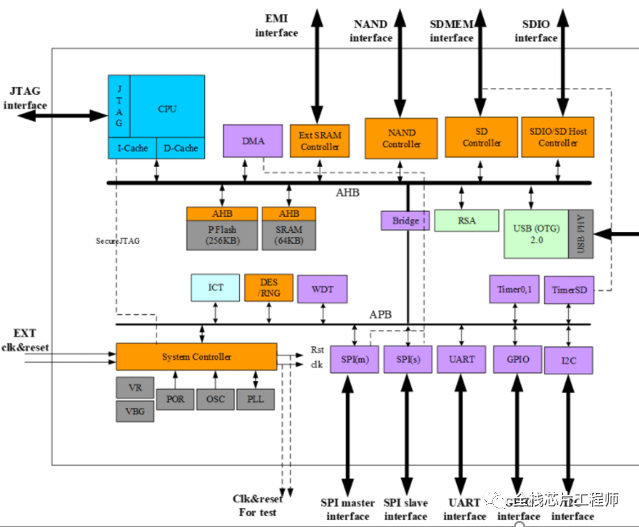

以項目驅(qū)動的方式介紹MCU芯片全流程設(shè)計的方法;

審核編輯:劉清

-

FIFO芯片

+關(guān)注

關(guān)注

0文章

10瀏覽量

8963 -

AMBA

+關(guān)注

關(guān)注

0文章

70瀏覽量

15308 -

axi協(xié)議

+關(guān)注

關(guān)注

0文章

8瀏覽量

2235

原文標(biāo)題:AXI IIP突發(fā)寫的bug定位

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

玩轉(zhuǎn)Zynq連載3——AXI總線協(xié)議介紹1

Vivado中AXI互連的突發(fā)模式

高級可擴(kuò)展接口(AXI)簡介

ARM系列 -- AXI協(xié)議資料匯總(一)

AXI接口協(xié)議詳解

看看Axi4寫通道decoder的設(shè)計

AXI 總線和引腳的介紹

AXI-4 Lite接口協(xié)議仿真波形解析

AXI4接口協(xié)議的基礎(chǔ)知識

高級可擴(kuò)展接口(AXI)簡介

AXI IIP突發(fā)寫的bug定位如何解決?

AXI IIP突發(fā)寫的bug定位如何解決?

評論