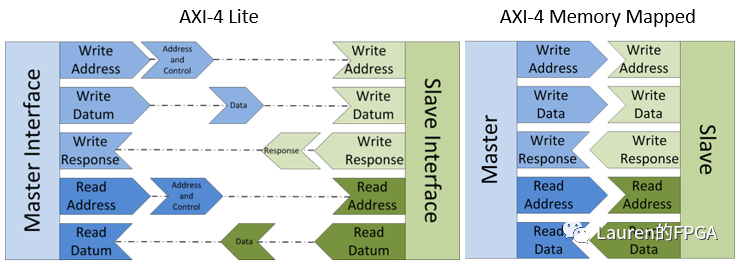

AXI-4 Lite可以看作是AXI-4 Memory Mapped的子集,從下面的示例圖中就可見一斑。最直接的體現是AXI-4 Lite的突發長度是固定值1。

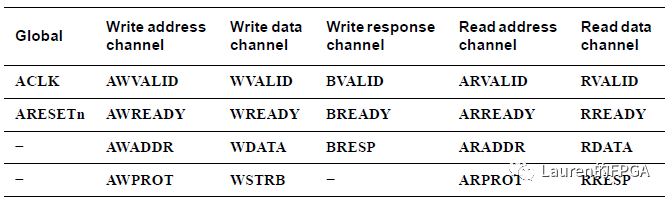

AXI-4 Lite的接口信號如下圖所示。同樣都是5個獨立通道,但由于突發長度被限制為1,使得某些信號不再需要,例如ARLEN和AWLEN就不再需要了,因為兩者均為0,同時用于顯示突發類型(Burst Type)的ARBURST和AWBURST、表明一筆數據交易的最后一個有效數據WLAST和RLAST均不再需要了。此外,AXI-4 Lite要求數據位寬必須是32-bit或64-bit,故ARSIZE和AWSIZE也不再需要了。

就數據傳輸機制而言,AXI-4 Lite和AXI-4 Memory Mapped是一致的,每個通道都有相應的VALID和READY信號對。

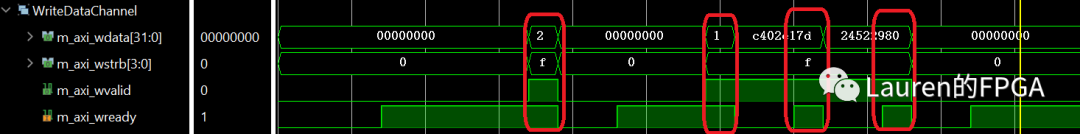

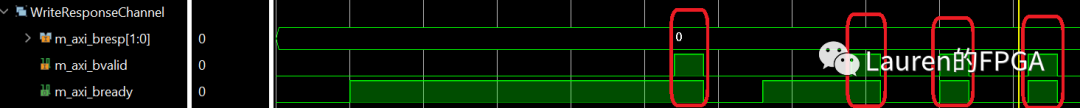

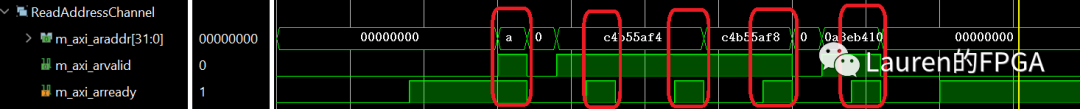

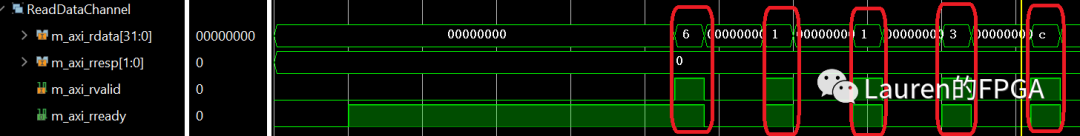

這里我們給出一個仿真波形供大家參考,以便理解AXI-4 Lite接口協議。

寫地址通道

寫數據通道

寫響應通道

讀地址通道

讀數據通道

-

接口協議

+關注

關注

5文章

41瀏覽量

18808

原文標題:AXI-4 Lite與AXI-4 Memory Mapped接口協議有什么區別?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Zynq中AXI4-Lite和AXI-Stream功能介紹

AXI VIP設計示例 AXI接口傳輸分析

XADC和AXI4Lite接口:定制AXI引腳

請問AXI-4流接口有沒有可用的地址線?

AXI4-lite端口可以保持未連接狀態嗎?

AXI接口協議詳解

AMBA 4 AXI4、AXI4-Lite和AXI4-流協議斷言用戶指南

AXI4 、 AXI4-Lite 、AXI4-Stream接口

如何在Vitis HLS中使用C語言代碼創建AXI4-Lite接口

自定義AXI-Lite接口的IP及源碼分析

AXI-4 Lite接口協議仿真波形解析

AXI-4 Lite接口協議仿真波形解析

評論