Zynq中AXI4-Lite功能

AXI4-Lite接口是AXI4的子集,專用于和元器件內的控制寄存器進行通信。AXI-Lite允許構建簡單的元件接口。這個接口規模較小,對設計和驗證方面的要求更少。AXI4-Lite接口的特性如下:

1) 突發長度為1。

2) 所有訪問數據的寬度和數據總線寬度相同。

3) 支持數據總線寬度為32位或64位。

4) 所有的訪問相當于AWCACHE和ARCACHE等于b0000(非緩沖和非緩存)。

5) 不支持互斥性操作。

Zynq中AXI-Stream功能

AXI-Stream協議作為一個標準接口,用于連接數據交換元件。接口將產生數據的一個主設備和接收數據的一個從設備連接。當很多元件和從元件連接時,也能使用該協議。協議支持使用具有相同設置共享總線的多個數據流。該協議允許建立一個互聯結構。

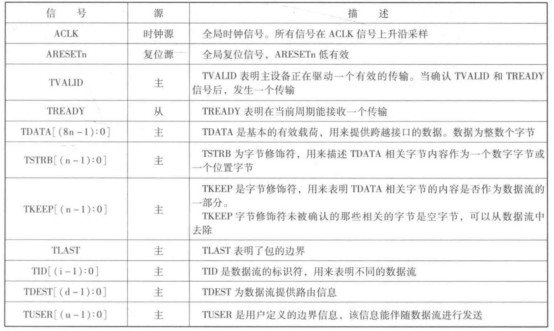

接口描述如下:

TVALID和TREADY握手信號用來確定跨接口數據的時間。雙向的流控制機制使得主設備和從設備能夠控制跨接口所發送的數據和控制信息的速度

一個主設備不允許在確認TVALID前,等待確認TREADY。一旦確認TVALID,必須一致保持這個狀態,知道產生握手信號。

在確認相應的TREADY信號前,一個從設備允許等待確認TVALID。

如果從設備確認了TREADY,在TVALID信號確認前,允許不確認TREADY。

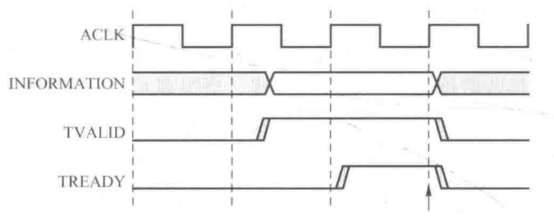

1. TVALID在TREADY前的握手信號

上圖給出了TVALID在TREADY前的握手信號,從圖中可以看出,主設備給出數據和控制信號,并且確認TVALID信號為高。一旦主設備確認了VALID,來自主設備的數據或從設備控制信息保持不變。這種狀態一直保持到從設備驅動TREADY信號為高位置,它用來表示從設備可以接收數據和控制信號。在這種情況下,一旦從設備確認TREADY為高,則開始進行傳輸。

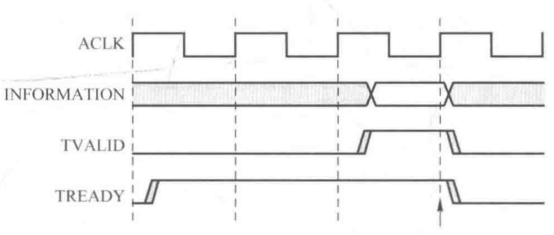

2. TREAD在TVALID之前的握手信號

上圖給出了TREADY在TVALID前的握手信號,從圖中可以看出,在數據和控制信息有效前,從設備驅動TREADY信號為高。這表示,從設備可以在一個ACLK周期內接收數據和控制信息。在這種情況下,一旦主機確認TVALID信號為高,則開始傳輸。

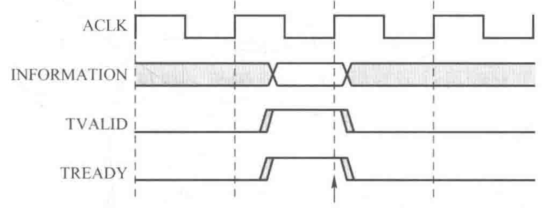

3. TVALID和TREADY握手

上圖給出了TVALID和TREADY握手的圖,在ACLK一個周期內,主設備確認TVALID為高,從設備確認TREADY為高,則開始傳輸。

本文轉自: 瓜大三哥,作者:米果不回來

-

Zynq

+關注

關注

10文章

615瀏覽量

48263 -

AXI

+關注

關注

1文章

136瀏覽量

17265 -

AXI4

+關注

關注

0文章

20瀏覽量

9060 -

控制寄存器

+關注

關注

0文章

34瀏覽量

11654

發布評論請先 登錄

Xilinx zynq AXI總線全面解讀

請問可以使用AXI-Stream Broadcaster作為AXI開關嗎?

AXI4-lite端口可以保持未連接狀態嗎?

AXI-stream數據傳輸過程

AXI-Stream代碼

關于AXI4-Stream協議總結分享

AXI4 、 AXI4-Lite 、AXI4-Stream接口

如何在Vitis HLS中使用C語言代碼創建AXI4-Lite接口

使用AXI4-Lite將Vitis HLS創建的IP連接到PS

Xilinx FPGA AXI4總線(一)介紹【AXI4】【AXI4-Lite】【AXI-Stream】

自定義AXI-Lite接口的IP及源碼分析

Zynq中AXI4-Lite和AXI-Stream功能介紹

Zynq中AXI4-Lite和AXI-Stream功能介紹

評論