以AXI4為例,有AXI full/lite/stream之分。

在Xilinx系列FPGA及其有關IP核中,經常見到AXI總線接口,AXI總線又分為三種:

?AXI-Lite,AXI-Full以及AXI-Stream,其中AXI-Lite和AXI-Full都是基于memory map的形式實現數據傳輸(即包括地址總線),而AXI-Stream是以數據流的形式傳輸,無地址。

?其中AXI-Lite是AXI-Full的簡化版,適合小批量的數據傳輸,常用來進行命令的傳輸,IP核的初始化等。

?AXI-Full則適用于大批量,高性能的數據傳輸。

AXI是一種用于傳輸數據的模塊或總線,用于兩個模塊或多個模塊之間相互傳遞數據。它本身有很多優點,被SOC廣泛采用了。

AXI傳輸數據的過程

AXI-full傳輸數據是全雙工的,也就是說,讀寫是同時進行的。

一條AXI總線有5條通道,兩個用于讀,三個用于寫。

首先描述一下AXI的寫數據過程:

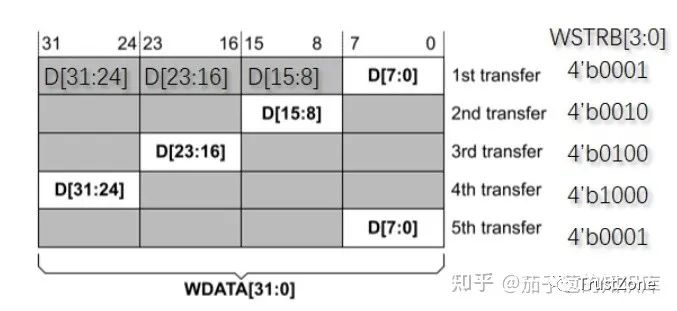

(1)Master主機通過寫地址通道將地址傳給Slave從機,從機收到地址可通過寫數據通道往里送入數據,寫完之后通過寫回應通道給主機一個結束信號。

(注:寫回應通道只需2個bit位就能代表四種狀態,傳成功了,傳失敗的幾種狀態)

(注:寫回復是針對整個傳輸操作(transcaction)的,而不是針對每個寫入數據(data transfer))。

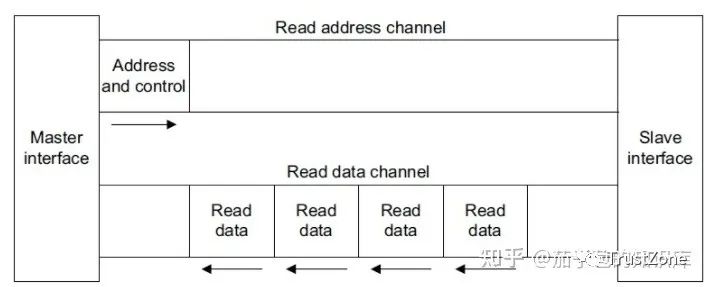

AXI讀數據的過程:

主機給從機一個地址,從機通過讀數據通道給主機返回數據。

為什么讀只需要兩個通道?因為完成信號可以用讀數據傳輸一并傳輸。

-

模塊

+關注

關注

7文章

2784瀏覽量

49750 -

數據傳輸

+關注

關注

9文章

2005瀏覽量

65764 -

總線

+關注

關注

10文章

2953瀏覽量

89409 -

AXI

+關注

關注

1文章

134瀏覽量

17125

發布評論請先 登錄

Xilinx zynq AXI總線全面解讀

AXI VIP設計示例 AXI接口傳輸分析

NVMe IP之AXI4總線分析

AXI流數據包傳輸問題

AXI-stream數據傳輸過程

ARM系列 -- AXI協議資料匯總(一)

AXI接口協議詳解

AXI接口協議詳解

ZYNQ的ARM和FPGA數據交互——AXI交互最重要的細節

你必須了解的AXI總線詳解

AXI傳輸數據的過程

AXI傳輸數據的過程

評論