Zynq中AXI4-Lite功能 AXI4-Lite接口是AXI4的子集,專用于和元器件內的控制寄存器進行通信。AXI-Lite允許構建簡單的元件接口。這個接口規模較小,對設計和驗證方面的要求更少

2020-09-27 11:33:02 8050

8050

,是面向地址映射的接口,允許最大256輪的數據突發傳輸; (B)AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一個輕量級的地址映射單次傳輸接口,占用很少的邏輯單元。 (C)AXI4-Stream:(F

2020-12-04 12:22:44 6179

6179

前面一節我們學會了創建基于AXI總線的IP,但是對于AXI協議各信號的時序還不太了解。這個實驗就是通過SDK和Vivado聯合調試觀察AXI總線的信號。由于我們創建的接口是基于AXI_Lite協議

2020-12-23 15:32:37 2169

2169 一、AXI DMA介紹 本篇博文講述AXI DMA的一些使用總結,硬件IP子系統搭建與SDK C代碼封裝參考米聯客ZYNQ教程。若想讓ZYNQ的PS與PL兩部分高速數據傳輸,需要利用PS的HP

2020-12-31 09:52:02 7165

7165

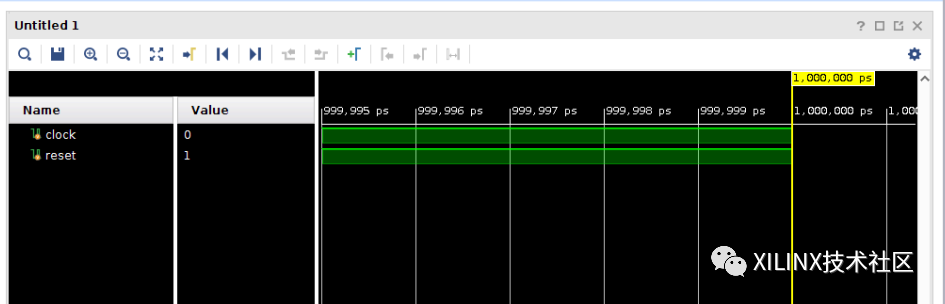

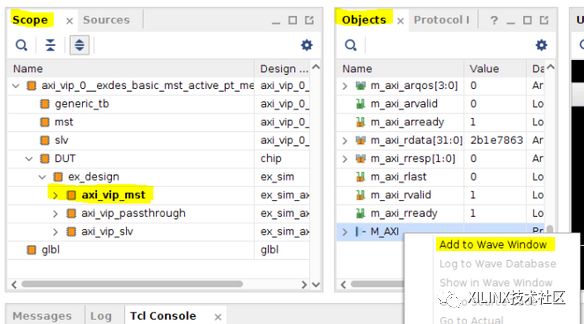

在這篇新博文中,我們來聊一聊如何將 AXI VIP 添加到 Vivado 工程中,并對 AXI4-Lite 接口進行仿真。隨后,我們將在仿真波形窗口中講解用于AXI4-Lite 傳輸事務的信號。

2022-07-08 09:27:14 1660

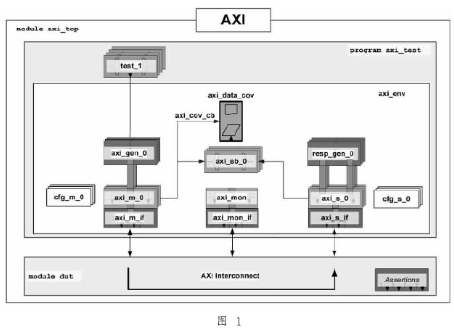

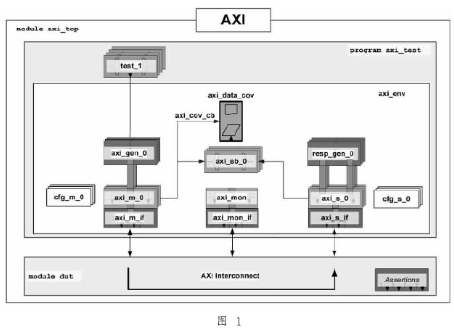

1660 在 AXI 基礎第 2 講 一文中,曾提到賽靈思 Verification IP (AXI VIP) 可用作為 AXI 協議檢查工具。在本次第4講中,我們將來了解下如何使用它在 AXI4 (Full) 主接口中執行驗證(和查找錯誤)。

2022-07-08 09:31:38 1944

1944 在某些情況下,通過嗅探 AXI 接口來分析其中正在發生的傳輸事務是很有用的。在本文中,我將為大家演示如何創建基本 AXI4-Lite Sniffer IP 以對特定地址上正在發生的讀寫傳輸事務進行計數。

2022-07-08 09:35:34 775

775 MPSoC有六個PL側高性能(HP)AXI主接口連接到PS側的FPD(PL-FPD AXI Masters),可以訪問PS側的所有從設備。這些高帶寬的接口主要用于訪問DDR內存。有四個HP AXI

2022-07-22 09:25:24 2501

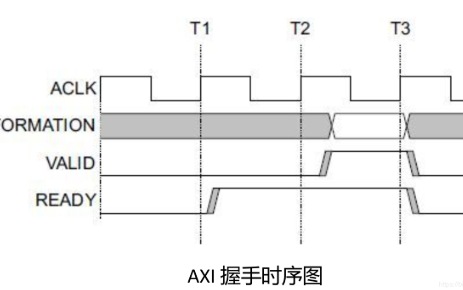

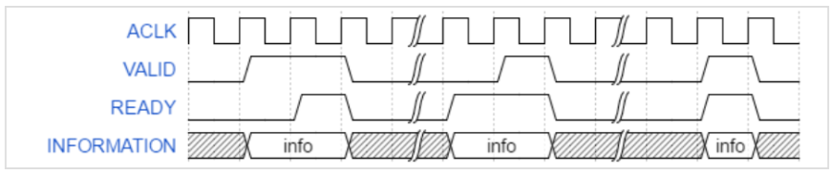

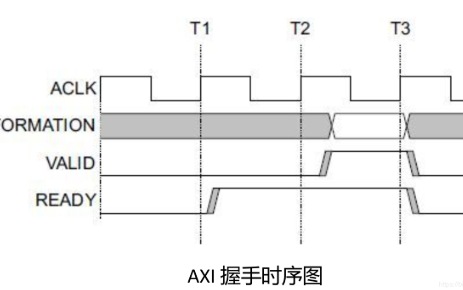

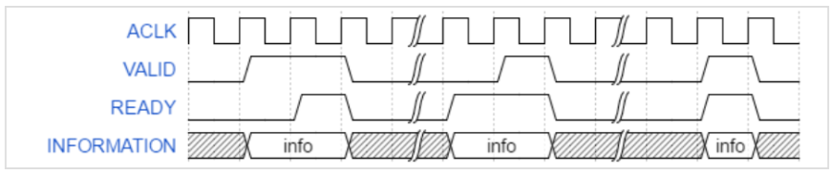

2501 由于ZYNQ架構和常用接口IP核經常出現 AXI協議,賽靈思的協議手冊講解時序比較分散。所以筆者收藏AXI協議的幾種時序,方便編程。

2022-08-02 12:42:17 6661

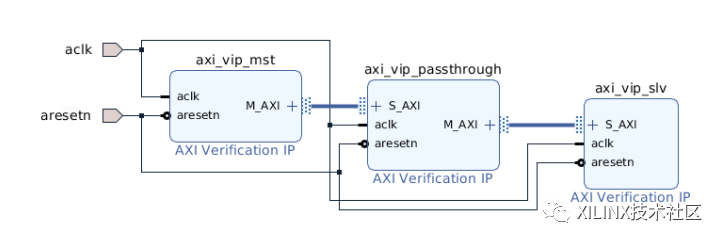

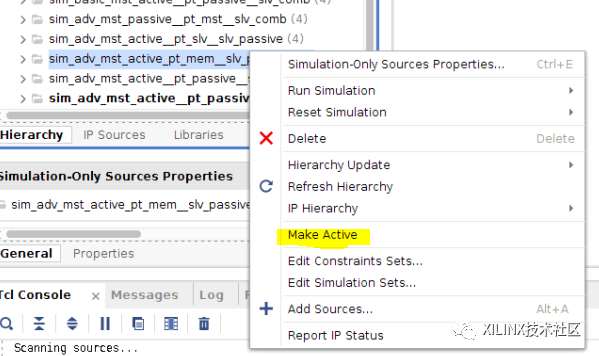

6661 ??AXI接口雖然經常使用,很多同學可能并不清楚Vivado里面也集成了AXI的Verification IP,可以當做AXI的master、pass through和slave,本次內容我們看下

2023-07-27 09:19:33 633

633

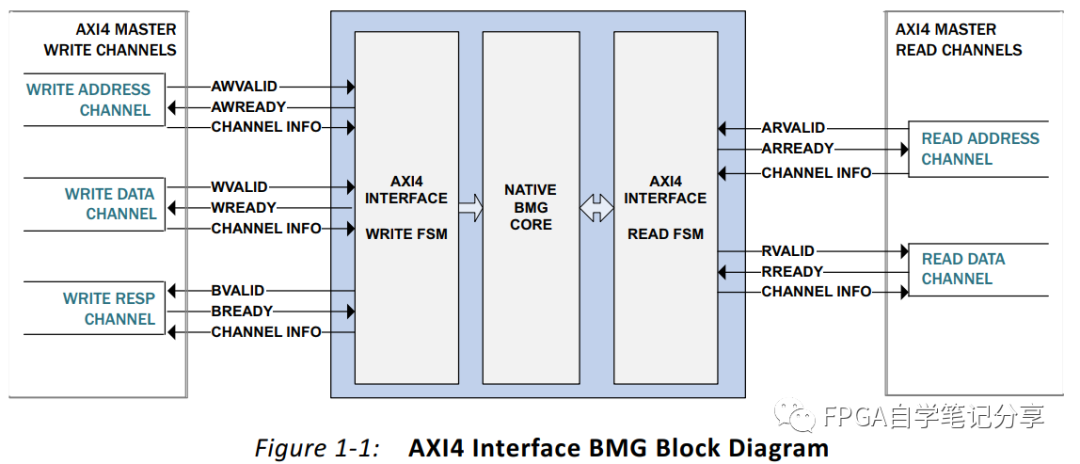

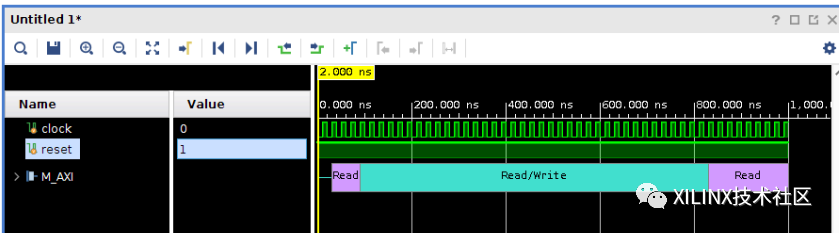

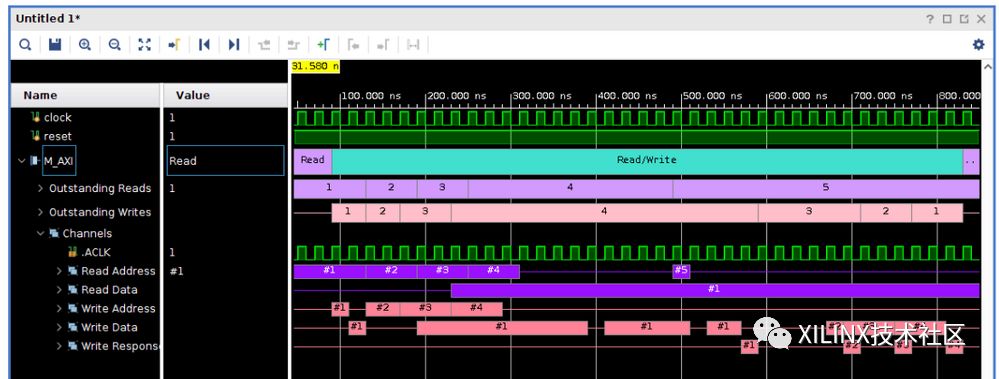

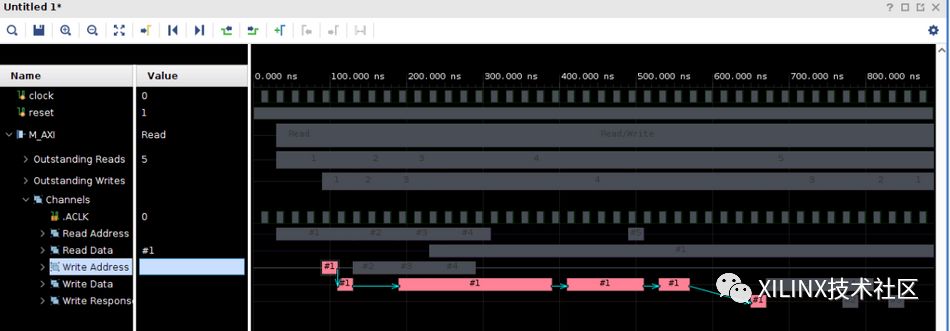

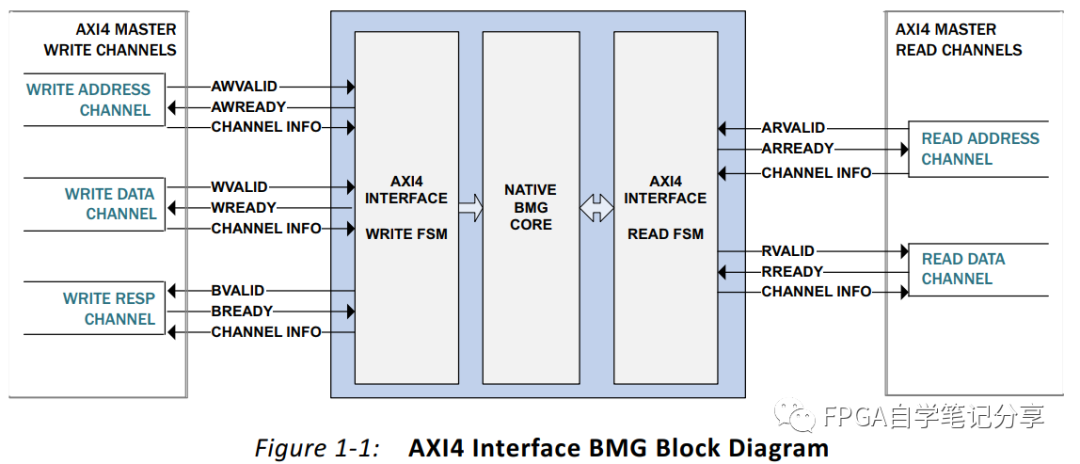

之前的文章對Block Memory Generator的原生接口做了說明和仿真,本文對AXI接口進行說明。

2023-11-14 18:25:10 685

685

AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互連以及其他AXI4系統外設上生成特定序列(流量)。它根據IP的編程和選擇的操作模式生成各種類型的AXI事務。是一個比較好用的AXI4協議測試源或者AXI外設的初始化配置接口。

2023-11-23 16:03:45 580

580

首先我們看一下針對AXI接口的IP設計,在介紹之前我們先回顧一下AXI所具有的一些feature。

2024-02-20 17:12:56 518

518

AXI Stream FIFO傳輸的數據TX Stream Control Data – 此接口支持 AXI 以太網 IP 內核的傳輸協議AXI Lite – 用于訪問配置寄存器和數據 Tx 和 Rx

2022-11-04 11:03:18

AXI4-Stream跟AXI4的區別在于AXI4-Stream沒有ADDR接口,這樣就不涉及讀寫數據的概念了,只有簡單的發送與接收說法,減少了延時,允許無限制的數據突發傳輸規模

2021-01-08 16:52:32

我必須通過AXI4-lite接口配置Jesd204b核心,或者我可以簡單地將AXI4-lite端口保持未連接狀態(強制接地)?Jesd204核心示例top沒有提供有關AXI4-Lite端口配置的指導。

2020-05-15 09:30:54

應該與最低有效像素位置對齊。同樣,如果每個器件只有8位通過為每個器件產生的10位接口傳輸,則有效位應MSB對齊,LSB用零填充。Figure 1-6 和 Figure 1-9中顯示了三個示例。重要提示

2022-11-14 15:15:13

4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允許最大256輪的數據突發傳輸;AXI

2022-04-08 10:45:31

突發傳輸; AXI4-Lite:(For simple, low-throughput memory-mapped communication)是一個輕量級的地址映射單次傳輸接口,占用很少的邏輯單元

2022-10-14 15:31:40

AXI總線學習AXI協議的主要特征主要結構通道定義讀寫地址通道讀數據通道寫數據通道寫操作回應信號接口和互聯寄存器片基本傳輸Read burstOverlapping read burstWrite

2022-02-09 07:17:23

。

?適用于具有高初始訪問延遲的內存控制器。

?提供了實現互連架構的靈活性。

?向后兼容AHB和APB接口。

AXI協議的主要特點是:

?獨立的地址/控制和數據階段。

?支持使用字節選通進行未對齊的數據傳輸

2023-08-02 09:44:08

本文介紹了AMBA3.0AXI的結構和特點,分析了新的AMBA3.0AXI協議相對于AMBA2.0的優點。它將革新未來高性能SOC總線互連技術,其特點使它更加適合未來的高性能、低延遲設計。最后介紹了基于AXI協議的設計實例,探討了利用IP復用技術和DesginWareIP搭建基于AXI協議的SOC系統。

2023-09-20 08:30:25

為主。AXI 的全稱是 Advanced eXtensible Interface。在 spec 里面是這么自夸的:用于高帶寬和低延遲設計。提供高頻操作,無需使用復雜電橋。協議滿足各種組件的接口要求

2022-04-08 09:34:43

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2021-02-02 07:30:07

你好,我有一個關于XADC及其AXI4Lite接口輸入的問題。我想在Microzed 7020主板上測試XADC,在通過AXI4Lite接口將Zynq PL連接到XADC向導(參見第一個附件)之后

2018-11-01 16:07:36

memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允許最大256輪的數據突發傳輸;AXI4-Lite:(For simple

2018-01-08 15:44:39

大部分器件的接口要求,提供互聯架構的靈活性與獨立性。

(1)AXI總線

總線是一組傳輸通道,是各種邏輯器件構成的傳輸數據的通道,一般由數據線、地址線、控制線等構成。在ZYNQ中支持三種AXI總線

2023-11-03 10:51:39

你好!如果我想使用vivado hls來合成具有axi流接口的代碼,是否有必須遵循的標準編碼風格?

2020-04-21 10:23:47

數據傳輸量,突發長度,延遲,和總線事務。它有助于用戶在設計初期對AXI總線的瓶頸進行分析。 VARONIP包括可配置的主站或從站IP,提供可合成的FPGA IP。這使得將AXI總線作為硬件實現起來很容易

2020-11-02 16:54:39

請問在開源的E203的AXI總線支持burst傳輸嗎?在sirv_gnrl_icb2axi.v模塊中看到了

請問如何使用呢?相應的在NucleiStudio中的代碼中需要做什么修改呢?有大佬指點一下想要使用AXI做burst傳輸具體需要做那些步驟呢?

2023-08-12 06:13:08

嗨,大家好,我目前正在創建一個PCIe接口卡,我正處于項目的調試階段。我試圖監視用戶_clkrate的AXI突發。關于ILA核心和PCIe端點(在VC709上)我有一些問題。1.當我嘗試將

2019-09-25 09:26:14

使用Vivado生成AXI VIP(AXI Verification IP)來對自己設計的AXI接口模塊進行全方位的驗證(如使用VIP的Master、Passthrough、Slave三種模式對自己寫的AXI

2022-10-09 16:08:45

我有一個simpleregister讀/寫/重置測試接口代碼(在VHDL中),我想與我的頂級處理系統7wrapper代碼鏈接。我想使用AXI總線協議對寄存器進行讀/寫/復位。實際上,我的測試接口

2019-09-09 10:03:44

大家好,我正在使用zedboard創建一個AXI接口應用程序,以突發模式從ARM發送64字節數據到FPGA。為此,我在vivado中創建了一個自定義AXI從站,選擇它作為AXI FULL(因為AXI

2020-08-12 10:37:46

本指南介紹了高級微控制器總線體系結構(AMBA)AXI的主要功能。

該指南解釋了幫助您實現AXI協議的關鍵概念和細節。

在本指南中,我們介紹:

?AMBA是什么。

?為什么AMBA在現代SoC設計中

2023-08-09 07:37:45

PuTTY,設定好串口號和波特率115200,可以看到不斷的打印如下的信息。若希望使用在線邏輯分析儀對AXI GP總線接口波形進行觀察,可以參考文檔《玩轉Zynq-工具篇:基于Vivado的在線邏輯

2019-11-12 10:23:42

嗨,我在Vivado 2016.3模塊設計中集成了PCIe DMA BAR0 AXI Lite接口和AXI IIC IP。在DMA IP端,它顯示S_AXI_Lite端口,但在AXI_IIC IP端

2020-05-14 09:09:35

本文將討論AMBA的第三次修訂版,該修訂版向世界介紹了高級可擴展接口(AXI)協議。AXI協議最初是為高頻系統而設計的,旨在滿足各種組件的接口要求,同時允許靈活地互連這些組件。適用于高頻,低延遲

2020-09-28 10:14:14

AXI Reference Guide (AXI).pdf

2012-12-23 16:41:36 55

55 AMBA AXI 總線學習筆記,非常詳細的AXI總線操作說明

2015-11-11 16:49:33 11

11 streaming接口。Vivado工具的AXI參考手冊(用戶手冊1037)對我們是非常有幫助的,提供了關于Zynq SoC的AXI協議的詳細信息,為了構建硬件我們將使用如下AXI協議

2017-02-08 08:10:39 286

286 本節介紹的AXI是個什么東西呢,它其實不屬于Zynq,不屬于Xilinx,而是屬于ARM。它是ARM最新的總線接口,以前叫做AMBA,從3.0以后就稱為AXI了。 書上講的AXI比較具體,本節呢不打算落入俗套,從應用角度解釋AXI。

2018-07-13 07:08:00 10226

10226

本文主要介紹zynq linux AXI DMA傳輸步驟教程,具體的跟隨小編一起來了解一下。

2018-07-08 05:46:00 29549

29549

本文包含兩部分內容:1)AXI接口簡介;2)AXI IP核的創建流程及讀寫邏輯分析。 1AXI簡介(本部分內容參考官網資料翻譯) 自定義IP核是Zynq學習與開發中的難點,AXI IP核又是十分常用

2018-06-29 09:33:00 14957

14957

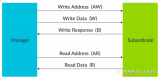

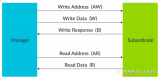

1、AXI 總線通道,總線和引腳的介紹 AXI接口具有五個獨立的通道: (1)寫地址通道(AW):write address channel (2)寫數據通道( W): write data

2018-01-05 08:13:47 9601

9601

了解如何使用Xilinx AXI驗證IP有效驗證和調試AXI接口。

該視頻回顧了使用的好處,以及如何使用示例設計進行模擬。

2018-11-20 06:38:00 3561

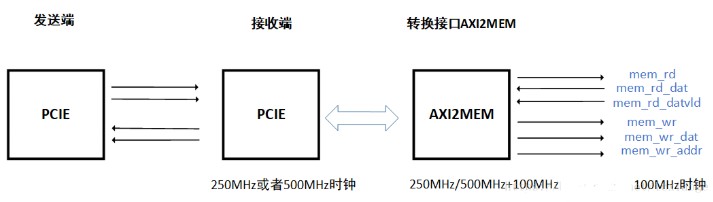

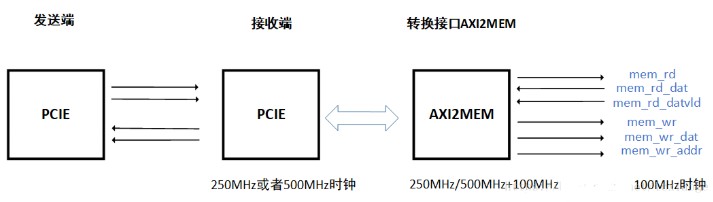

3561 AXI2MEM轉換接口需要將來自PCIE的AXI信號(時鐘為250MHz或者500MHz)轉換成100MHz時鐘的MEM接口。MEM接口用于SOC總線主端口,用于讀寫芯片內部模塊或者配置寄存器。

2019-05-12 09:19:31 2243

2243

由于ZYNQ架構和常用接口IP核經常出現 AXI協議,賽靈思的協議手冊講解時序比較分散。所以筆者收藏AXI協議的幾種時序,方便編程。

2019-05-12 09:10:33 10860

10860

如何設計高效的 PL 和 PS 數據交互通路是 ZYNQ 芯片設計的重中之重。AXI 全稱 Advanced eXtensible Interface,是 Xilinx 從 6 系列的 FPGA 開始引入的一個接口協議,主要描述了主設備和從設備之間的數據傳輸方式。

2020-03-15 17:04:00 10317

10317

這將創建一個附帶 BD 的 Vivado 工程,此 BD 包含 AXI VIP (設置為 AXI4-Lite 主接口) 和 AXI GPIO IP。這與我們在 AXI 基礎第 3 講一文 中完成的最終設計十分相似。

2020-04-30 16:24:50 2068

2068

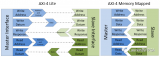

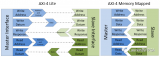

AXI-4 Lite可以看作是AXI-4 Memory Mapped的子集,從下面的示例圖中就可見一斑。最直接的體現是AXI-4 Lite的突發長度是固定值1。

2020-09-23 11:18:06 3113

3113

AXI-4 Memory Mapped也被稱之為AXI-4 Full,它是AXI4接口協議的基礎,其他AXI4接口是該接口的變形。總體而言,AXI-4 Memory Mapped由五個通道構成,如下圖所示:寫地址通道、寫數據通道、寫響應通道、讀地址通道和讀數據通道。

2020-09-23 11:20:23 5453

5453

AXI全稱Advanced eXtensibleInterface,是Xilinx從6系列的FPGA開始引入的一種接口協議,主要描述了主設備和從設備之間的數據傳輸方式。

2020-09-23 11:22:41 4128

4128

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現,不能直接和PS相連,必須通過AXI

2020-09-24 09:50:30 4289

4289

M_AXI接口對數據進行讀取操作,此時設計一個基于AXI-Slave接口的IP進行數據傳輸操作就非常的方便。 封裝的形式并不復雜,只是略微繁瑣,接下來一步一步演示如何封裝AXI_SLAVE接口IP

2020-10-30 12:32:37 3953

3953

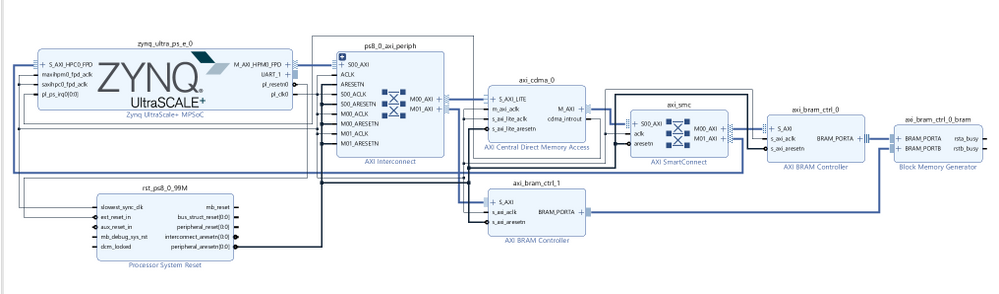

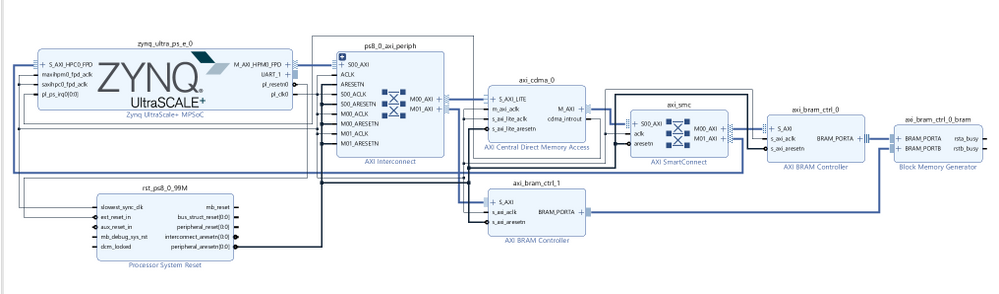

本篇博文將為您演示如何創建 AXI CDMA Linux 用戶空間示例應用。 示例設計將在 Zynq UltraScale+ RFSoC ZCU111 評估板上實現通過 AXI CDMA 把數據

2020-09-28 15:31:06 2259

2259

引言 近來,幾乎每個賽靈思 IP 都使用 AXI 接口。Zynq、Zynq MP、MicroBlaze 和全新的 Versal 處理器都無一例外使用 AXI 接口。因此,AXI 接口已成為幾乎所有

2020-09-27 11:06:45 5857

5857

本文將討論AMBA的第三次修訂版,該修訂版向世界介紹了高級可擴展接口(AXI)協議。AXI協議最初是為高頻系統而設計的,旨在滿足各種組件的接口要求,同時允許靈活地互連這些組件。適用于高頻,低延遲

2020-09-29 11:44:22 5425

5425

DMA的總結 ZYNQ中不同應用的DMA 幾個常用的 AXI 接口 IP 的功能(上面已經提到): AXI-DMA:實現從 PS 內存到 PL 高速傳輸高速通道 AXI-HP----AXI

2020-10-09 18:05:57 6391

6391

和接口的構架 在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三種總線,但PS與PL之間的接口卻只支持前兩種,AXI-Stream只能在PL中實現,不能直接和PS相連,必須通過

2020-11-02 11:27:51 3880

3880

AXI-Stream代碼詳解 AXI4-Stream跟AXI4的區別在于AXI4-Stream沒有ADDR接口,這樣就不涉及讀寫數據的概念了,只有簡單的發送與接收說法,減少了延時,允許無限制的數據

2020-11-05 17:40:36 2826

2826

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2022-07-25 17:41:58 2046

2046

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

2021-01-31 06:50:04 12

12 在 AMBA 系列之 AXI 總線協議初探 中,了解到 AXI 總線交互分為 Master / Slave 兩端,而且標準的 AXI 總線支持不同的位寬,既然是總線,那么必須要支持總線互聯,多 Master,多 Slave的場景

2021-02-23 06:57:00 45

45 AXI是個什么東西呢,它其實不屬于Zynq,不屬于Xilinx,而是屬于ARM。它是ARM最新的總線接口,以前叫做AMBA,從3.0以后就稱為AXI了。

2021-04-09 17:10:10 4970

4970

本文介紹了AMBA 3.0 AXI的結構和特點,分析了新的AMBA 3.0 AXI協議相對于AMBA 2. 0的優點。它將革新未來高性能SOC總線互連技術,其特點使它更加適合未來的高性能、低延遲

2021-04-12 15:47:39 28

28 ,它使用通用的AXI4接口在系統中移動或轉換數據,而不解釋數據。 這些基礎的IP各自有自己的常用的功能,下面列舉出一部分AXI接口的基礎構架IP。 ° AXI Register slices

2021-05-11 14:52:55 5612

5612

AXI總線學習AXI協議的主要特征主要結構通道定義讀寫地址通道讀數據通道寫數據通道寫操作回應信號接口和互聯寄存器片基本傳輸Read burstOverlapping read burstWrite

2021-12-05 16:21:03 5

5 uart2axi_master_intf程序源碼:/**************************************************** Module Name

2021-12-28 20:04:42 14

14 學習關于ZYNQ IP核中的GP接口和HP接口的異同,介紹關于AXI_GP接口和AXI_HP接口的相關內容。

2022-07-03 14:17:34 1880

1880 AXI4 是一種高性能memory-mapped總線,AXI4-Lite是一只簡單的、低通量的memory-mapped 總線,而 AXI4-Stream 可以傳輸高速數據流。從字面意思去理解

2022-07-04 09:40:14 5818

5818 前面簡單學習了關于GPIO的操作,本次將使用PL 端調用 AXI GPIO IP 核, 并通過 AXI4-Lite 接口實現 PS 與 PL 中 AXI GPIO 模塊的通信。

2022-07-19 17:36:52 3228

3228 本文主要介紹了AXI通道以及在每個通道下信號的概述。

2022-08-04 10:49:17 9635

9635 本系列我想深入探尋 AXI4 總線。不過事情總是這樣,不能我說想深入就深入。當前我對 AXI總線的理解尚談不上深入。但我希望通過一系列文章,讓讀者能和我一起深入探尋 AXI4。

2022-08-29 14:58:44 1272

1272 使用Vivado生成AXI VIP(AXI Verification IP)來對自己設計的AXI接口模塊進行全方位的驗證(如使用VIP的Master、Passthrough、Slave三種模式對自己寫的AXI

2022-10-08 16:07:11 3846

3846 AXI4S攜帶實際的視頻數據(無行場消隱),由主機和從機接口驅動,如Figure 1-1所示。

2022-11-14 09:15:25 815

815 關于VIP的好處,估計就不用我安利了,引用最近S家的一句廣告語,“擁有VIP,無懼芯片設計挑戰”。而在當今的芯片領域,用的最多的可能還是標準總線APB/AHB/AXI等。提到VIP,估計大家最先想到的就是Cadence和Synopsys了。

2022-12-06 14:58:04 1076

1076 上面兩圖的區別是相比AXI3,AXI4協議需要確認AWVALID、AWREADY握手完成才能回復BVALID。為什么呢?

2023-03-30 09:59:49 668

668 AXI 是一種接口規范,它定義了 IP 塊的接口,而不是互連本身。

2023-05-04 09:27:39 703

703

之前文章為大家介紹了AXI的協議與架構,本篇我們接著往下講AXI的讀寫傳輸

內容概括

2023-05-04 14:41:27 1423

1423

AXI 規范描述了兩個接口之間的點對點協議:manager and subordinate接口。

2023-05-05 11:42:40 462

462

上文FPGA IP之AXI4協議1_協議構架對協議框架進行了說明,本文對AXI4接口的信號進行說明。

2023-05-24 15:05:46 842

842

上文FPGA IP之AXI4協議1_信號說明把AXI協議5個通道的接口信息做了說明,本文對上文說的信號進行詳細說明。

2023-05-24 15:06:41 669

669

最近需要用到AXI接口的模塊,xilinx的IP核很多都用到了AXI總線進行數據和指令傳輸。如果有多個設備需要使用AXI協議對AXI接口的BRAM進行讀寫,總線之間該如何進行仲裁,通信?

2023-06-19 15:45:14 4243

4243

從 FPGA 應用角度看看 AMBA 總線中的 AXI4 總線。

2023-06-21 15:21:44 1729

1729

在 Vivado 中自定義 AXI4-Lite 接口的 IP,實現一個簡單的 LED 控制功能,并將其掛載到 AXI Interconnect 總線互聯結構上,通過 ZYNQ 主機控制,后面對 Xilinx 提供的整個 AXI4-Lite 源碼進行分析。

2023-06-25 16:31:25 1913

1913

可以看到,在AXI到UART中,是通過寄存器和FIFO進行中介的。因為從AXI總線往里看,其控制的是就是地址上所映射的寄存器。

2023-06-27 10:12:53 2229

2229

本文將為您演示如何創建?AXI CDMA Linux?用戶空間示例應用

2023-07-07 14:15:03 533

533

?AXI接口雖然經常使用,很多同學可能并不清楚Vivado里面也集成了AXI的Verification IP,可以當做AXI的master、pass through和slave,本次內容我們看下AXI VIP當作master時如何使用。

2023-07-27 09:16:13 792

792

本文開源一個FPGA項目:基于AXI總線的DDR3讀寫。之前的一篇文章介紹了DDR3簡單用戶接口的讀寫方式:《DDR3讀寫測試》,如果在某些項目中,我們需要把DDR掛載到AXI總線上,那就要通過MIG IP核提供的AXI接口來讀寫DDR。

2023-09-01 16:20:37 1896

1896

LogiCORE IP AXI4-Stream FIFO內核允許以內存映射方式訪問一個AXI4-Stream接口。該內核可用于與AXI4-Stream IP接口,類似于LogiCORE IP AXI以太網內核,而無需使用完整的DMA解決方案。

2023-09-25 10:55:33 497

497

Xilinx 從 Spartan-6 和 Virtex-6 器件開始采用高級可擴展接口 (AXI) 協議作為知識產權 (IP) 內核。Xilinx 繼續將 AXI 協議用于針對 7 系列和 Zynq-7000 All Programmable SoC 器件的 IP。

2023-09-27 09:50:27 594

594

LogiCORE?IPAXI IIC總線接口連接到AMBA?AXI規范,提供低速、兩線串行總線接口,可連接大量流行的設備。

2023-09-28 15:56:16 4484

4484 LogiCORE JTAG至AXI Master IP核是一個可定制的核,可生成AXIAXI總線可用于處理和驅動系統中FPGA內部的AXI信號。AXI總線接口協議可通過IP定制Vivado

2023-10-16 10:12:42 410

410

LogiCORE IP AXI 通用異步接收發送器 (UART) 16550 連接到高級微控制器總線架構 (AMBA) AXI,為異步串行數據傳輸提供控制器接口。該軟 IP 核旨在通過 AXI4-Lite 接口進行連接。

2023-10-16 11:02:01 1762

1762

以AXI4為例,有AXI full/lite/stream之分。 在Xilinx系列FPGA及其有關IP核中,經常見到AXI總線接口,AXI總線又分為三種: ?AXI-Lite,AXI-Full以及

2023-10-31 15:37:08 386

386

在介紹AXI之前,先簡單說一下總線、 接口 以及協議的含義 總線、接口和協議,這三個詞常常被聯系在一起,但是我們心里要明白他們的區別。 總線是一組傳輸通道,是各種邏輯器件構成的傳輸數據的通道,一般

2023-12-16 15:55:01 248

248

電子發燒友App

電子發燒友App

評論