以下為個人譯文,僅供個人學習記錄參考之用,如有疏漏之處,還請不吝賜教。

本篇博文將為您演示如何創建 AXI CDMA Linux 用戶空間示例應用。示例設計將在 Zynq UltraScale+ RFSoC ZCU111 評估板上實現通過AXI CDMA 把數據從 PS DDR 傳輸至 AXI BRAM。

本篇博文將為您演示如何創建AXI CDMA Linux用戶空間示例應用。

示例設計將在Zynq UltraScale+ RFSoC ZCU111評估板上實現通過AXI CDMA把數據從PS DDR傳輸至AXI BRAM。

適用平臺

Vivado和PetaLinux 2019.2。

Zynq UltraScale+ RFSoC ZCU111評估板

啟動模式:JTAG,SD

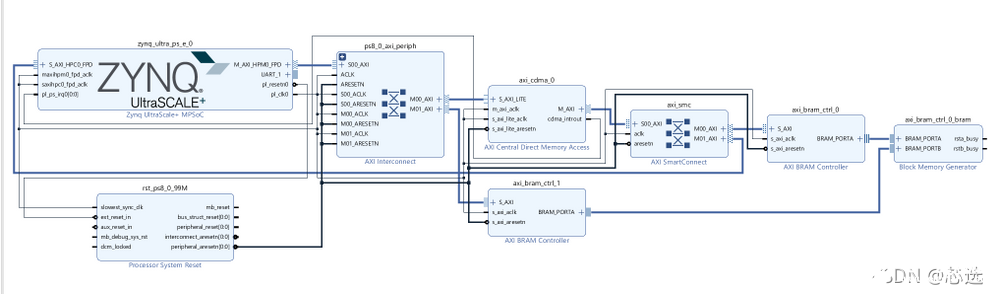

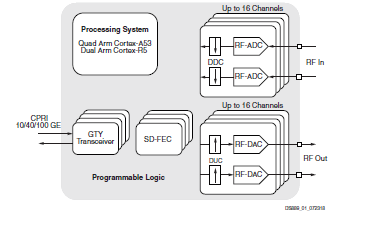

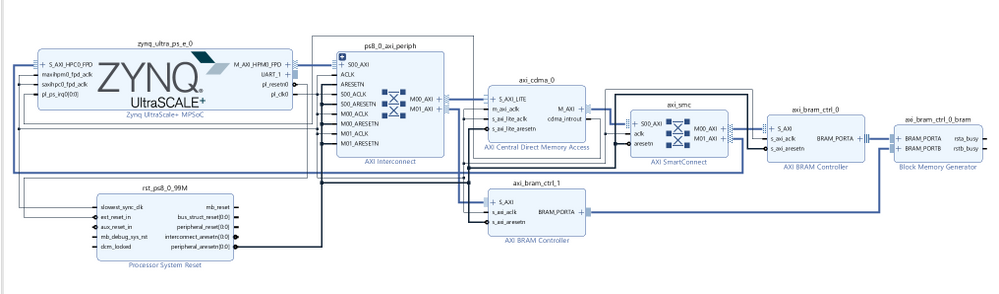

模塊框圖

Vivado步驟

步驟1:基于ZCU111評估版創建一個工程,并根據上圖中的模塊設計完成相應的模塊設計。

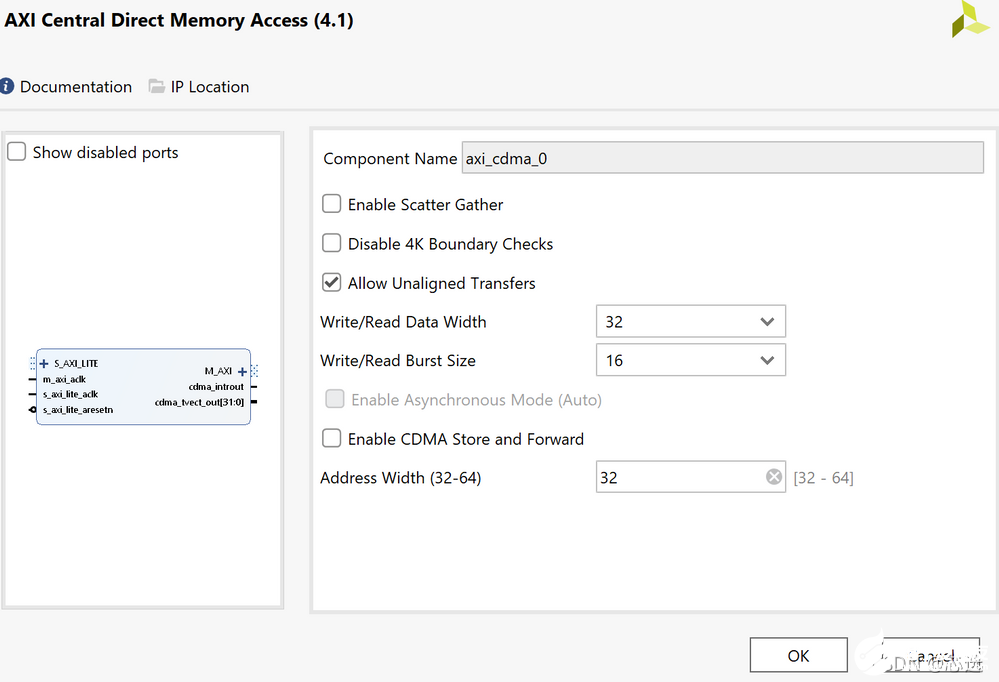

步驟2:按下列設置來配置AXI CDMA:

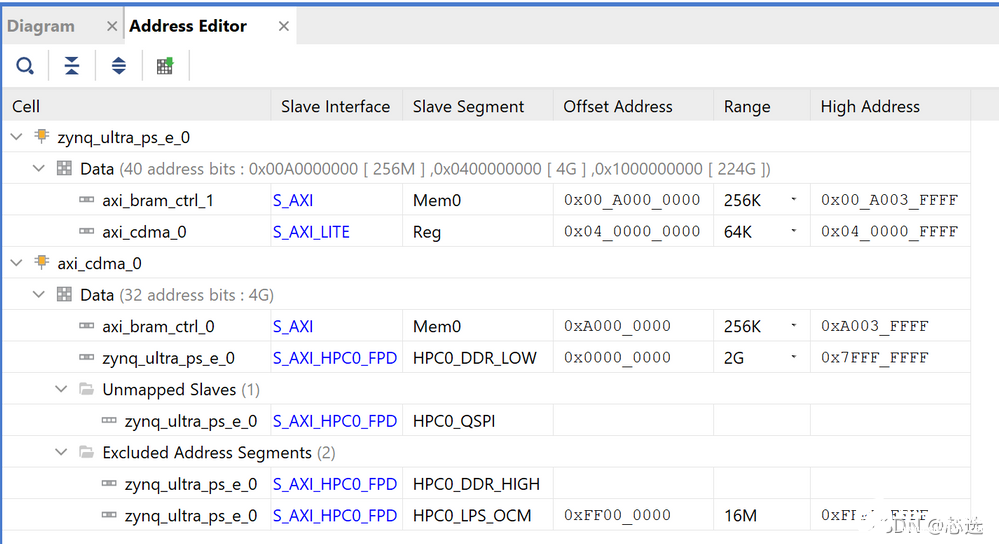

步驟3:成功完成后,選擇“驗證設計(Validate design)”以驗證設計,并檢查地址編輯器。

步驟4:創建整個模塊設計的頂層文件并生成比特流。

步驟5:導出硬件設計以獲取XSA文件。

PetaLinux步驟

以下步驟用于生成啟動鏡像和Linux用戶空間應用。

步驟1:

使用以下命令和隨附內容(axicdma.c)創建AXI CDMA用戶空間應用。

vim axicmda.c

步驟2:

petalinux-create -t project -n bram --template zynqMP

步驟3:

petalinux-config --v --get-hw-description=

步驟4:

在system-user.dtsi文件中添加以下更改以禁用CDMA驅動并保留內存。

/include/"system-conf.dtsi"

/{

#address-cells=<2>;

#size-cells=<2>;

memory{

device_type="memory";

reg=<0x0?0x0?0x0?0x80000000>,<0x0?0xA0000000?0x0?0x40000>,<0x00000008?0x00000000?0x0?0x80000000>;

};

reserved-memory{

ranges;

reserved{

reg=<0x0?0xa0000000?0x0?0x40000>;

};

};

};

&axi_bram_ctrl_1{

status="disabled";

};

&axi_cdma_0{

status="disabled";

};

步驟5:

petalinux-config -c kernel

然后,按如下方式操作:

Kernel hacking --->[ ] Filter access to /dev/mem --> Save & exit

步驟6:

petalinux-build

步驟7:

petalinux-package --boot --fsbl images/linux/zynqmp_fsbl.elf --pmufw images/linux/pmufw.elf --fpga images/linux/system.bit --u-boot images/linux/u-boot.elf --force

步驟8:

將BOOT.bin和image.ub文件與測試應用二進制文件一起復制到SD卡。

步驟9:

啟動評估板,并運行隨附的應用(axicmda.c)。

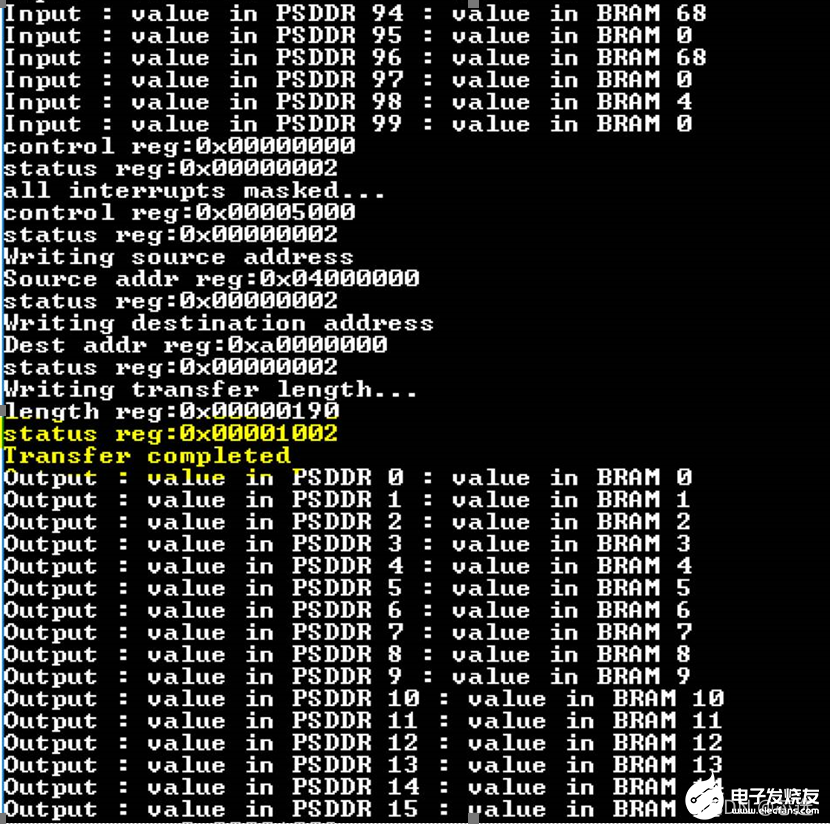

運行設計

要運行設計,請首先連接到ZCU111評估板并從SD卡啟動鏡像,然后運行二進制應用文件。

控制臺輸出

/dev/memopened. BRAMMemorymappedataddress0x7fb5339000. PSDDRMemorymappedataddress0x7fb5192000. CDMAMemorymappedataddress0x7fb5336000. Input:valueinPSDDR0:valueinBRAM1179403647 Input:valueinPSDDR1:valueinBRAM65794 Input:valueinPSDDR2:valueinBRAM0 Input:valueinPSDDR3:valueinBRAM0 Input:valueinPSDDR4:valueinBRAM11993091 Input:valueinPSDDR5:valueinBRAM1 Input:valueinPSDDR6:valueinBRAM13128 Input:valueinPSDDR7:valueinBRAM0 Input:valueinPSDDR8:valueinBRAM64 Input:valueinPSDDR9:valueinBRAM0 Input:valueinPSDDR10:valueinBRAM44872 Input:valueinPSDDR11:valueinBRAM0 Input:valueinPSDDR12:valueinBRAM0 Input:valueinPSDDR13:valueinBRAM3670080 Input:valueinPSDDR14:valueinBRAM4194313 Input:valueinPSDDR15:valueinBRAM1638426 Input:valueinPSDDR16:valueinBRAM6 Input:valueinPSDDR17:valueinBRAM4 Input:valueinPSDDR18:valueinBRAM64 Input:valueinPSDDR19:valueinBRAM0 Input:valueinPSDDR20:valueinBRAM64 Input:valueinPSDDR21:valueinBRAM0 Input:valueinPSDDR22:valueinBRAM64 Input:valueinPSDDR23:valueinBRAM0 Input:valueinPSDDR24:valueinBRAM504 Input:valueinPSDDR25:valueinBRAM0 Input:valueinPSDDR26:valueinBRAM504 Input:valueinPSDDR27:valueinBRAM0 Input:valueinPSDDR28:valueinBRAM8 Input:valueinPSDDR29:valueinBRAM0 Input:valueinPSDDR30:valueinBRAM3 Input:valueinPSDDR31:valueinBRAM4 Input:valueinPSDDR32:valueinBRAM568 Input:valueinPSDDR33:valueinBRAM0 Input:valueinPSDDR34:valueinBRAM568 Input:valueinPSDDR35:valueinBRAM0 Input:valueinPSDDR36:valueinBRAM568 Input:valueinPSDDR37:valueinBRAM0 Input:valueinPSDDR38:valueinBRAM27 Input:valueinPSDDR39:valueinBRAM0 Input:valueinPSDDR40:valueinBRAM27 Input:valueinPSDDR41:valueinBRAM0 Input:valueinPSDDR42:valueinBRAM1 Input:valueinPSDDR43:valueinBRAM0 Input:valueinPSDDR44:valueinBRAM1 Input:valueinPSDDR45:valueinBRAM5 Input:valueinPSDDR46:valueinBRAM0 Input:valueinPSDDR47:valueinBRAM0 Input:valueinPSDDR48:valueinBRAM0 Input:valueinPSDDR49:valueinBRAM0 Input:valueinPSDDR50:valueinBRAM0 Input:valueinPSDDR51:valueinBRAM0 Input:valueinPSDDR52:valueinBRAM37116 Input:valueinPSDDR53:valueinBRAM0 Input:valueinPSDDR54:valueinBRAM37116 Input:valueinPSDDR55:valueinBRAM0 Input:valueinPSDDR56:valueinBRAM65536 Input:valueinPSDDR57:valueinBRAM0 Input:valueinPSDDR58:valueinBRAM1 Input:valueinPSDDR59:valueinBRAM6 Input:valueinPSDDR60:valueinBRAM39544 Input:valueinPSDDR61:valueinBRAM0 Input:valueinPSDDR62:valueinBRAM105080 Input:valueinPSDDR63:valueinBRAM0 Input:valueinPSDDR64:valueinBRAM105080 Input:valueinPSDDR65:valueinBRAM0 Input:valueinPSDDR66:valueinBRAM5072 Input:valueinPSDDR67:valueinBRAM0 Input:valueinPSDDR68:valueinBRAM6168 Input:valueinPSDDR69:valueinBRAM0 Input:valueinPSDDR70:valueinBRAM65536 Input:valueinPSDDR71:valueinBRAM0 Input:valueinPSDDR72:valueinBRAM2 Input:valueinPSDDR73:valueinBRAM6 Input:valueinPSDDR74:valueinBRAM39560 Input:valueinPSDDR75:valueinBRAM0 Input:valueinPSDDR76:valueinBRAM105096 Input:valueinPSDDR77:valueinBRAM0 Input:valueinPSDDR78:valueinBRAM105096 Input:valueinPSDDR79:valueinBRAM0 Input:valueinPSDDR80:valueinBRAM512 Input:valueinPSDDR81:valueinBRAM0 Input:valueinPSDDR82:valueinBRAM512 Input:valueinPSDDR83:valueinBRAM0 Input:valueinPSDDR84:valueinBRAM8 Input:valueinPSDDR85:valueinBRAM0 Input:valueinPSDDR86:valueinBRAM4 Input:valueinPSDDR87:valueinBRAM4 Input:valueinPSDDR88:valueinBRAM596 Input:valueinPSDDR89:valueinBRAM0 Input:valueinPSDDR90:valueinBRAM596 Input:valueinPSDDR91:valueinBRAM0 Input:valueinPSDDR92:valueinBRAM596 Input:valueinPSDDR93:valueinBRAM0 Input:valueinPSDDR94:valueinBRAM68 Input:valueinPSDDR95:valueinBRAM0 Input:valueinPSDDR96:valueinBRAM68 Input:valueinPSDDR97:valueinBRAM0 Input:valueinPSDDR98:valueinBRAM4 Input:valueinPSDDR99:valueinBRAM0 controlreg:0x00000000 statusreg:0x00000002 allinterruptsmasked... controlreg:0x00005000 statusreg:0x00000002 Writingsourceaddress Sourceaddrreg:0x04000000 statusreg:0x00000002 Writingdestinationaddress Destaddrreg:0xa0000000 statusreg:0x00000002 Writingtransferlength... DMAtransferiscompleted lengthreg:0x00000190 statusreg:0x00001002 Output:valueinPSDDR0:valueinBRAM0 Output:valueinPSDDR1:valueinBRAM1 Output:valueinPSDDR2:valueinBRAM2 Output:valueinPSDDR3:valueinBRAM3 Output:valueinPSDDR4:valueinBRAM4 Output:valueinPSDDR5:valueinBRAM5 Output:valueinPSDDR6:valueinBRAM6 Output:valueinPSDDR7:valueinBRAM7 Output:valueinPSDDR8:valueinBRAM8 Output:valueinPSDDR9:valueinBRAM9 Output:valueinPSDDR10:valueinBRAM10 Output:valueinPSDDR11:valueinBRAM11 Output:valueinPSDDR12:valueinBRAM12 Output:valueinPSDDR13:valueinBRAM13 Output:valueinPSDDR14:valueinBRAM14 Output:valueinPSDDR15:valueinBRAM15 Output:valueinPSDDR16:valueinBRAM16 Output:valueinPSDDR17:valueinBRAM17 Output:valueinPSDDR18:valueinBRAM18 Output:valueinPSDDR19:valueinBRAM19 Output:valueinPSDDR20:valueinBRAM20 Output:valueinPSDDR21:valueinBRAM21 Output:valueinPSDDR22:valueinBRAM22 Output:valueinPSDDR23:valueinBRAM23 Output:valueinPSDDR24:valueinBRAM24 Output:valueinPSDDR25:valueinBRAM25 Output:valueinPSDDR26:valueinBRAM26 Output:valueinPSDDR27:valueinBRAM27 Output:valueinPSDDR28:valueinBRAM28 Output:valueinPSDDR29:valueinBRAM29 Output:valueinPSDDR30:valueinBRAM30 Output:valueinPSDDR31:valueinBRAM31 Output:valueinPSDDR32:valueinBRAM32 Output:valueinPSDDR33:valueinBRAM33 Output:valueinPSDDR34:valueinBRAM34 Output:valueinPSDDR35:valueinBRAM35 Output:valueinPSDDR36:valueinBRAM36 Output:valueinPSDDR37:valueinBRAM37 Output:valueinPSDDR38:valueinBRAM38 Output:valueinPSDDR39:valueinBRAM39 Output:valueinPSDDR40:valueinBRAM40 Output:valueinPSDDR41:valueinBRAM41 Output:valueinPSDDR42:valueinBRAM42 Output:valueinPSDDR43:valueinBRAM43 Output:valueinPSDDR44:valueinBRAM44 Output:valueinPSDDR45:valueinBRAM45 Output:valueinPSDDR46:valueinBRAM46 Output:valueinPSDDR47:valueinBRAM47 Output:valueinPSDDR48:valueinBRAM48 Output:valueinPSDDR49:valueinBRAM49 Output:valueinPSDDR50:valueinBRAM50 Output:valueinPSDDR51:valueinBRAM51 Output:valueinPSDDR52:valueinBRAM52 Output:valueinPSDDR53:valueinBRAM53 Output:valueinPSDDR54:valueinBRAM54 Output:valueinPSDDR55:valueinBRAM55 Output:valueinPSDDR56:valueinBRAM56 Output:valueinPSDDR57:valueinBRAM57 Output:valueinPSDDR58:valueinBRAM58 Output:valueinPSDDR59:valueinBRAM59 Output:valueinPSDDR60:valueinBRAM60 Output:valueinPSDDR61:valueinBRAM61 Output:valueinPSDDR62:valueinBRAM62 Output:valueinPSDDR63:valueinBRAM63 Output:valueinPSDDR64:valueinBRAM64 Output:valueinPSDDR65:valueinBRAM65 Output:valueinPSDDR66:valueinBRAM66 Output:valueinPSDDR67:valueinBRAM67 Output:valueinPSDDR68:valueinBRAM68 Output:valueinPSDDR69:valueinBRAM69 Output:valueinPSDDR70:valueinBRAM70 Output:valueinPSDDR71:valueinBRAM71 Output:valueinPSDDR72:valueinBRAM72 Output:valueinPSDDR73:valueinBRAM73 Output:valueinPSDDR74:valueinBRAM74 Output:valueinPSDDR75:valueinBRAM75 Output:valueinPSDDR76:valueinBRAM76 Output:valueinPSDDR77:valueinBRAM77 Output:valueinPSDDR78:valueinBRAM78 Output:valueinPSDDR79:valueinBRAM79 Output:valueinPSDDR80:valueinBRAM80 Output:valueinPSDDR81:valueinBRAM81 Output:valueinPSDDR82:valueinBRAM82 Output:valueinPSDDR83:valueinBRAM83 Output:valueinPSDDR84:valueinBRAM84 Output:valueinPSDDR85:valueinBRAM85 Output:valueinPSDDR86:valueinBRAM86 Output:valueinPSDDR87:valueinBRAM87 Output:valueinPSDDR88:valueinBRAM88 Output:valueinPSDDR89:valueinBRAM89 Output:valueinPSDDR90:valueinBRAM90 Output:valueinPSDDR91:valueinBRAM91 Output:valueinPSDDR92:valueinBRAM92 Output:valueinPSDDR93:valueinBRAM93 Output:valueinPSDDR94:valueinBRAM94 Output:valueinPSDDR95:valueinBRAM95 Output:valueinPSDDR96:valueinBRAM96 Output:valueinPSDDR97:valueinBRAM97 Output:valueinPSDDR98:valueinBRAM98 Output:valueinPSDDR99:valueinBRAM99 TransmittedDatasuccessfully root@cdma_proj:~#

輸出截屏

本文轉載自:芯選的CSDN博客

審核編輯:湯梓紅

-

Linux

+關注

關注

87文章

11479瀏覽量

213080 -

Zynq

+關注

關注

10文章

614瀏覽量

48090 -

AXI

+關注

關注

1文章

135瀏覽量

17148

發布評論請先 登錄

Zynq UltraScale + MPSoC USB 3.0 CDC器件類設計

怎么使用AXI CDMA從OCM/DDR寫入BRAM

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器

Xilinx ZYNQ UltraScale+RFSoCZU27DR 開源RFSOC算法驗證評估板

Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞

賽靈思推出同類首創的Zynq UltraScale+RFSoC ZCU111評估套件

Zynq UltraScale+ RFSoC的功能特點與應用

Zynq UltraScale Rfsoc數據手冊的詳細資料概述

支持6GHz以下頻段的Zynq UltraScale+RFSoC

上新:Zynq UltraScale+ RFSoC ZCU111 評估套件

賽靈思關于Zynq UltraScale+ RFSoC系列產品介紹

Zynq UltraScale+ MPSoC的隔離設計示例

Zynq UltraScale+RFSoC的AXI CDMA Linux用戶空間示例

Zynq UltraScale+RFSoC的AXI CDMA Linux用戶空間示例

評論