最近需要用到AXI接口的模塊,xilinx的IP核很多都用到了AXI總線(xiàn)進(jìn)行數(shù)據(jù)和指令傳輸。如果有多個(gè)設(shè)備需要使用AXI協(xié)議對(duì)AXI接口的BRAM進(jìn)行讀寫(xiě),總線(xiàn)之間該如何進(jìn)行仲裁,通信?

這里我們注意到,Vivado有一個(gè)叫做AXI Interconnect (RTL)的IP核,這個(gè)IP核可以實(shí)現(xiàn)上述功能。

本文將簡(jiǎn)單講解AXI Interconnect IP核的使用方法,設(shè)計(jì)到Vivado的Block Design,仿真等知識(shí)運(yùn)用。

為了簡(jiǎn)化整體例子的復(fù)雜度,整個(gè)測(cè)試工程項(xiàng)目采用了兩個(gè)措施:

- 使用Block Design代替了RTL代碼書(shū)寫(xiě)連線(xiàn)操作

- 使用AXI4-Lite總線(xiàn)進(jìn)行測(cè)試,相對(duì)于A(yíng)XI4,省去了部分信號(hào)

- 整個(gè)工程量不大,故沒(méi)有在VCS中仿真,使用Vivado自帶的仿真器做仿真

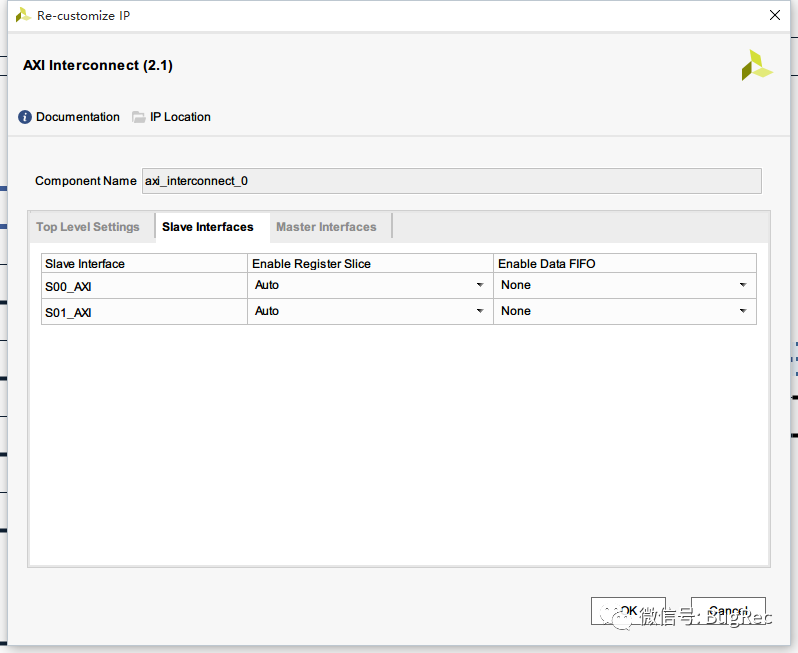

最終整體的Block Design結(jié)構(gòu)如下圖:

圖1

簡(jiǎn)單介紹一下圖1中的模塊功能

clk_wiz_0: MMCM,模式時(shí)鐘管理器,這里作用主要是產(chǎn)生100MHz的clk_out1和200MHz的clk_out2,類(lèi)似鎖相環(huán);proc_sys_reset_x: 系統(tǒng)復(fù)位模塊,根據(jù)輸入時(shí)鐘和輸入的信號(hào)產(chǎn)生對(duì)應(yīng)的高復(fù)位有效信號(hào)和低復(fù)位有效信號(hào);axi_interconnect_0: AXI Interconnect,這里管理著2個(gè)Slave接口和1個(gè)Master接口;對(duì)總線(xiàn)傳輸進(jìn)行仲裁,通信,時(shí)序轉(zhuǎn)換等操作。axi_bram_ctrl_0: Bram Controller,AXI接口的Bram控制器;blk_mem_gen_0: Block Ram

簡(jiǎn)單介紹下Block Design的AXI Interconnect IP核使用(因?yàn)锽lock Design可以實(shí)現(xiàn)自動(dòng)連線(xiàn),自動(dòng)設(shè)置位寬等信息,所以設(shè)置內(nèi)容沒(méi)有AXI Interconnect RTL多,后者專(zhuān)用于Verilog代碼中使用)

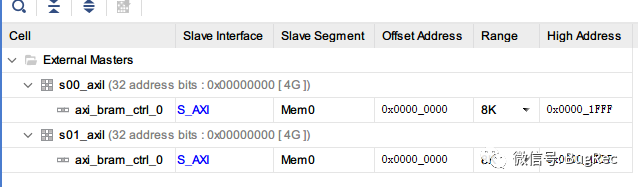

圖2

這個(gè)界面設(shè)置Slave Interface的數(shù)量,與Master 模塊的數(shù)量對(duì)應(yīng);Master Interface數(shù)量,與 Slave模塊的數(shù)量對(duì)應(yīng),如果想不明白可以看圖6。

圖3

圖4

這里使能S/M_AXI端口的Register Slice和Data FIFO功能,Slice對(duì)時(shí)序收斂有一定作用,但是數(shù)據(jù)輸出會(huì)延遲一個(gè)周期;Data FIFO,顧名思義,可以實(shí)現(xiàn)數(shù)據(jù)緩存和packet mode。

圖5

勾選圖2的Advanced Options后,可以進(jìn)入圖5界面,這里可以設(shè)置S_AXI端口的優(yōu)先級(jí),優(yōu)先級(jí)值越高,越優(yōu)先,平行優(yōu)先級(jí)的端口會(huì)使用輪詢(xún)的方式處理端口請(qǐng)求。

圖6

整個(gè)IP核的外部端口,Sxx_AXI連接Master模塊的M_AXI接口;Mxx_AXI連接Slave模塊的S_AXI接口;ACLK是IP核的運(yùn)行時(shí)鐘,ARESETN是IP核的異步低有效復(fù)位信號(hào)。

Sxx_ACLK是對(duì)應(yīng)總線(xiàn)的總線(xiàn)時(shí)鐘,Sxx_ARESETN是對(duì)應(yīng)總線(xiàn)的異步低有效復(fù)位信號(hào)。同理,Mxx_ACLK是對(duì)應(yīng)總線(xiàn)的總線(xiàn)時(shí)鐘,Mxx_ACLK_ARESETN是對(duì)應(yīng)總線(xiàn)的異步低有效復(fù)位信號(hào)。

圖中出現(xiàn)了4個(gè)時(shí)鐘端口,這4個(gè)時(shí)鐘端口的頻率可以各不相同。曾經(jīng)我很疑惑ACLK的時(shí)鐘頻率到底應(yīng)該如何設(shè)置,找到了一個(gè)在Xilinx論壇的帖子,上面的建議是連接到任一Sxx_ACLK或者M(jìn)xx_ACLK,雖然ACLK可以隨意連接到一個(gè)時(shí)鐘頻率信號(hào)。

圖1的輸入端口有S00_AXI,S01_AXI的接口,clk_100MHz的時(shí)鐘輸入信號(hào),reset_rtl_0的高有效復(fù)位信號(hào);輸出有100MHz的clk_out1,200MHz的clk_out2;

然后將Block Design生成為verilog文件,供其他的verilog文件直接實(shí)例化。這里我們利用留出的clk_out1,clk_out2,s00_axi,s01_axi接口,對(duì)Bram進(jìn)行簡(jiǎn)單的地址讀寫(xiě)操作,讀寫(xiě)時(shí)鐘分別為200MHz/100MHz。

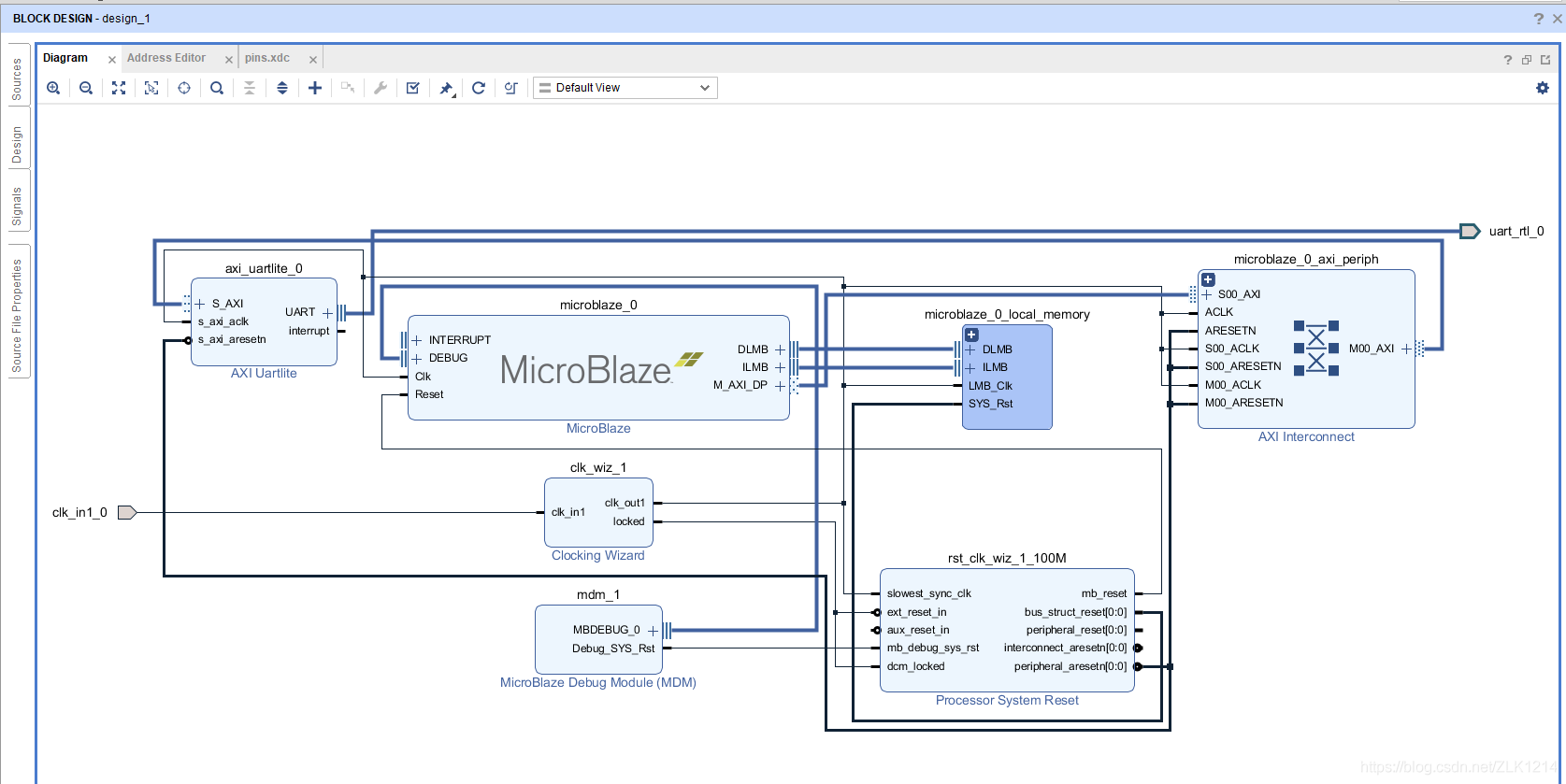

Testbench里面,除了必要的initial和時(shí)鐘賦值外,主要的還是對(duì)s00_axi,s01_axi的控制。

s00_axi在100MHz時(shí)鐘域下,我們單獨(dú)對(duì)它進(jìn)行寫(xiě)操作。

在設(shè)計(jì)過(guò)程中,我還發(fā)現(xiàn)了一個(gè)奇怪的現(xiàn)象,原本的設(shè)計(jì)中,握手信號(hào)想等著s00_axil_awready信號(hào)拉高之后,這邊的s00_axil_awvalid再拉高。結(jié)果發(fā)現(xiàn)awready遲遲沒(méi)有拉高,在看完參考資料1后,才知道需要Master這側(cè)的valid先拉高,否則slave的ready信號(hào)不一定會(huì)拉高;所以s00_axil_awvalid, s01_axil_arvalid設(shè)置為1 。

100MHz頻率下,s00_axil_awaddr 在寫(xiě)入數(shù)據(jù)完成(s00_axil_wready & s00_axil_wvalid)后,地址會(huì)加4;地址寫(xiě)到1024后會(huì)重新歸零。

可以看到,等到s00_axil_wready拉高,Master會(huì)把s00_axil_wvalid拉高,并生成一個(gè)隨機(jī)數(shù)寫(xiě)入BRAM;然后s00_axil_wvalid拉低。

always @ (posedge clk_out1) begin

if (s00_axil_wready & s00_axil_wvalid)

s00_axil_awaddr <= (s00_axil_awaddr < 32'd1023) ? s00_axil_awaddr + 32'd4 : 0;

if (s00_axil_wready & ~s00_axil_wvalid) begin

s00_axil_wvalid <= 1'b1;

s00_axil_wdata <= $random;

end

else

s00_axil_wvalid <= 1'b0;

end

200MHz頻率下,s01_axil_araddr在讀取數(shù)據(jù)完成后(s01_axil_rvalid & s01_axil_rready),會(huì)加4;同樣,地址寫(xiě)到1024后會(huì)重新歸零。

可以看到,等到s01_axil_rvalid拉高,s01_axil_rready會(huì)拉高,讀取出對(duì)應(yīng)數(shù)據(jù),然后拉低s01_axil_rready;

always @ (posedge clk_out2) begin

s01_axil_arvalid <= 1'b1;

if (s01_axil_rvalid & s01_axil_rready)

s01_axil_araddr <= (s01_axil_araddr < 32'd1023) ? s01_axil_araddr + 32'd4 : 0;

if (s01_axil_rvalid & ~s01_axil_rready) begin

s01_axil_rready <= 1'b1;

end

else

s01_axil_rready <= 1'b0;

end

當(dāng)然,為什么兩個(gè)不同的總線(xiàn)能夠?qū)σ粋€(gè)BRAM進(jìn)行操作,這里涉及到地址分配的問(wèn)題;

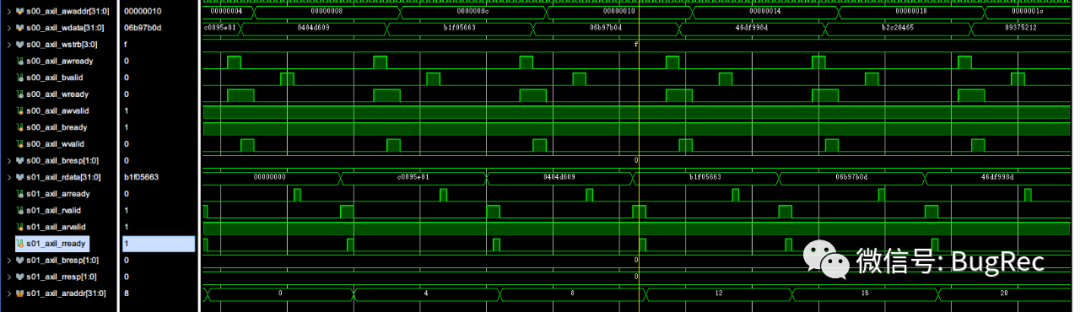

圖7

兩個(gè)總線(xiàn)可以訪(fǎng)問(wèn)到同一個(gè)地址,所以自然可以對(duì)同一個(gè)BRAM進(jìn)行操作;那有人可能問(wèn),假如我操作s00訪(fǎng)問(wèn)的地址超過(guò)了分配的地址范圍呢,那么s00_axil_bresp會(huì)等于2'd3,告知地址錯(cuò)誤的問(wèn)題。

圖8

由于設(shè)計(jì)問(wèn)題,讀取的地址相比寫(xiě)入數(shù)據(jù)落后幾個(gè)時(shí)鐘周期,這樣可以將剛寫(xiě)入的數(shù)據(jù)讀出來(lái)。

這個(gè)實(shí)驗(yàn)表明AXI Interconnect不僅是總線(xiàn)仲裁器,還幫助時(shí)鐘域不同的AXI總線(xiàn)完成了時(shí)序轉(zhuǎn)換。除此之外,AXI Interconnect還可以實(shí)現(xiàn)數(shù)據(jù)位寬轉(zhuǎn)換,AXI協(xié)議轉(zhuǎn)換,例如AXI4/3轉(zhuǎn)AXI4-Lite,AXI4轉(zhuǎn)AXI3等;增加Register Slice改善時(shí)序,增加數(shù)據(jù)fifo緩存數(shù)據(jù);

AXI Interconnect最多支持16 MI與16 SI組合。不過(guò),當(dāng)配置只有一個(gè)SI接口時(shí),MI接口最多可以設(shè)置到64位。

其中的仲裁采用的輪詢(xún)調(diào)度算法,當(dāng)然,IP核可以設(shè)置每個(gè)SI的優(yōu)先級(jí),值越高,優(yōu)先級(jí)越高;

當(dāng)然,這篇文章只是為了簡(jiǎn)單介紹AXI Interconnect的作用,更復(fù)雜更多的功能還有待發(fā)掘。當(dāng)然,功能強(qiáng)大意味著復(fù)雜,比如根據(jù)參考資料2,AXI4協(xié)議中的ID信號(hào),如果在A(yíng)XI Interconnect中使用不當(dāng),可能造成仲裁器死鎖。

圖9

看上圖,在我的示例中,ACLK與S01_ACLK同源同頻,所以示意圖中,s01_couples從S_AXI直通到M_AXI;而s00_couples則添加了一個(gè)AXI Clock Converter做時(shí)序轉(zhuǎn)換;在m00_couples中,又使用了AXI Clock Converter將ACLK轉(zhuǎn)換到M00_ACLK;

至此,簡(jiǎn)單總結(jié)下在A(yíng)XI通信中使用AXI Interconnect的好處:

- 真正實(shí)現(xiàn)了總線(xiàn)通信,N Master模塊與M Slave模塊的通信,減少了相互間通信的復(fù)雜度

- 內(nèi)部實(shí)現(xiàn)時(shí)鐘域轉(zhuǎn)換,不需要外部的過(guò)度干預(yù)

- 內(nèi)部可實(shí)現(xiàn)FIFO等,免去了很多場(chǎng)景下需要FIFO,Register,位寬轉(zhuǎn)換,協(xié)議轉(zhuǎn)換的需求

-

控制器

+關(guān)注

關(guān)注

114文章

17017瀏覽量

183243 -

RTL

+關(guān)注

關(guān)注

1文章

388瀏覽量

60766 -

VCS

+關(guān)注

關(guān)注

0文章

80瀏覽量

9862 -

AXI總線(xiàn)

+關(guān)注

關(guān)注

0文章

66瀏覽量

14514 -

BRAM

+關(guān)注

關(guān)注

0文章

41瀏覽量

11248

發(fā)布評(píng)論請(qǐng)先 登錄

一文詳解Video In to AXI4-Stream IP核

Designing High-Performance Video Systems with the AXI Interconnect

有人知道為什么MIG IP核中的AXI協(xié)議。為什么沒(méi)有AXI_WID這個(gè)信號(hào)呢?

如何在IP_catalog中創(chuàng)建可見(jiàn)的axi_interconnect_v2.1?

PCIE項(xiàng)目中AXI4 IP核例化詳解

AXI FIFO和AXI virtual FIFO這兩個(gè)IP的使用方法

三個(gè)不同AXI IP核的實(shí)現(xiàn)的方法_性能的對(duì)比及差異的分析

基于MicroBlaze的AXI總線(xiàn)實(shí)時(shí)時(shí)鐘IP核設(shè)計(jì)

AXI接口簡(jiǎn)介_(kāi)AXI IP核的創(chuàng)建流程及讀寫(xiě)邏輯分析

自定義sobel濾波IP核,IP接口遵守AXI Stream協(xié)議

如何使用MicroBlaze調(diào)用AXI IP核詳細(xì)解析

Xilinx FPGA里面的AXI DMA IP核的簡(jiǎn)單用法

AXI4-Stream Video 協(xié)議和AXI_VDMA的IP核介紹

自定義AXI-Lite接口的IP及源碼分析

FPGA學(xué)習(xí)筆記:ROM IP核的使用方法

簡(jiǎn)單講解AXI Interconnect IP核的使用方法

簡(jiǎn)單講解AXI Interconnect IP核的使用方法

評(píng)論