上文FPGA IP之AXI4協議1_協議構架對協議框架進行了說明,本文對AXI4接口的信號進行說明:

1.全局信號

ACLK,ARESETn,AXI所有信號都在時鐘的上升沿采樣.

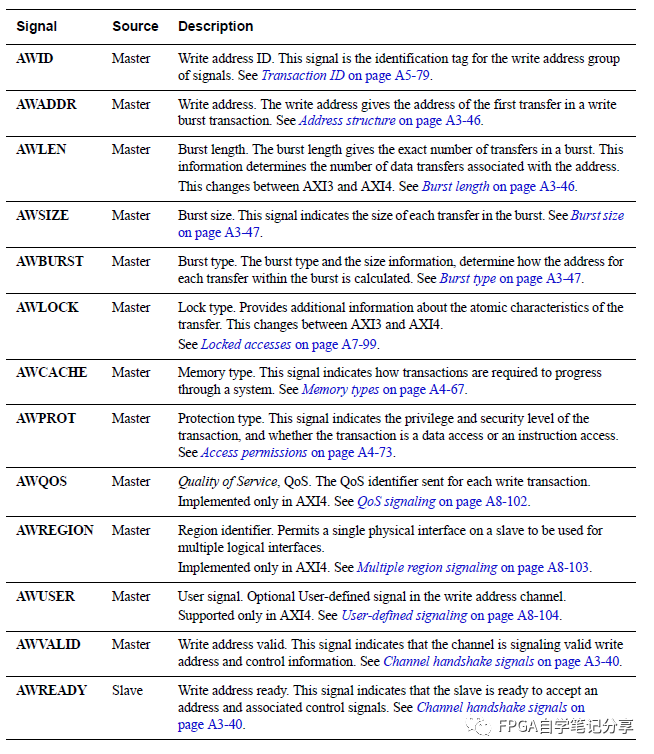

2.寫地址通道信號

AWID Master 寫地址ID。該信號是信號寫地址組的標識標簽。

AWADDR Master 寫地址。寫地址給出寫突發事務中第一個傳輸的地址。

AWLEN Master爆發長度。突發長度給出了突發中傳輸的確切數量。此信息確定與該地址關聯的數據傳輸數量。這在AXI3和AXI4之間發生變化。

AWSIZE Master 突發大小。這個信號表示脈沖中每個傳輸的大小。

AWBURST Master 爆發類型。突發類型和大小信息決定了如何計算突發中每個傳輸的地址。

AWLOCK Master 鎖類型。提供有關傳輸的原子特性的附加信息。這在AXI3和AXI4之間發生變化。

AWCACHE Master內存類型。這個信號表明事務如何在系統中進行。

AWPROT Master 保護類型。該信號指示事務的權限和安全級別,以及該事務是數據訪問還是指令訪問。

AWQOS Master服務質量,QoS。為每個寫事務發送的QoS標識符。僅在AXI4中實現

AWREGION Master區域標識符。允許從服務器上的一個物理接口用于多個邏輯接口。

僅在AXI4中實現。

AWUSER Master 用戶信號。可選寫地址通道中用戶自定義的信號。僅在AXI4中支持。

AWVALID Master寫地址有效。該信號表明通道正在發出有效的寫地址和控制信息。

AWREADY Slave 寫地址準備就緒。這個信號表明從機已經準備好接受一個地址和相關的控制信號。

官網文檔如下:

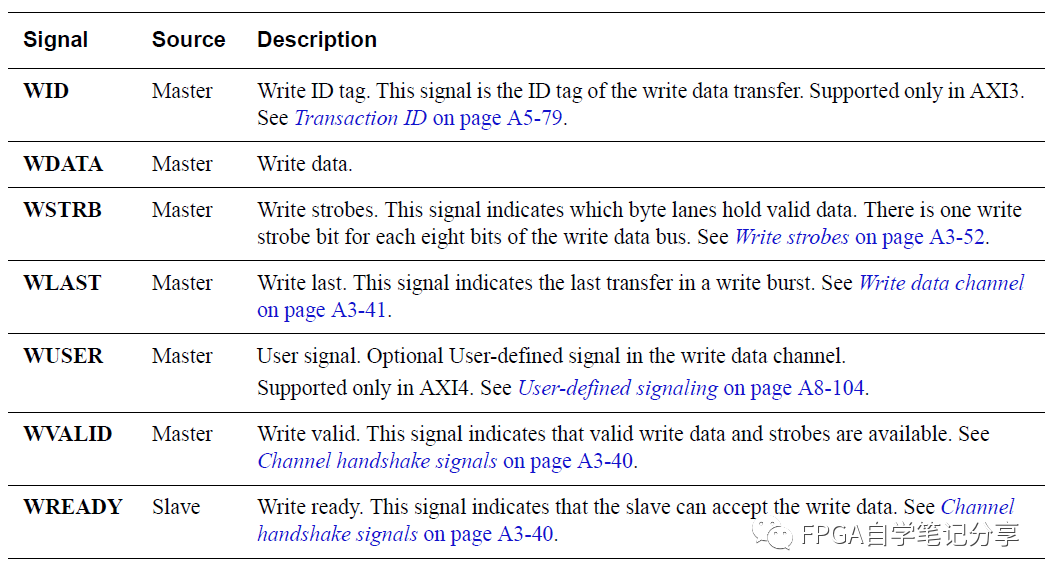

3.寫數據通道信號

WID Master寫ID標簽。這個信號是寫入數據傳輸的ID標記。僅在AXI3中支持。

WDATA Master寫數據。

WSTRB Master寫byte有效標注。這個信號指示哪些字節通道保存有效數據。寫數據總線的每八位有一個寫標志位。

WLAST Master最后寫。這個信號表示寫突發中的最后一次傳輸。

WUSER Master用戶信號。可選寫入數據通道中用戶自定義的信號。僅在AXI4中支持。

WVALID Master寫有效。此信號表示有效的寫數據和頻閃燈可用。

WREADY Slave 寫準備就緒。這個信號表示從機可以接受寫數據。

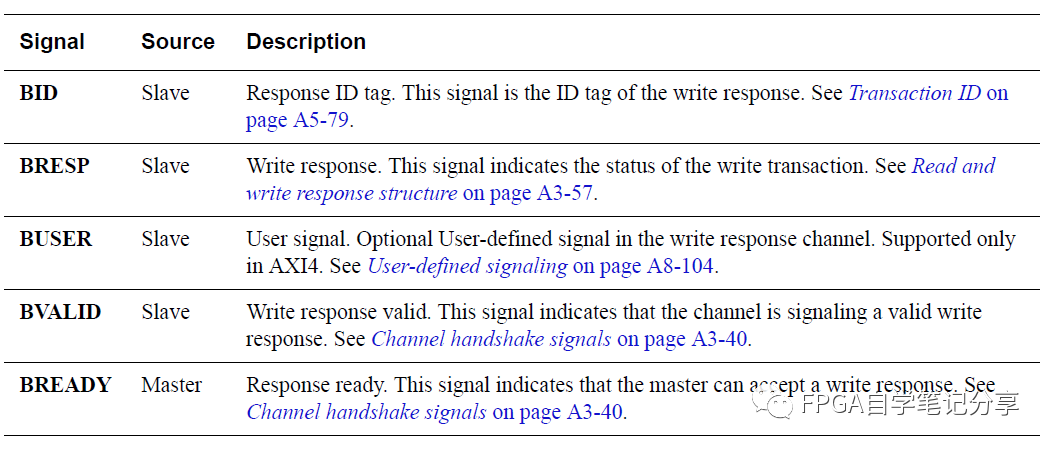

4.寫響應通道信號

BID Slave響應ID標記。這個信號是寫響應的ID標記。

BRESP Slave 寫響應信號。這個信號指示寫事務的狀態。

BUSER Slave用戶信號。可選寫響應通道中用戶自定義的信號。僅在AXI4中支持。

BVALID Slave寫響應有效。此信號表示通道正在發出有效的寫響應信號。

BREADY Master響應準備就緒。這個信號表明主機可以接受寫響應。

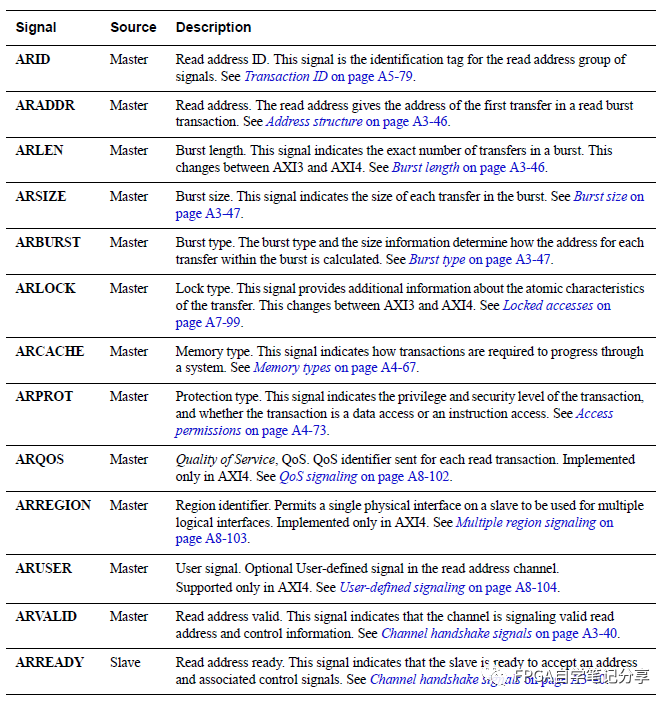

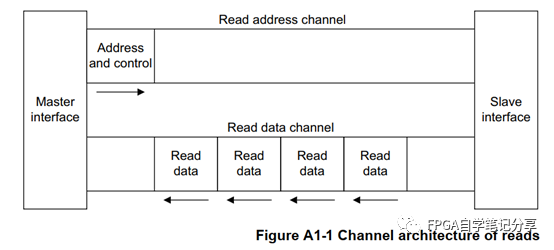

5.讀地址通道

和寫地址通道完全相同:

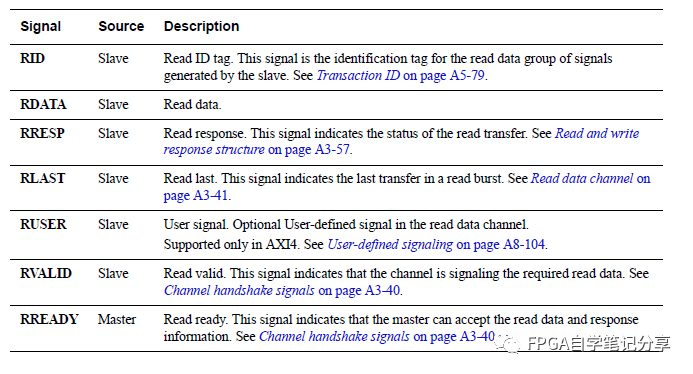

6.讀數據通道信號

RID Slave讀ID標簽。這個信號是從機產生的信號的讀數據組的標識標簽。

RDATA Slave讀數據。

RRESP Slave讀響應。這個信號表示讀傳輸的狀態。

RLAST Slave最后讀取。這個信號表示讀突發中的最后一次傳輸。

RUSER Slave從用戶信號。可選讀數據通道中用戶自定義的信號。僅在AXI4中支持。

RVALID Slave讀有效。該信號表示通道正在發送所需的讀取數據的信號。

RREADY Master讀準備就緒。該信號表示主機可以接受讀取數據和響應信息。

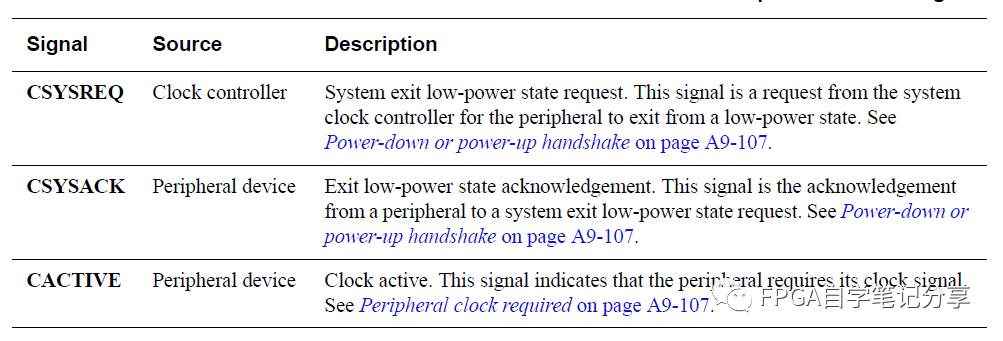

7.低功耗接口信號

CSYSREQ Clock controller 系統退出低電狀態請求。這個信號是來自系統時鐘控制器的一個請求,要求外設退出低功耗狀態。

CSYSACK Peripheral device 退出低電狀態確認。此信號是從外設到系統退出低功耗狀態請求的確認。

CACTIVE Peripheral device 時鐘有效。這個信號表明外圍設備請求時鐘信號。

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614639 -

接口

+關注

關注

33文章

8961瀏覽量

153288 -

信號

+關注

關注

11文章

2844瀏覽量

77955 -

時鐘

+關注

關注

11文章

1886瀏覽量

132903 -

AXI4

+關注

關注

0文章

20瀏覽量

9030

發布評論請先 登錄

看看在SpinalHDL中AXI4總線互聯IP的設計

SoC Designer AXI4協議包的用戶指南

AMBA 4 AXI4、AXI4-Lite和AXI4-流協議斷言用戶指南

ZYNQ中DMA與AXI4總線

AXI4 、 AXI4-Lite 、AXI4-Stream接口

AXI3與AXI4寫響應的依賴區別?

Xilinx FPGA AXI4總線(一)介紹【AXI4】【AXI4-Lite】【AXI-Stream】

漫談AMBA總線-AXI4協議的基本介紹

SoC設計中總線協議AXI4與AXI3的主要區別詳解

AMBA AXI4接口協議概述

FPGA AXI4協議學習筆記(二)

FPGA AXI4協議學習筆記(二)

評論