1.關于AXI協議

AMBA AXI協議支持高性能、高頻系統設計。

AXI協議:

?適用于高帶寬和低延遲的設計;

?提供高頻操作,無需使用復雜的連線橋接;

?滿足多器件的接口要求;

?適用于具有高初始訪問延遲的內存控制器;

?提供靈活的互連架構;

?向后兼容現有的AHB和APB接口。

AXI協議的主要特性是:

?獨立的地址/控制和數據階段

?使用字節控制支持不對齊的數據傳輸;

?使用基于突發的傳輸(burst),只需要發出起始地址;

?獨立的讀和寫數據通道,可以提供低成本的直接內存訪問(DMA);

?支持發出多個傳輸地址;

?支持亂序傳輸;

?允許輕松添加配置階段,以提供定時關斷(AXI支持低功耗擴展模式)。

2.AXI 架構

AXI協議是基于突發傳輸的(burst-based),并定義了以下獨立的傳輸通道:

?讀取地址傳輸通道

?讀取數據傳輸通道

?寫地址傳輸通道

?寫入數據傳輸通道

?寫響應傳輸通道

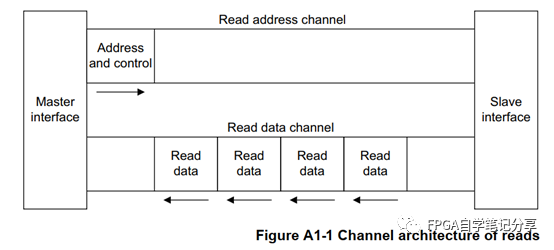

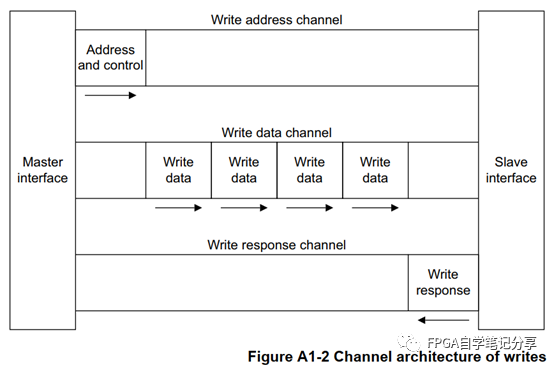

地址通道攜帶描述要傳輸的數據性質的控制信息。 數據在主從之間通過以下方式傳輸:

?寫數據通道,用于將數據從主端傳輸到從端。 在寫事務中,從端使用寫響應通道向主機發送完成傳輸的信號。

?讀取數據通道,將數據從從端傳輸到主機。

AXI協議:

?允許在實際數據傳輸之前發出地址信息;

?支持多個未完成的傳輸事務;

?支持亂序傳輸。

讀傳輸使用讀地址和讀數據通道進行讀操作的過程如下圖所示:

寫傳輸使用寫地址、寫數據通道和響應通道進行讀操作的過程如下圖所示:

信息源端使用VALID信號來顯示通道上何時有有效地址、數據或控制信息可用。 目的端使用READY信號來顯示它何時可以接受信息。 讀數據通道和寫數據通道都包括一個LAST信號,以指示事務中最終數據項的傳輸。

讀和寫地址通道:

讀寫傳輸都有自己的地址通道。 適當的地址通道攜帶傳輸所需的所有地址和控制信息。

讀數據通道:

讀數據通道攜帶從端到主端的讀數據和讀響應信息,包括:

?數據總線,可以是8、16、32、64、128、256、512或1024位寬;

?一個讀響應信號,指示讀事務的完成狀態。

寫數據通道:

寫數據通道攜帶從主機到從主機的寫數據,包括:

?數據總線,可以是8、16、32、64、128、256、512或1024位寬;

?字節有效信號為每8個數據位,表明哪些字節的數據是有效的。

寫數據通道信息總是被視為緩沖的,這樣主端就可以執行寫傳輸,而不需要等待從端確認。

寫響應信道:

從端使用寫響應通道來響應寫傳輸。所有寫傳輸都需要在寫響應通道上發出完成信號。寫傳輸完成時,寫響應只對一個完全的傳輸發出響應信號,而不是對傳輸中的每個數據傳輸發出響應信號。

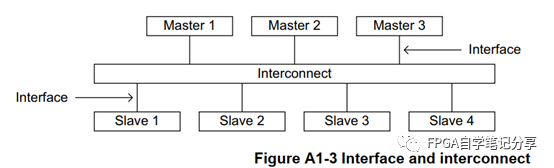

3.AXI總線的互聯:

AXI協議提供了一個單獨的接口定義,用于以下接口:

主機和互聯接口之間的連接;

從機和互連接口之間的連接;

主機和從機之間連接;

AXI的連接接口如下:

AXI的拓撲結構,大多數系統使用AXI以下三種互連拓撲之一:

?共享地址和數據總線;

?共享地址總線和多個數據總線;

?多層,具有多個地址和數據總線;

在大多數系統中,地址通道帶寬需求明顯小于數據通道帶寬需求。這樣的系統可以通過使用多個數據總線的共享地址總線來實現并行數據傳輸,從而在系統性能和互連復雜性之間實現良好的平衡。

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614632 -

接口

+關注

關注

33文章

8961瀏覽量

153283 -

總線

+關注

關注

10文章

2953瀏覽量

89407 -

AMBA

+關注

關注

0文章

70瀏覽量

15353 -

AXI

+關注

關注

1文章

134瀏覽量

17123

發布評論請先 登錄

看看在SpinalHDL中AXI4總線互聯IP的設計

SoC Designer AXI4協議包的用戶指南

AMBA 4 AXI4、AXI4-Lite和AXI4-流協議斷言用戶指南

一文詳解ZYNQ中的DMA與AXI4總線

深入AXI4總線一握手機制

AXI4 、 AXI4-Lite 、AXI4-Stream接口

AXI3與AXI4寫響應的依賴區別?

Xilinx FPGA AXI4總線(一)介紹【AXI4】【AXI4-Lite】【AXI-Stream】

漫談AMBA總線-AXI4協議的基本介紹

AMBA AXI4接口協議概述

FPGA AXI4協議學習筆記(一)

FPGA AXI4協議學習筆記(一)

評論