現(xiàn)在但凡打開SoC原廠的PCB Layout Guide,都會提及到高速信號的走線的拐角角度問題,都會說高速信號不要以直角走線,要以45度角走線,并且會說走圓弧會比45度拐角更好。

事實(shí)是不是這樣?PCB走線角度該怎樣設(shè)置,是走45度好還是走圓弧好?90度直角走線到底行不行?

大家開始糾結(jié)于PCB走線的拐角角度,也就是近十幾二十年的事情。上世紀(jì)九十年代初,PC界的霸主Intel主導(dǎo)定制了PCI總線技術(shù)。

似乎從PCI接口開始,我們開始進(jìn)入了一個(gè)“高速”系統(tǒng)設(shè)計(jì)的時(shí)代。

電子設(shè)計(jì)和芯片制造技術(shù)按照摩爾定律往前發(fā)展,由于IC制程的工藝不斷提高,IC的晶體管開關(guān)速度也越來越快,各種總線的時(shí)鐘頻率也越來越快,信號完整性問題也在不斷的引起大家的研究和重視。

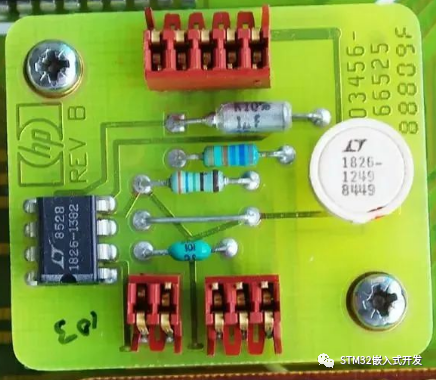

早期PCB拉線菌應(yīng)該還是比較單純,把線路拉通、擼順,整潔、美觀即可,不用去關(guān)注各種信號完整性問題。比如下圖所示的HP經(jīng)典的HP3456A萬用表的電路板,大量的90°角走線,幾乎是故意走的直角,絕大多數(shù)地方?jīng)]有鋪銅。

上面PCB板的右上角,不僅走直角不止,拐彎后,線寬還變小了,會造成信號反射問題,影響信號完整性。

本文跟大家探討一下關(guān)于高頻/高速信號的走線拐角角度問題。我們從銳角到直角、鈍角、圓弧一直到任意角度走線,看看各種走線拐角角度的優(yōu)缺點(diǎn)。

為什么PCB不能以銳角走線?

PCB能不能以銳角走線,答案是否定的。先不管以銳角走線會不會對高速信號傳輸線造成負(fù)面影響,單從PCB DFM方面,就應(yīng)該避免出現(xiàn)銳角走線的情形。

因?yàn)樵赑CB導(dǎo)線相交形成銳角處,會造成一種叫酸角“acid traps”的問題。在PCB制板過程中,在PCB線路蝕刻環(huán)節(jié),在“acid traps”處會造成PCB線路腐蝕過度,帶來PCB線路虛斷的問題。

雖然,我們可以借助CAM 350 進(jìn)行DFF Audit自動(dòng)檢測出“acid traps”潛在問題,避免在PCB在制造產(chǎn)生時(shí)產(chǎn)生加工瓶頸。如果pcb板廠工藝人員檢測到有酸角(acid trap)存在,他們將簡單地貼一塊銅到這個(gè)縫隙中。

很多板廠的工程人員他們其實(shí)并不懂Layout的,他們只是從PCB工程加工的角度修復(fù)酸角(acid trap)的問題,但這種修復(fù)是否能帶來進(jìn)一步的信號完整性問題便不得而知了,所以我們在Layout時(shí)就應(yīng)該從源頭去盡量避免產(chǎn)生酸角(acid trap)。

怎樣避免拉線時(shí)出現(xiàn)銳角,造成acid trap DFM 問題?

現(xiàn)代的EDA設(shè)計(jì)軟件(如Cadence Allegro、Altium Designer等)都帶有了完善的Layout走線選項(xiàng),我們在Layout走線時(shí),靈活運(yùn)用這些輔助選項(xiàng),可以極大的避免我們在Layout時(shí)產(chǎn)生產(chǎn)生“acid trap”現(xiàn)象。

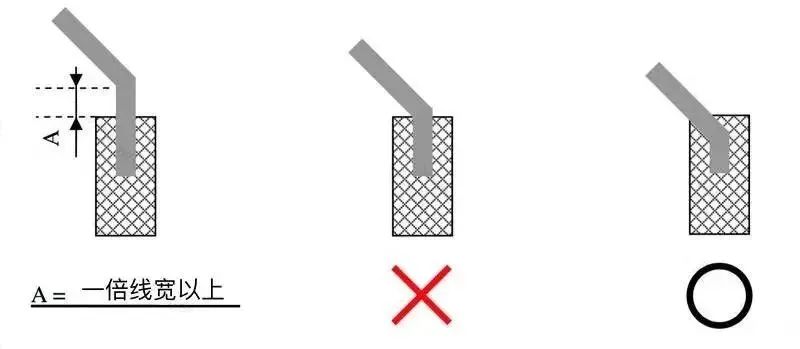

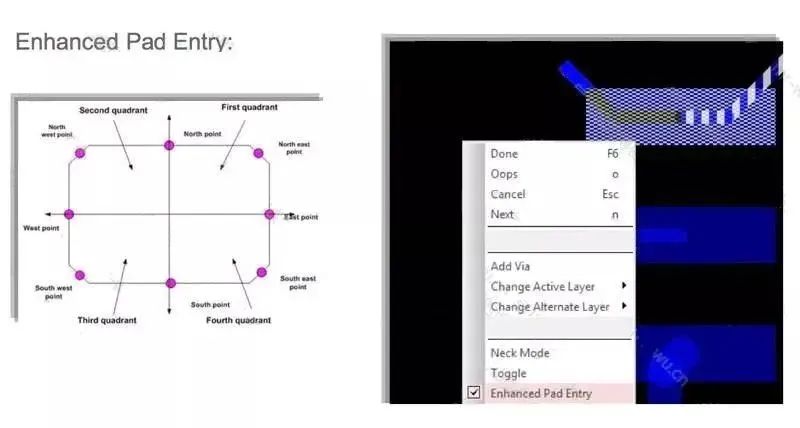

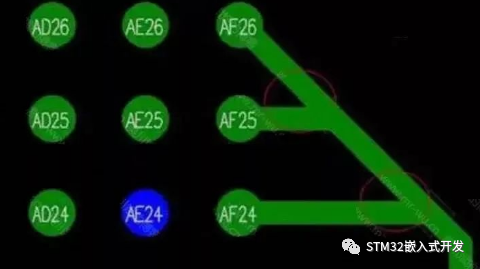

焊盤的出線角度設(shè)置,避免導(dǎo)線與焊盤形成銳角角度的夾角,如下圖示例。

利用 Cadence Allegro 的 Enhanced Pad Entry 功能能夠讓我們在Layout時(shí)盡可能的避免導(dǎo)線與焊盤在出線時(shí)形成夾角,避免造成“acid traps”DFM問題。

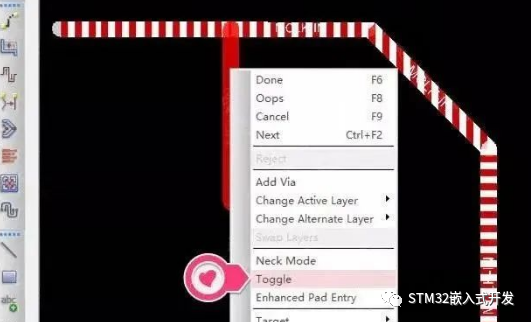

避免兩條導(dǎo)線交叉形成銳角夾角。

靈活應(yīng)用 Cadence Allegro 布線時(shí)切換 ” toggle “ 選項(xiàng),可以避免導(dǎo)線拉出T型分支時(shí)形成銳角夾角,避免造成“acid traps”DFM問題。

PCB Layout能不能以90°走線

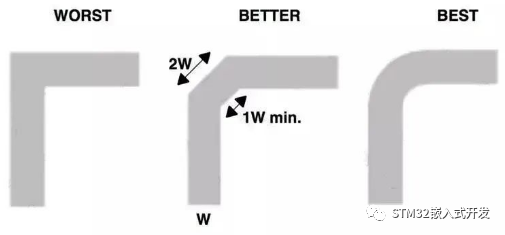

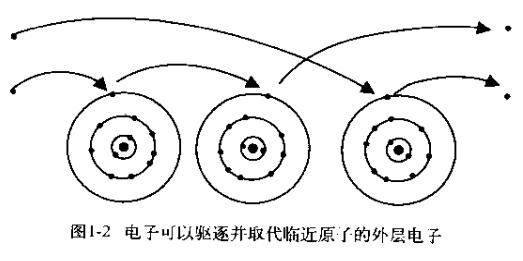

高頻高速信號傳輸線應(yīng)避免以90°的拐角走線,是各種PCB Design Guide中極力要求的,因?yàn)楦哳l高速信號傳輸線需要保持特性阻抗一致,而采用90°拐角走線,在傳輸線拐角處,會改變線寬,90°拐角處線寬約為正常線寬的 1.414倍,由于線寬改變了,就會造成信號的反射。

同時(shí),拐角處的額外寄生電容也會對信號的傳輸造成時(shí)延影響。

當(dāng)然,當(dāng)信號沿著均勻互連線傳播時(shí),不會產(chǎn)生反射和傳輸信號的失真。如果均勻互連線上有一個(gè)90°拐角,則會在拐角處造成PCB傳輸線寬的變化,根據(jù)相關(guān)電磁理論計(jì)算得出,這肯定會帶來信號的反射影響。

直角走線的對信號的影響就是主要體現(xiàn)在三個(gè)方面:

拐角可以等效為傳輸線上的容性負(fù)載,減緩上升時(shí)間

90°拐角處線寬約為正常線寬的 1.414倍,引起阻抗不連續(xù),進(jìn)而造成信號的反射

直角尖端產(chǎn)生的EMI,尖端容易發(fā)射或接收電磁波,產(chǎn)生EMI

傳輸線的直角帶來的寄生電容可以由下面這個(gè)經(jīng)驗(yàn)公式來計(jì)算:

C=61W(Er)1/2/ZO

在上式中,C就是指拐角的等效電容(單位pF),W指走線的寬度(單位inch),Er指介質(zhì)的介電常數(shù),ZO就是傳輸線的特征阻抗。

對于高速數(shù)字信號來說,90°拐角對高速信號傳輸線會造成一定的影響,對于我們現(xiàn)在高密高速pcb來說,一般走線寬度為4-5mil,一個(gè)90°拐角的電容量大約為10fF,經(jīng)測算,此電容引起的時(shí)延累加大約為0.25ps,所以,5mil線寬的導(dǎo)線上的90°拐角并不會對現(xiàn)在的高速數(shù)字信號(100-psec上升沿時(shí)間)造成很大影響。

而對于高頻信號傳輸線來說,為了避免集膚效應(yīng)(Skin effect)造成的信號損壞,通常會采用寬一點(diǎn)的信號傳輸線,例如50Ω阻抗,100mil線寬,這90°拐角處的線寬約為141mil,寄生電容造成的信號延時(shí)大約為25ps,此時(shí),90°拐角將會造成非常嚴(yán)重的影響。

同時(shí),微波傳輸線總是希望能盡量降低信號的損耗,90°拐角處的阻抗不連續(xù)和而外的寄生電容會引起高頻信號的相位和振幅誤差、輸入與輸出的失配,以及可能存在的寄生耦合,進(jìn)而導(dǎo)致電路性能的惡化,影響 PCB 電路信號的傳輸特性。

關(guān)于90°信號走線,老wu自己的觀點(diǎn)是,盡量避免以90°走線

45度外斜切線

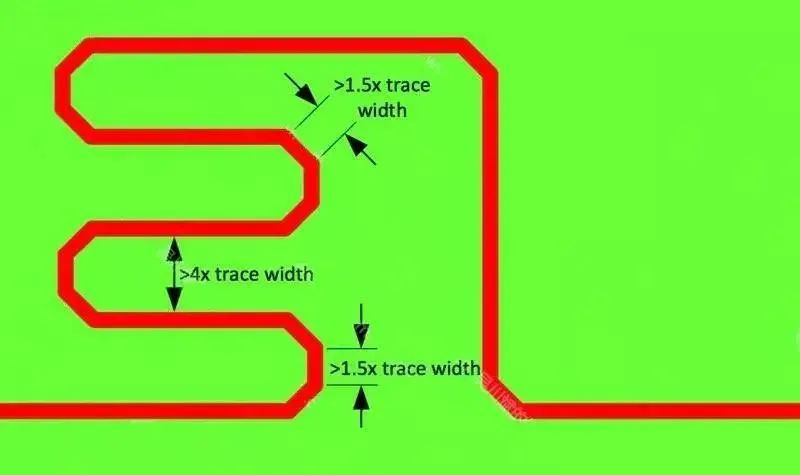

除了射頻信號和其他有特殊要求的信號,我們PCB上的走線應(yīng)該優(yōu)選以45°走線。要注意一點(diǎn)的是,45°角走線繞等長時(shí),拐角處的走線長度要至少為1.5倍線寬,繞等長的線與線之間的間距要至少4倍線寬的距離。

由于高速信號線總是沿著阻抗的路徑傳輸,如果繞等長的線間距太近,由于線間的寄生電容,高速信號走了捷徑,就會出現(xiàn)等長不準(zhǔn)的情況。現(xiàn)代的EDA軟件的繞線規(guī)則都可以很方便的設(shè)置相關(guān)的繞線規(guī)則。

以arc弧形走線

如果不是技術(shù)規(guī)范明確要求要以弧形走線,或者是RF微波傳輸線,個(gè)人覺得,沒有必要去走弧形線,因?yàn)楦咚俑呙芏萈CB的Layout,大量的弧形線后期修線非常麻煩,而且大量的弧形走線也比較費(fèi)空間。

對于類似USB3.1或HDMI2.0這樣的高速差分信號,個(gè)人認(rèn)為還是可以走圓弧線的。

當(dāng)然,對于RF微波信號傳輸線,還是優(yōu)先走圓弧線,甚至是要走“采用 45° 外斜切”線走線。

總結(jié)

隨著4G/5G無線通訊技術(shù)的發(fā)展和電子產(chǎn)品的不斷升級換代,目前PCB數(shù)據(jù)接口傳輸速率已高達(dá)10Gbps或25Gbps以上,且信號傳輸速率還在不斷的朝著高速化方向發(fā)展。隨著信號傳輸?shù)母咚倩⒏哳l化發(fā)展,對PCB阻抗控制和信號完整性提出了更高的要求。

對于PCB板上傳輸?shù)臄?shù)字信號來說,電子工業(yè)界應(yīng)用的包括FR4在內(nèi)的許多電介質(zhì)材料,在低速低頻傳輸時(shí)一直被認(rèn)為是均勻的。

但當(dāng)系統(tǒng)總線上電子信號速率達(dá)到Gbps級別時(shí),這種均勻性假設(shè)不再成立,此時(shí)交織在環(huán)氧樹脂基材中的玻璃纖維束之間的間隙引起的介質(zhì)層相對介電常數(shù)的局部變化將不可忽視,介電常數(shù)的局部擾動(dòng)將使線路的時(shí)延和特征阻抗與空間相關(guān),從而影響高速信號的傳輸。

基于FR4測試基板的測試數(shù)據(jù)表明,由于微帶線與玻纖束相對位置差異,導(dǎo)致測量所得的傳輸線有效介電常數(shù)波動(dòng)較大,值之差可以達(dá)到△εr=0.4。盡管這些空間擾動(dòng)看上去較小,它會嚴(yán)重影響數(shù)據(jù)速度為5-10Gbps的差分傳輸線。

在一些高速設(shè)計(jì)項(xiàng)目中,為了應(yīng)對玻纖效應(yīng)對高速信號的影響,我們可以采用zig-zag routing布線技術(shù)以減緩玻纖效應(yīng)的影響。

Cadence Allegro PCB Editor 16.6-2015 及后續(xù)版本帶來了對zig-zag布線模式的支持。

在Cadence Allegro PCB Editor 16.6-2015 菜單中選擇”Route -> Unsupported Prototype -> Fiber Weave Effect” 打開zig-zag routing功能。

二十年前我們PCB Layout不用關(guān)注是否要走弧形線,不用擔(dān)心PCB板材玻璃纖維對高速信號的影響。

不存在一成不變的PCB Layout規(guī)則,隨著PCB制造工藝的提升和數(shù)據(jù)傳輸速率的提高,有可能現(xiàn)在正確的規(guī)則在將來將變得不再適用。

審核編輯:湯梓紅

-

pcb

+關(guān)注

關(guān)注

4340文章

23333瀏覽量

404673 -

晶體管

+關(guān)注

關(guān)注

77文章

9907瀏覽量

140132 -

信號完整性

+關(guān)注

關(guān)注

68文章

1426瀏覽量

96186 -

走線

+關(guān)注

關(guān)注

3文章

117瀏覽量

24151 -

高速信號

+關(guān)注

關(guān)注

1文章

235瀏覽量

17927

原文標(biāo)題:詳解PCB走線與信號完整性問題

文章出處:【微信號:單片機(jī)與嵌入式,微信公眾號:單片機(jī)與嵌入式】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

常見的信號完整性問題及解決方案

PCB信號完整性搞不定?教你高速信號跳過PCB走線的方法

識別和修復(fù)pcb信號完整性問題

如何克服高速PCB設(shè)計(jì)中信號完整性問題?

如何使用您的PCB走線寬度來改善信號完整性

pcb信號完整性詳解

PCB設(shè)計(jì)中的信號完整性問題

詳解PCB走線與信號完整性問題

詳解PCB走線與信號完整性問題

評論