在半導體行業競爭日趨激烈的背景下,封裝工藝作為一種部署更小型、更輕薄、更高效、和更低功耗半導體的方法,其重要性日益凸顯。同時,封裝工藝也可響應半導體小型化技術的限制和滿足其他市場需求。

封裝工藝是指對半導體制成品進行包裝的過程,使其免受損壞,同時將半導體電路中的電線與外部連接。此前,封裝工藝通常被視為一種簡單的輔助工作,屬于半導體制造的后工序,而非確定半導體質量的前工序。然而,近年來,隨著晶體管的特征尺寸縮小到5nm以下,加之半導體制造業在未來幾年面臨物理尺寸限制的可能性越來越大,封裝技術也得到了前所未有的關注。

封裝工藝關乎半導體產品,是與客戶休戚相關的關鍵工藝。下面我們將詳細探討封裝技術,了解封裝技術的未來趨勢。

對封裝技術的重新思考

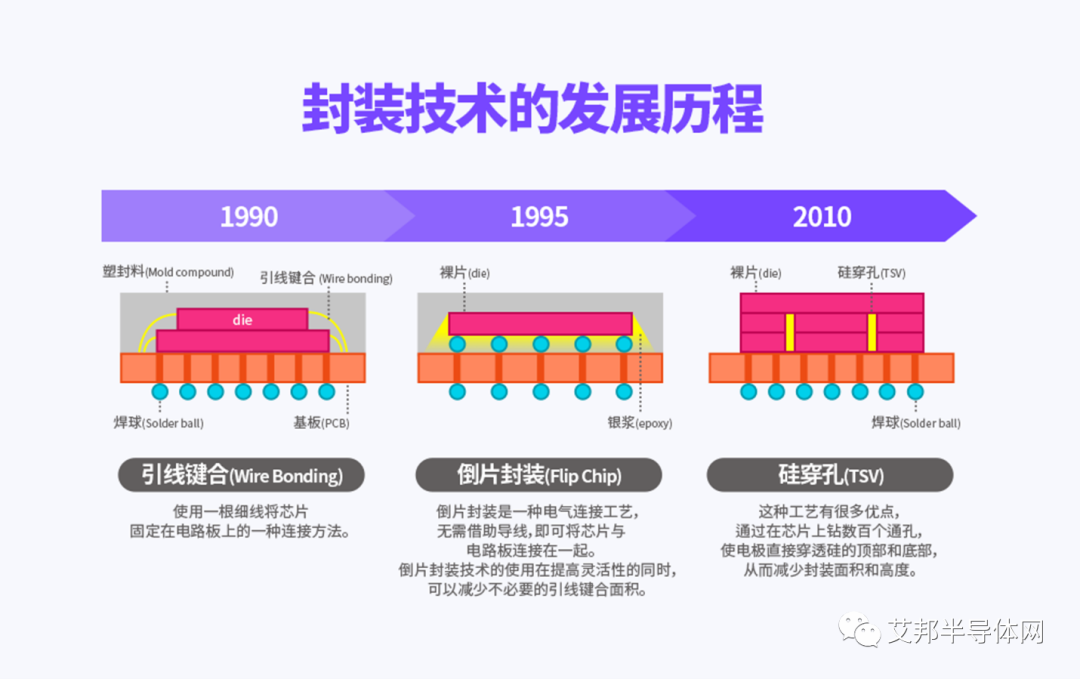

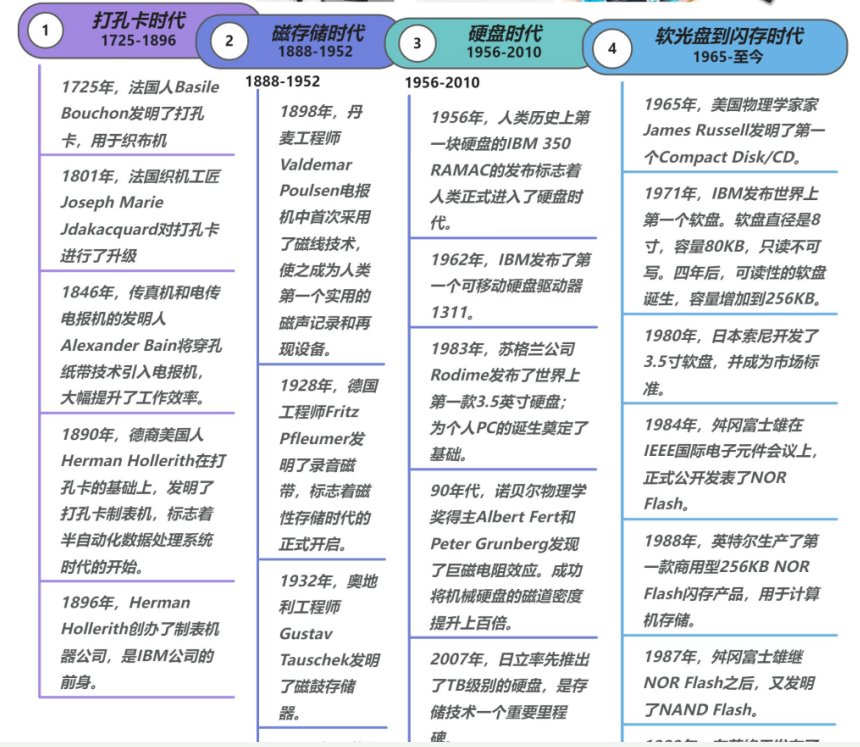

圖1.封裝技術的發展歷程

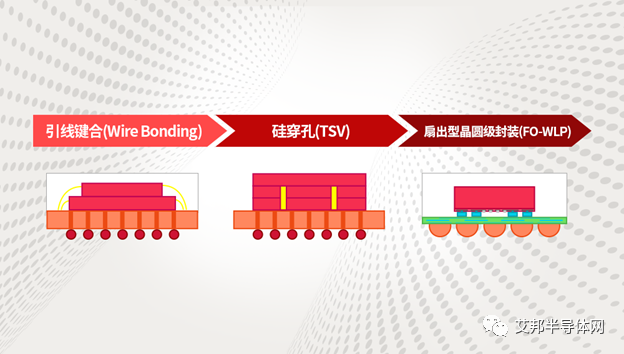

隨著市場對高性能和高容量存儲器產品的需求不斷增加,從十年前開始,諸如*重新分配層(RDL)、*倒片封裝(Flip Chip)和*硅穿孔(TSV)等封裝技術得到了積極廣泛的應用【圖1】。這些技術顛覆了傳統的芯片級封裝方法,在硅晶圓或芯片堆疊結構晶圓中進行工藝處理,大幅提高了產品的性能和容量。需要指出的是,SK海力士憑借業界領先的TSV堆疊技術引領市場發展,這其中包括高帶寬存儲器(HBM)封裝存儲器解決方案,以及用于服務器的高密度存儲器(HDM)三維堆疊(3DS)技術【圖2】。

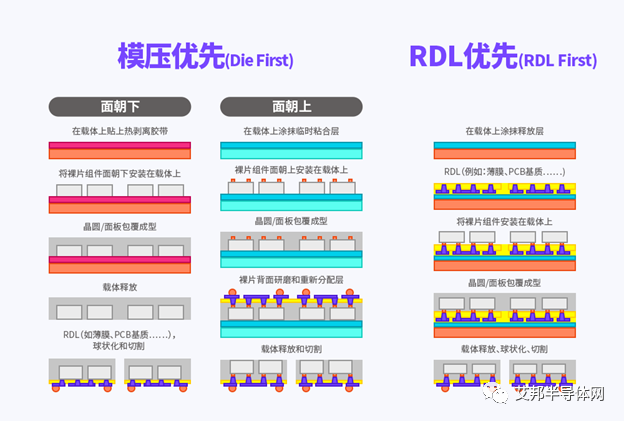

圖2. FO-WLP封裝計劃包含模壓優先選項(die-first)和重新分配層(RDL)優先封裝選項(來源:Micromachines,《EE Times》雜志)

2016年,SK海力士率先應用*批量回流焊(mass reflow)工藝,將4塊50 um厚芯片相互堆疊,并結合TSV堆疊技術,成功開發出一款服務器專用3DS存儲器。近期,公司將這項技術應用于HBM產品的8層堆疊上。通過采用多個熱假凸塊作為散熱路徑,并使用具有優良導熱性的塑封料作為間隙填充材料,SK海力士大大改善了因存儲器帶寬增加而引起的散熱問題,同時也大幅降低了TSV的高昂制造成本。

*重新分配層(Ridistribution Layer,簡稱RDL):一種重新布線技術;RDL技術旨在重新排列已經在晶圓上形成的焊盤,通過形成額外的金屬布線層,將焊盤重塑到所需位置。

*倒片封裝(Flip Chip):在芯片的焊盤上形成凸點(幾十微米(?)大小,稱為焊球),將凸點翻轉然后與基板鍵合的方法

*硅穿孔(Through-siliconvia, 簡稱TSV):一種通過在硅芯片內部鉆孔(通孔)形成通過電極,然后將多個芯片垂直3D堆疊的方法;與引線連接方法相比,該方法封裝面積更小,并且在相同厚度下可以堆疊更多的芯片。此外,由于該方法可以在最短的距離內連接多個I/O,因此可以達到實現高帶寬和降低功耗兩全其美的效果。

*批量回流模制底部填充(Mass reflow molded underfill,簡稱MR-MUF):將多個芯片放置在下層基板上,通過回流焊一次性粘合,然后同時用模塑料填充芯片之間或芯片與基板之間間隙的方法,該方法主要用于倒片封裝和TSV芯片堆疊方法。

存儲器容量需求影響芯片技術

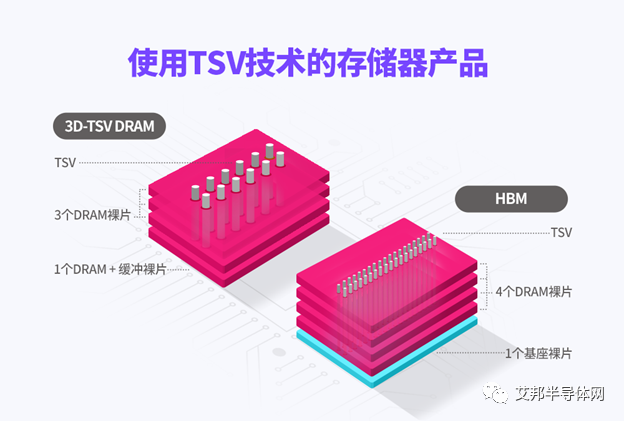

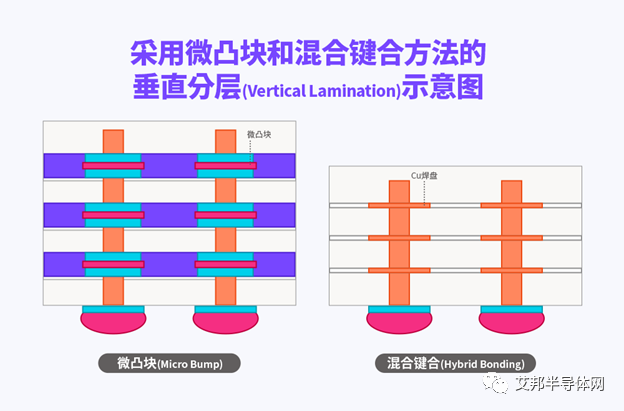

HBM中所使用的TSV技術是一種使用硅穿孔電極(TSV)和微凸塊垂直堆疊多個芯片(通常為4-8個芯片)的方法。由于市場對高容量存儲器產品需求不斷增加,預計未來將需要12-16層甚至更高的多芯片堆疊技術。為了實現這一目標,不僅需要減小芯片的厚度和凸塊電極的尺寸,而且在不久的將來還需要應用混合鍵合(hybrid bonding)技術*,去除芯片之間的填充物,使其直接連接到銅電極上【圖3】。

圖3.使用TSV技術的存儲器產品

與使用微凸塊的方法相比,混合鍵合方法可以大幅縮小電極尺寸,從而增加單位面積上的I/O數量,進而大幅降低功耗。與此同時,混合鍵合方法可以顯著縮小芯片之間的間隙,由此實現大容量封裝。此外,它還可以改善芯片散熱性能,有效地解決因耗電量增加而引起的散熱問題。

*混合鍵合:一種同時鍵合金屬電極(如銅電極)和無機絕緣層的方法;該方法可以將至少兩個不同的芯片集成到同一個封裝中,縮小互連間距,有望廣泛應用于芯片(SoC)裸片、SoC存儲器和存儲器上的多系統垂直堆疊。

平衡容量與熱量生成

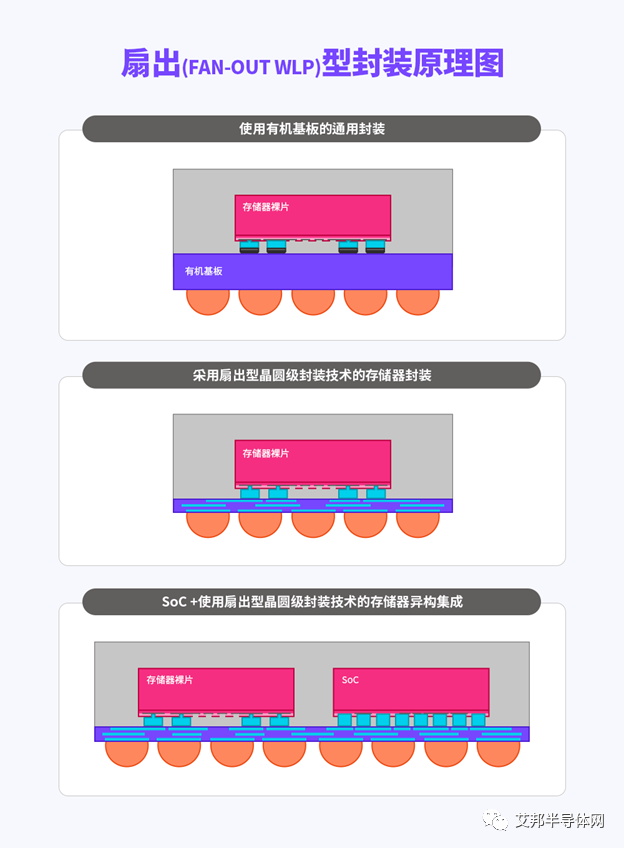

除了需要TSV技術在容量方面的創新外,人們還需要高速芯片和存儲器芯片的*異構集成解決方案,以最大限度地發揮系統內存儲器產品的特性。此外,人們還需要全新封裝解決方案,來解決因存儲器芯片功率增加而引起的散熱問題,以及因堆疊的存儲器芯片數量增加而產生的厚度限制要求。*扇出型晶圓級封裝(Fan-out WLP)是一種通過使用晶圓級重新布線技術將芯片的I/O焊盤遷移到芯片外部區域的技術。這種先進的封裝技術目前被積極應用于應用處理器(AP)和電源管理芯片(PMIC)等非存儲器芯片上。該技術可以使用重新分配層來替代基板,從而減小封裝厚度。此舉還可以改善芯片散熱效果,因此人們正在積極研究將這一技術應用于存儲器產品的可行性。

此外,為了解決存儲器裝置的技術縮減限制和功率消耗問題,目前人們正在積極研究異構芯片(而非存儲器芯片)集成技術。通過采用扇出型封裝技術可以在不同形式的封裝中實現上述目標,不僅提高了存儲器產品的性能,而且可以通過新的應用場景實現擴展【圖4】。

圖4.采用微凸塊和混合鍵合方法的垂直分層(Vertical Lamination)示意圖

扇出型封裝技術可以與包括引線鍵合、 TSV、重新分配和凸塊技術等在內的各種封裝技術相融合,對各種形式的存儲器產品進行封裝。由于存儲器芯片需要足夠的容量,扇出型晶圓級封裝結構將成為一項關鍵實施技術,能夠實現垂直堆疊。除了通用的扇出型RDL技術外,存儲器產品的扇出型晶圓級封裝還必須從多個堆疊芯片的I/O垂直連接扇出RDL布線,因此,確保電氣特性和布線質量至關重要。

圖5.扇出(fan-out WLP)型晶圓級封裝示意圖

*異構集成解決方案(Heterogeneous Integration Solution):一種在同一封裝中部署不同類型(異構)器件的方法

*扇出型晶圓級封裝(Fan-out wafer-level packaging, 簡稱Fan-out WLP):通過擴展芯片,在外部區域形成一個用于外部連接的球狀端子。這種方法無需使用PCB基板,可以減小封裝厚度,節約PCB基板成本。此外,這種方法還可以通過重新分配,簡化在水平方向上橋接異構芯片的操作,因而可以用于多功能和高性能的存儲器系統中。

封裝轉型,促進增長

研究發現,使用TSV技術和扇出型技術的3D堆疊技術預計將分別以每年20%和15%的速度增長。這也表明,這些都是高端封裝領域的代表性技術。TSV和扇出型晶圓級封裝技術正在不斷發展完善,以便更好地消除當前存儲器產品面臨的各種局限性。

編輯:黃飛

-

存儲器

+關注

關注

38文章

7637瀏覽量

166539 -

封裝技術

+關注

關注

12文章

575瀏覽量

68471

原文標題:高端封裝技術:攻克存儲器系統性能和容量限制

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

封裝技術的發展歷程 存儲器容量需求是否影響芯片技術

封裝技術的發展歷程 存儲器容量需求是否影響芯片技術

評論