3 阻性負載的反射

傳輸線的終端匹配有三種特殊情況:開路、短路、終端阻抗和傳輸線阻抗匹配。

情況一:終端開路(假設(shè)傳輸線阻抗是50R)

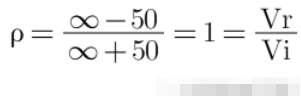

當傳輸線終端開路,則傳輸線模末端的瞬態(tài)阻抗是無群大,此時反射系數(shù)是:

即當信號到達傳輸線的終端時,在終端將產(chǎn)生與入射波大小相同,方向相反,返回源端的反射波。在終端看到的波形是入射波形的2倍(入射波形+反射波形)

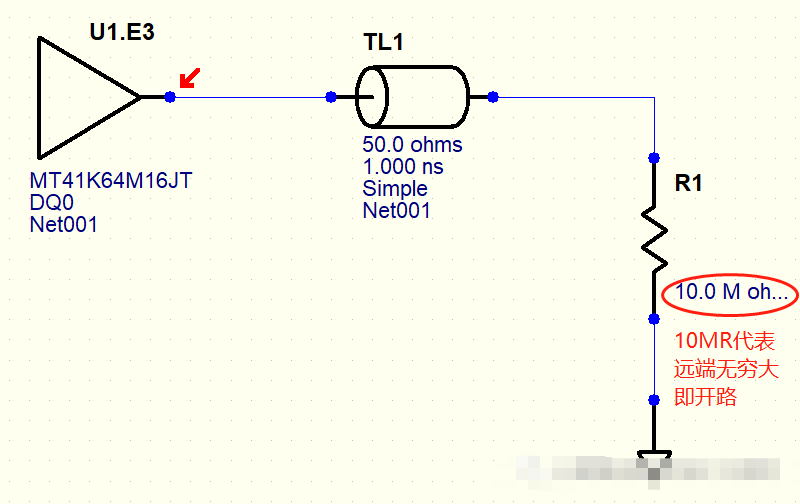

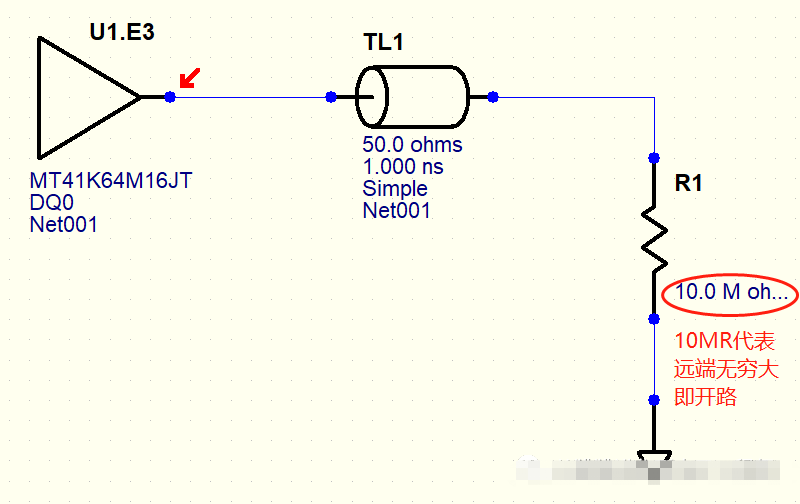

如下圖是一個簡單的仿真電路,R1賦值10MR,用來表示終端開路。本案例中LPDDR3的E3 pin(DQ0)是輸出pin。

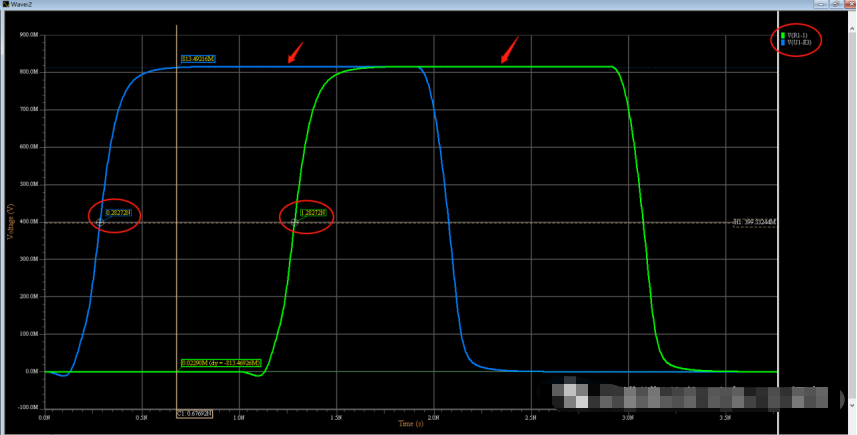

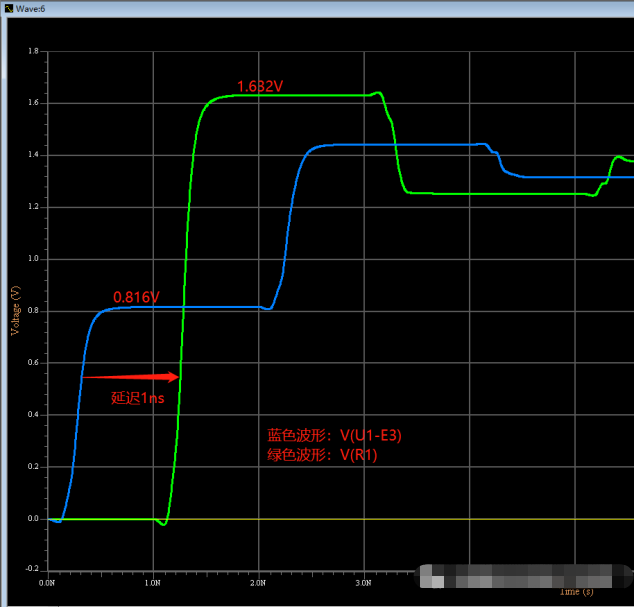

下圖是仿真結(jié)果。藍色是源端輸出的波形,也被稱為入射電壓。綠色是終端的波形。就像上面計算的那樣,入射電壓是0.816V。同時因為終端開路,因此在終端會產(chǎn)生一個0.816V的反射電壓,導致在終端看到的總電壓是入射電壓和反射電壓之和(1.632V)。另外,因為設(shè)計傳輸線延遲在1ns,藍色信號和綠色信號之間的延遲也差不多是1ns。

情況二:終端短路(假設(shè)傳輸線阻抗是50R)

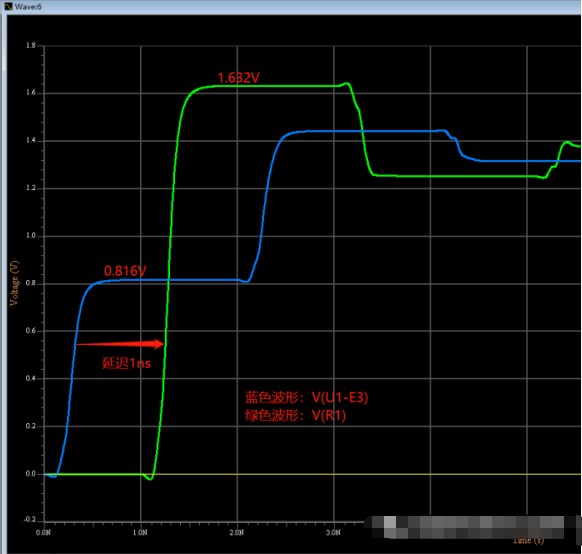

當傳輸線終端短路,則傳輸線模末端的瞬態(tài)阻抗是0,此時反射系數(shù)是:

即1V入射信號到達遠端時,將產(chǎn)生-1V反射信號,向源端傳播。短路突變處的電壓為入射電壓和反射電壓之和,即1V-(-1V)=0V。

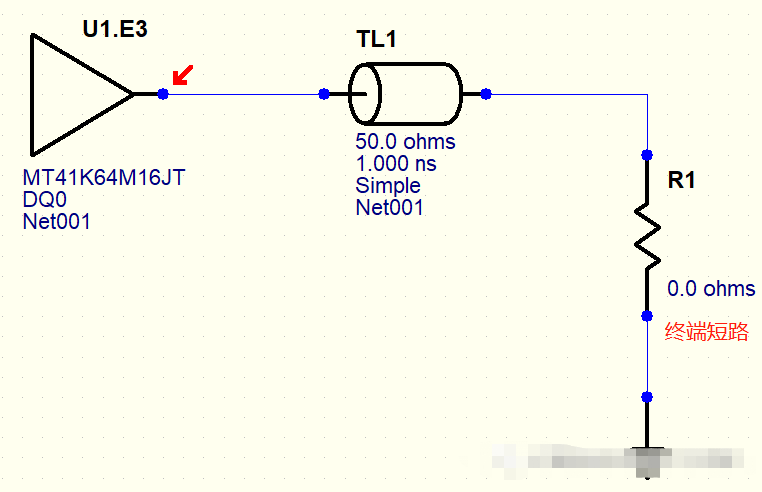

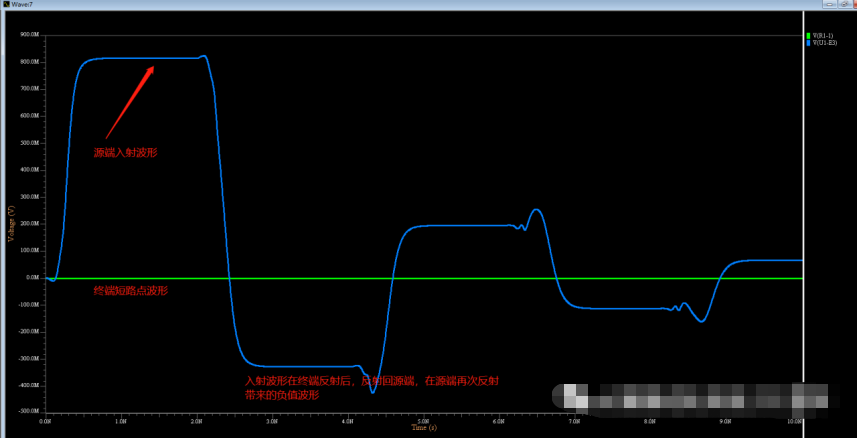

如下是終端短路的電路仿真,R1=0R,代表終端短路。

從仿真結(jié)果看:終端信號為0V,因為終端的信號端和返回平面端(地)是短路的。同時入射信號在終端阻抗短路處發(fā)生反射,反射波形回到源端,遇到源端內(nèi)阻,再次被反射,產(chǎn)生一個負電壓。

情況三:終端阻抗和傳輸線阻抗匹配

當終端阻抗和傳輸線阻抗匹配時,此時反射系數(shù)為:

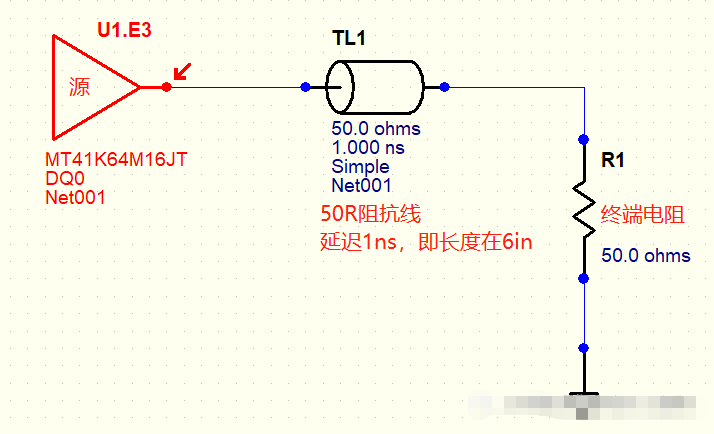

沒有反射信號,終端電阻兩端的電壓就是入射信號。如下圖是使用Hyperlynx做的簡單仿真。U1是某個LPDDR3的DQ0,在本仿真中做輸出。經(jīng)過一段阻抗為50R的傳輸線(此段線帶來的信號延遲是1ns),終端是一個50R的電阻。

通過仿真結(jié)果可以看到(1)終端電壓和入射電壓幅度一致,為813mV,沒有反射。(2)入射電壓和終端電阻電壓有1ns的信號延遲。

總之:當末端為一般性阻性負載時,信號在終端感受到的瞬態(tài)阻抗在0~無群大之間,反射系數(shù)在1~-1之間。

4 驅(qū)動源的內(nèi)阻

驅(qū)動源總是存在內(nèi)阻。典型的CMOS器件,內(nèi)阻大約在5R~20R之間。內(nèi)阻對進入傳輸線的初始電壓和后來的多次反射電壓都有影響。例如當反射波最終到達源端時,會將源端的輸出阻抗(內(nèi)阻)作為瞬態(tài)阻抗,此阻抗決定反射波再次反射回負載端的情況。

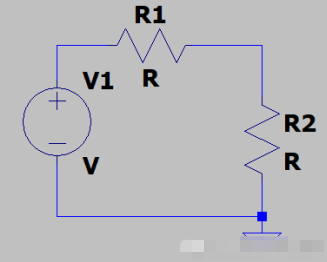

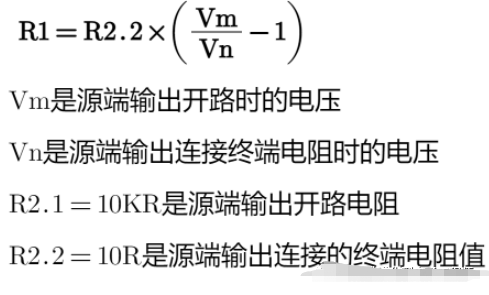

怎么知道源端的內(nèi)阻是多大呢?假設(shè)V1是信號源,R1是信號源內(nèi)阻,R2是外部負載。

通過SPICE或者IBIS模型可以計算得到R1的值。分別仿真R2=10KR和R2=10R時的輸出電壓。

例如某芯片的一根信號源,進行仿真。當連接R2.1時,Vm=3.3V。當連接R2.2時,Vn=1.9V。由上述公式計算得知R1=7.3R。

5 反彈圖

因為內(nèi)阻的存在,初始進入傳輸線的信號是源內(nèi)阻和傳輸線特性阻抗的分壓。當分壓后的信號到達負載端,如果負載端阻抗不匹配,有部分信號被反射回源端。這些反射回源端的信號到達源端后,會再次被反射,疊加在原始信號上又被傳到負載端,而后再次被反射。就這樣循環(huán)下去。

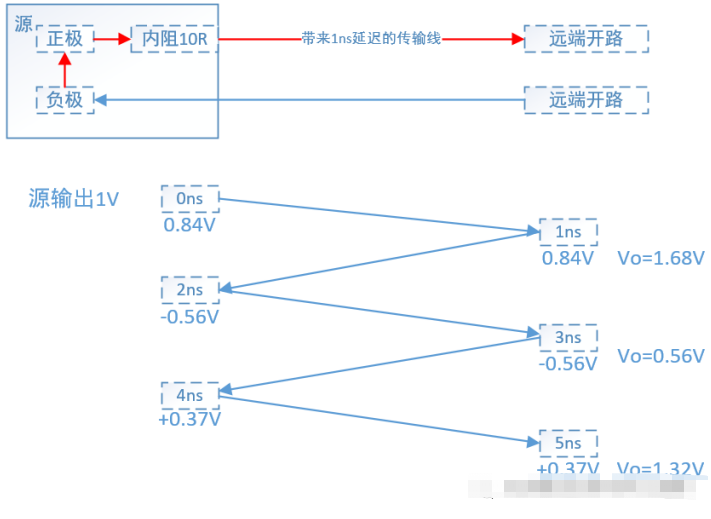

舉例,假設(shè)源端輸出電壓是1V,源內(nèi)阻是10R,傳輸線阻抗是50R,考慮負載端是開路的極端情況,步驟分析如下

(1)剛開始,有1Vx50/(10+50)=0.84V的電壓進入50R傳輸線。這個0.84V就是沿傳輸線傳播的初始入射電壓。

(2)1ns時間到,0.84V的電壓到達負載端,之前已經(jīng)說過假設(shè)負載端是開路的。此時反射系數(shù)是1,反射電壓=入射電壓=0.84V。即有0.84V的反射電壓開始向這源端反射回去。此時在負載端(開路端)測得總電壓為0.84V+0.84V=1.68V

(3)又過了1ns,被反射回來的0.84V反射波回到源端,在源端遇到阻抗匹配,再次被反射。此時源端的反射系數(shù)是(10-50)/(10+50)=-0.67,即此時由被負載端反射回源端的0.84V在源端再次反射的電壓是0.84Vx(-0.67)=-0.56V。這個-0.56V被傳回負載端。

(4)又過了1ns,此時已經(jīng)是第3ns了,-0.56V的波到達負載端,并且又被反射回源端。同時在負載端測試到由此-0.56V產(chǎn)生的波是(-0.56v)+(-0.56v)=-1.12V。此時的-1.12V疊加上之前的1.68V,第3ns時在開路端測量到的波形是1.68V-1.12V=0.56V。

(5)再過1ns,即第4ns時,反射波(-0.56V)回到源端,產(chǎn)生的反射電壓是+0.37V。

(6)再過1ns,+0.37V的源端反射電壓到達負載端,產(chǎn)生負載端新的反射電壓+0.37V。此時已經(jīng)是第5ns,此時負載端的總電壓是0.56V+0.37+0.37V=1.3V。

(7)如此繼續(xù)循環(huán)反射下去。

(8)最終輸出端電壓會趨向于源端電壓1V,畢竟終端最終是開路的。

當源內(nèi)阻小于傳輸線的特性阻抗時,源端出現(xiàn)負反射,這會引起振鈴現(xiàn)象。在此過程中,部分時間點的輸出開路電壓大于源電壓。多出來的電壓是由于傳輸線的寄生電感和寄生電容諧振產(chǎn)生的。

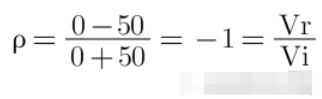

如下圖是一個仿真電路來模擬終端開路時的反射過程。本案例中LPDDR3的E3 pin(DQ0)是輸出pin。

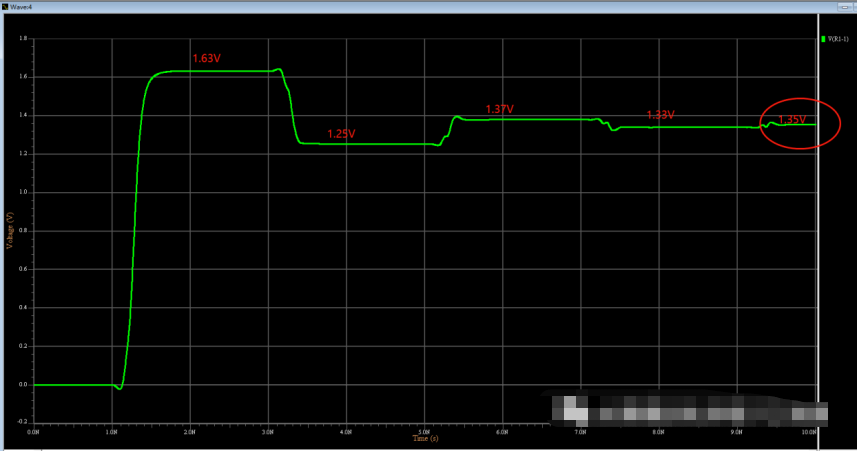

(一)下圖中綠色波形是終端電阻上的波形。結(jié)果顯示有振鈴,電壓幅度按照上述步驟所述的隨著時間在變化(注:本仿真案例中的LPDDR3的信號入射電壓和上述步驟中案例的信號入射電壓不同,內(nèi)阻也不同,因此在電壓上沒有一一對應(yīng)關(guān)系,此處只是表示每一步的趨勢是一致的)。當然因為遠端是開路的,隨著時間的推移,最終遠端的電壓值會和源端電壓一致。因為仿真選擇的MT41K64M16JT是LPDDR3,1.35V供電。因此其輸出的Data是1.35V。

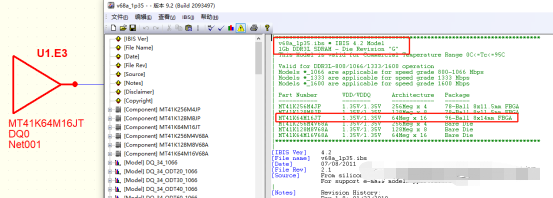

下圖是MT41K64M16JT的IBIS模型,顯示為1.35V的IO口電壓。

(二)下圖表示源端發(fā)出信號(入射電壓),在1ns之后到遠端的情況。和上述步驟(1)(2)對應(yīng)。下圖我只截取前面幾個納秒的波形。有興趣的人可以試著自己做個仿真,得到完整的仿真波形。結(jié)合上述的反射圖步驟,看看源端和終端波形在每一步是什么幅度,怎么計算出來的。

-

阻抗匹配

+關(guān)注

關(guān)注

14文章

358瀏覽量

31434 -

信號完整性

+關(guān)注

關(guān)注

68文章

1445瀏覽量

96770 -

波形

+關(guān)注

關(guān)注

3文章

390瀏覽量

32348 -

反射

+關(guān)注

關(guān)注

0文章

69瀏覽量

16065 -

傳輸線

+關(guān)注

關(guān)注

0文章

382瀏覽量

24682

發(fā)布評論請先 登錄

信號完整性(五):信號反射

信號完整性簡介及protel信號完整性設(shè)計指南

信號完整性與電源完整性的仿真

信號完整性之反射(一)

信號完整性之反射(二)

信號完整性之反射(二)

評論