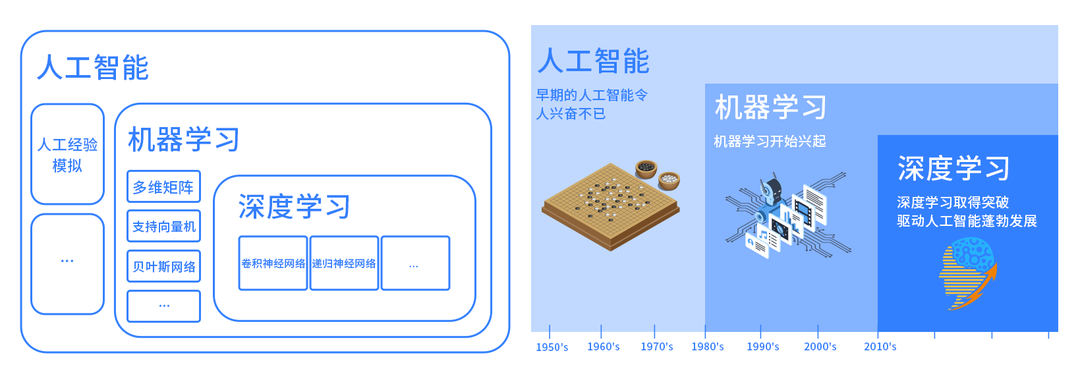

隨著人工智能技術(shù)的不斷發(fā)展,機(jī)器學(xué)習(xí)和深度學(xué)習(xí)已經(jīng)成為當(dāng)今最熱門的話題之一。它們可以應(yīng)用于各種場景,從醫(yī)療保健到自動駕駛,從金融分析到自然語言處理,都有著廣泛的應(yīng)用。在這些應(yīng)用場景中,計(jì)算和數(shù)據(jù)傳輸是機(jī)器學(xué)習(xí)和深度學(xué)習(xí)的核心需求,但同時(shí)也是面臨的挑戰(zhàn)之一。

首先,機(jī)器學(xué)習(xí)和深度學(xué)習(xí)的計(jì)算需求是非常高的。這些技術(shù)需要進(jìn)行大規(guī)模的矩陣乘法、向量加法和激活函數(shù)計(jì)算、卷積、循環(huán)神經(jīng)網(wǎng)絡(luò)等復(fù)雜的運(yùn)算。這些運(yùn)算需要大量的計(jì)算資源,包括高性能計(jì)算機(jī)、CPU、APU、GPU加速器、FPGA等等。同時(shí),這些計(jì)算資源的能力和效率也是限制計(jì)算速度的關(guān)鍵因素。

其次,機(jī)器學(xué)習(xí)和深度學(xué)習(xí)的數(shù)據(jù)傳輸需求也非常高。大規(guī)模的數(shù)據(jù)集需要被傳輸?shù)接?jì)算機(jī)中進(jìn)行處理,這對數(shù)據(jù)傳輸?shù)乃俣群涂煽啃蕴岢隽藰O高的要求。傳統(tǒng)的數(shù)據(jù)傳輸技術(shù),如以太網(wǎng)、PCIe等高速SerDes接口,已經(jīng)變成主流以滿足大量數(shù)據(jù)傳輸及資料傳輸?shù)男枨蟆?/p>

最后,機(jī)器學(xué)習(xí)和深度學(xué)習(xí)面臨的挑戰(zhàn)還包括數(shù)據(jù)安全、數(shù)據(jù)隱私等方面的問題。這些問題需要高性能計(jì)算和可靠數(shù)據(jù)傳輸?shù)闹С郑瑫r(shí)也需要更高級的安全技術(shù)來保護(hù)數(shù)據(jù)的安全性和隱私性。

為了解決這些問題,芯片接口IP成為了關(guān)鍵的技術(shù)支撐。

1、支持高帶寬和低延遲的數(shù)據(jù)傳輸

為了支持機(jī)器學(xué)習(xí)和深度學(xué)習(xí)的數(shù)據(jù)傳輸需求,芯片接口IP需要提供高帶寬和低延遲的數(shù)據(jù)傳輸能力。這可以通過采用高速串行接口技術(shù)來實(shí)現(xiàn),如PCIe接口,以提供更高的數(shù)據(jù)傳輸速率和吞吐量。PCIe接口是一種點(diǎn)對點(diǎn)的串行高速接口,可以支持多個通道和多個傳輸速率。采用PCIe接口可以在吞吐量和延遲之間取得平衡,并提供高效和可靠的數(shù)據(jù)傳輸。

2. 支持高速并行計(jì)算和處理

為了支持機(jī)器學(xué)習(xí)和深度學(xué)習(xí)的計(jì)算需求,芯片接口IP需要提供高速并行計(jì)算和處理能力。這可以通過采用多核處理器和高速總線架構(gòu)來實(shí)現(xiàn),以支持復(fù)雜的計(jì)算任務(wù)和數(shù)據(jù)處理需求。同時(shí),采用硬件加速器和定制化指令集,可以進(jìn)一步提高計(jì)算效率和性能。這些技術(shù)通常會被集成到芯片內(nèi)部,以提供更高的計(jì)算和處理性能,接口IP提供的可編程接口和配置選項(xiàng),可以幫助客戶根據(jù)具體的應(yīng)用場景進(jìn)行優(yōu)化和定制化,以滿足不同的需求。

為了滿足機(jī)器學(xué)習(xí)和深度學(xué)習(xí)的計(jì)算需求,芯片接口IP需要提供高速并行計(jì)算和處理能力。多核架構(gòu)是實(shí)現(xiàn)這一目標(biāo)的一種方式,包括同構(gòu)和異構(gòu)架構(gòu)。在同構(gòu)架構(gòu)中,通過高速接口和先進(jìn)的封裝技術(shù),將多個相同的處理器核心緊密相連,以實(shí)現(xiàn)計(jì)算能力的擴(kuò)展。這種架構(gòu)適用于CPU、TPU、AI SoC等,接口要求低延遲和低誤碼率。在異構(gòu)架構(gòu)中,芯片按功能拆分,先進(jìn)制程的Die提供高算力和性能,成熟制程的Die負(fù)責(zé)常規(guī)或特色的功能,它們被封裝在一起。不同類型的處理器核心可以配合工作,如CPU、GPU、DSP等,這樣可以實(shí)現(xiàn)異構(gòu)計(jì)算,進(jìn)一步提高系統(tǒng)的性能和功效。

在多核架構(gòu)中,D2D IP是非常重要的。一方面,它可以提高系統(tǒng)的集成能力。多核架構(gòu)需要集成多個處理器核心、內(nèi)存控制器、外圍接口等組件,這些組件的設(shè)計(jì)和實(shí)現(xiàn)需要大量的芯片設(shè)計(jì)資源。通過采用D2D IP,可以連接這些預(yù)先設(shè)計(jì)好、經(jīng)過驗(yàn)證、可重用的組件,從而節(jié)省開發(fā)時(shí)間和成本,并且可以提高系統(tǒng)的可靠性和穩(wěn)定性。另一方面,D2D IP可以幫助設(shè)計(jì)人員實(shí)現(xiàn)不同類型處理器核心之間的協(xié)作和數(shù)據(jù)傳輸,促進(jìn)異構(gòu)計(jì)算的實(shí)現(xiàn)。同時(shí),D2D IP也可以用在同類型的核的擴(kuò)展,實(shí)現(xiàn)同構(gòu)計(jì)算的算力提升。因此,D2D IP在多核架構(gòu)中具有重要作用,可以提高系統(tǒng)的集成能力和計(jì)算性能,同時(shí)也支持異構(gòu)和同構(gòu)計(jì)算的實(shí)現(xiàn)。這些技術(shù)的應(yīng)用需要精確的設(shè)計(jì)和實(shí)現(xiàn),以確保系統(tǒng)的穩(wěn)定性和可靠性。

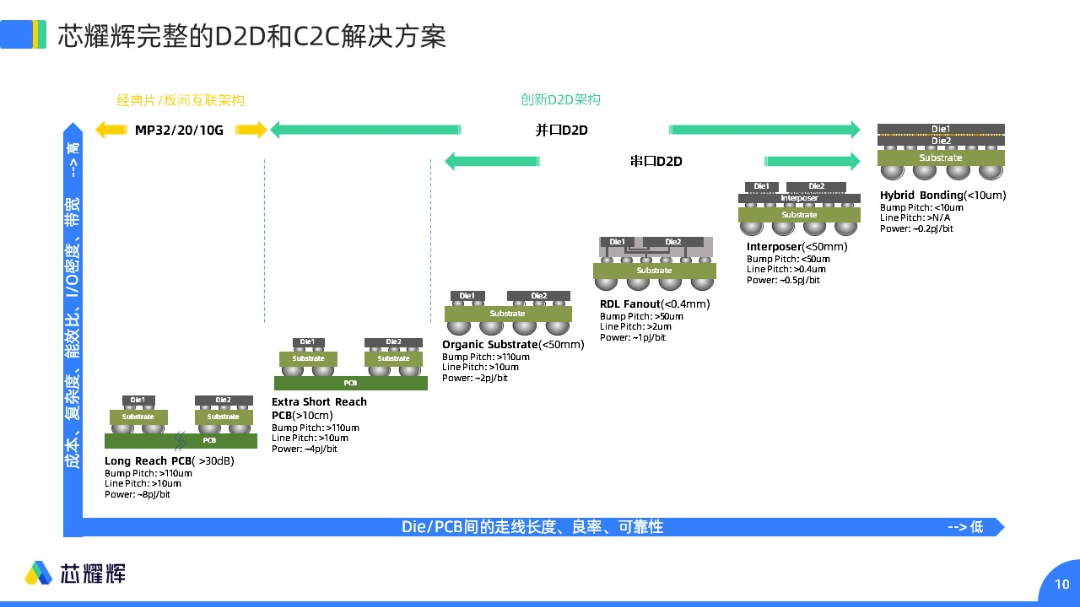

芯耀輝完整的D2D和C2C解決方案

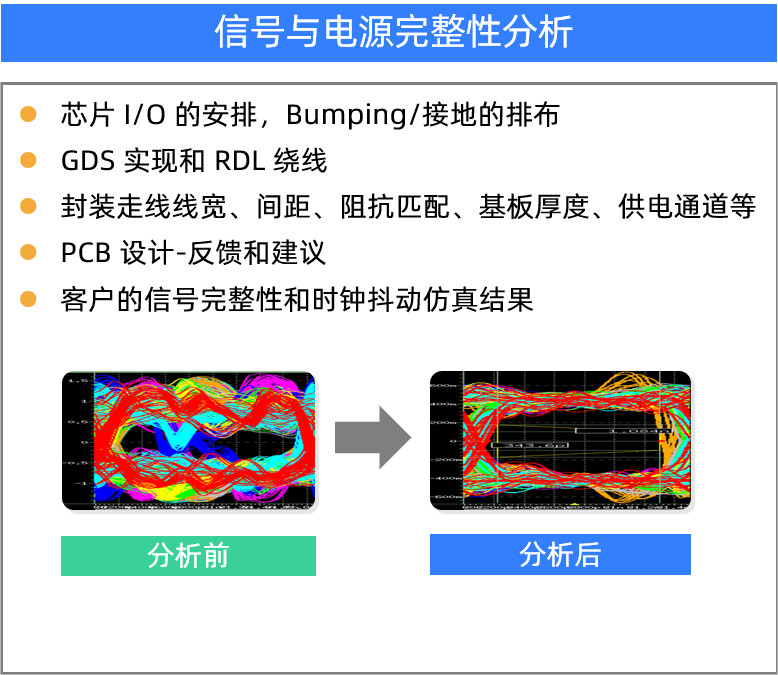

3. 提供多種接口和協(xié)議支持為了滿足不同的機(jī)器學(xué)習(xí)和深度學(xué)習(xí)應(yīng)用的需求,芯片接口IP需要支持多種協(xié)議及功能的高速接口IP。例如,網(wǎng)絡(luò)協(xié)議、PCIe和DDR等協(xié)議,這些協(xié)議定義了數(shù)據(jù)傳輸?shù)母袷健鬏斔俾省㈠e誤處理等方面內(nèi)容,以確保芯片接口IP可以與不同的系統(tǒng)和設(shè)備進(jìn)行交互和通信。其中,以太網(wǎng)是一種常見的網(wǎng)絡(luò)通信協(xié)議,用于在計(jì)算機(jī)網(wǎng)絡(luò)中進(jìn)行數(shù)據(jù)傳輸和通信;PCIe是一種高速串行總線協(xié)議,用于連接計(jì)算機(jī)主板和各種外部設(shè)備,如顯卡、網(wǎng)卡、固態(tài)硬盤等;DDR是一種常見的內(nèi)存協(xié)議,用于在計(jì)算機(jī)系統(tǒng)中進(jìn)行數(shù)據(jù)存儲和讀取。 4. 支持定制化和靈活性由于機(jī)器學(xué)習(xí)和深度學(xué)習(xí)的應(yīng)用場景和需求非常多樣化和復(fù)雜化,因此芯片接口IP需要具有較高的定制化和靈活性,以便滿足不同應(yīng)用的需求。為了進(jìn)一步提升芯片的價(jià)值和競爭力,接口IP廠商還可以提供一些增值服務(wù),例如子系統(tǒng)服務(wù)、SIPI服務(wù)等。其中,子系統(tǒng)服務(wù)是指采用適合的接口IP并針對某個具體應(yīng)用場景或客戶系統(tǒng)需求設(shè)計(jì)的一套完整接口解決方案,可以幫助客戶快速開發(fā)和實(shí)現(xiàn)相應(yīng)的產(chǎn)品。SIPI則是指信號完整性和電源完整性,它主要分析和優(yōu)化信號和電源的噪聲、干擾和失真等問題和性能,以確保芯片在高速運(yùn)行時(shí)能夠保持穩(wěn)定和可靠的性能。SIPI服務(wù)包括芯片I/O的安排、Bumping/接地的排布、PCB設(shè)計(jì)、封裝等,可以幫助設(shè)計(jì)人員在芯片設(shè)計(jì)的早期階段就發(fā)現(xiàn)和解決潛在的SIPI問題,幫助他們制定或改進(jìn)架構(gòu)。

芯耀輝的SIPI服務(wù)

芯片接口IP在支持機(jī)器學(xué)習(xí)和深度學(xué)習(xí)的計(jì)算和數(shù)據(jù)傳輸方面發(fā)揮著重要作用。芯耀輝作為領(lǐng)先的芯片接口IP提供商,提供支持高帶寬和低延遲的數(shù)據(jù)傳輸、支持高速并行計(jì)算和處理、提供多種接口和協(xié)議支持、支持高度定制化和靈活性的接口IP,如芯耀輝的多協(xié)議接口IP、完整的Chiplet D2D解決方案和DDR5/4 PHY IP,可以應(yīng)用于物聯(lián)網(wǎng)、云計(jì)算、數(shù)據(jù)中心、高性能計(jì)算等領(lǐng)域。這些特性和服務(wù)可以幫助客戶更快速地實(shí)現(xiàn)芯片設(shè)計(jì)和開發(fā),同時(shí)也可以提高芯片的可靠性和穩(wěn)定性,減少后期的設(shè)計(jì)和驗(yàn)證工作。因此,芯耀輝的接口IP在機(jī)器學(xué)習(xí)和深度學(xué)習(xí)等領(lǐng)域具有重要的作用和效益,可以幫助客戶實(shí)現(xiàn)高性能、高可靠性和靈活性的芯片設(shè)計(jì),推動技術(shù)的創(chuàng)新和發(fā)展。

審核編輯 :李倩

-

數(shù)據(jù)傳輸

+關(guān)注

關(guān)注

9文章

2008瀏覽量

65795 -

機(jī)器學(xué)習(xí)

+關(guān)注

關(guān)注

66文章

8495瀏覽量

134200 -

深度學(xué)習(xí)

+關(guān)注

關(guān)注

73文章

5557瀏覽量

122554

原文標(biāo)題:芯科普 | 芯片接口IP如何支持機(jī)器學(xué)習(xí)和深度學(xué)習(xí)的計(jì)算和數(shù)據(jù)傳輸?

文章出處:【微信號:AkroStar-Tech,微信公眾號:芯耀輝科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

【OK210申請】無線數(shù)據(jù)傳輸模塊設(shè)計(jì)

汽車行駛記錄儀的數(shù)據(jù)傳輸設(shè)計(jì)

【uFun試用申請】智能小車定點(diǎn)配送和數(shù)據(jù)傳輸

USB數(shù)據(jù)傳輸接口電路設(shè)計(jì)

DMA進(jìn)行數(shù)據(jù)傳輸和CPU進(jìn)行數(shù)據(jù)傳輸的疑問

數(shù)據(jù)傳輸介質(zhì)

基于USB接口的無線數(shù)據(jù)傳輸系統(tǒng)設(shè)計(jì)

tcp ip 數(shù)據(jù)傳輸

數(shù)據(jù)傳輸速率是什么意思

工業(yè)控制領(lǐng)域基于TCP/IP的數(shù)據(jù)傳輸方案

3針M5公頭接口速度和數(shù)據(jù)傳輸效率怎樣

以太網(wǎng)接口的數(shù)據(jù)傳輸原理詳解

pcie在深度學(xué)習(xí)中的應(yīng)用

PD芯片智能充電與數(shù)據(jù)傳輸交互

芯片接口IP如何支持機(jī)器學(xué)習(xí)和深度學(xué)習(xí)的計(jì)算和數(shù)據(jù)傳輸?

芯片接口IP如何支持機(jī)器學(xué)習(xí)和深度學(xué)習(xí)的計(jì)算和數(shù)據(jù)傳輸?

評論