在開始芯片測試流程之前應先充分了解芯片的工作原理。要熟悉它的內部電路,主要參數指標,各個引出線的作用及其正常電壓。芯片很敏感,所以測試的時候要注意不要引起引腳之間的短路,任何一瞬間的短路都能被捕捉到,從而造成芯片燒壞。本篇文章納米軟件小編將帶大家全方位了解IC芯片測試流程及IC芯片自動化測試平臺。

1、晶圓測試(wafertest)

是在晶圓從晶圓廠生產出來后,切割減薄之前的測試。其設備通常是測試廠商自行開發制造或定制的,一般是將晶圓放在測試平臺上,用探針探到芯片中事先確定的測試點,探針上可以通過直流電流和交流信號,可以對其進行各種電氣參數測試。

2、芯片測試(chiptest)

是在晶圓經過切割、減薄工序,成為一片片獨立的chip之后的測試。其設備通常是測試廠商自行開發制造或定制的,一般是將晶圓放在測試平臺上,用探針探到芯片中事先確定的測試點,探針上可以通過直流電流和交流信號,可以對其進行各種電氣參數測試。chiptest和wafertest設備Z主要的區別是因為被測目標形狀大小不同因而夾具不同。

3、封裝測試(packagetest)

packagetest是在芯片封裝成成品之后進行的測試。由于芯片已經封裝,所以不再需要無塵室環境,測試要求的條件大大降低。通常包含測試各種電子或光學參數的傳感器,但通常不使用探針探入芯片內部(多數芯片封裝后也無法探入),而是直接從管腳連線進行測試。由于packagetest無法使用探針測試芯片內部,因此其測試范圍受到限制,有很多指標無法在這一環節進行測試。

二、不同芯片適用的測試

對于芯片面積大、良率高、封裝成本低的芯片,通常可以不進行wafertest,而芯片面積小、良率低、封裝成本高的芯片,Z好將很多測試放在wafertest環節,及早發現不良品,避免不良品混入封裝環節,無謂地增加封裝成本。

三、芯片測試的過程

芯片測試的過程是將封裝后的芯片置于各種環境下測試其電氣特性,如消耗功率、運行速度、耐壓度等。經測試后的芯片,依其電氣特性劃分為不同等級。而特殊測試則是根據客戶特殊需求的技術參數,從相近參數規格、品種中拿出部分芯片,做有針對性的專門測試,看是否能滿足客戶的特殊需求,以決定是否須為客戶設計專用芯片。經一般測試合格的產品貼上規格、型號及出廠日期等標識的標簽并加以包裝后即可出廠。而未通過測試的芯片則視其達到的參數情況定作降級品或廢品。

IC測試的設備,由于IC的生產量通常非常巨大,因此像萬用表、示波器一類手工測試儀器是一定不能勝任的,目前的測試設備通常都是全自動化、多功能組合測量裝置,并由程序控制,你基本上可以認為這些測試設備就是一臺測量專用工業機器人。

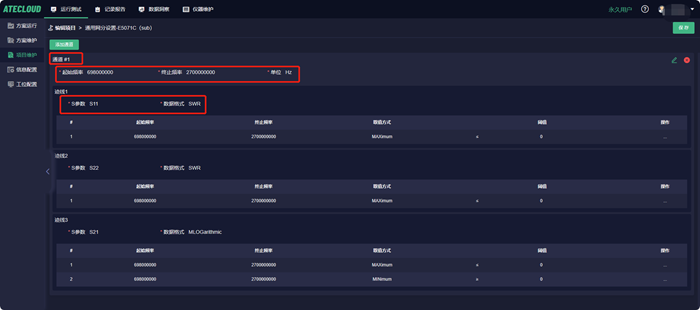

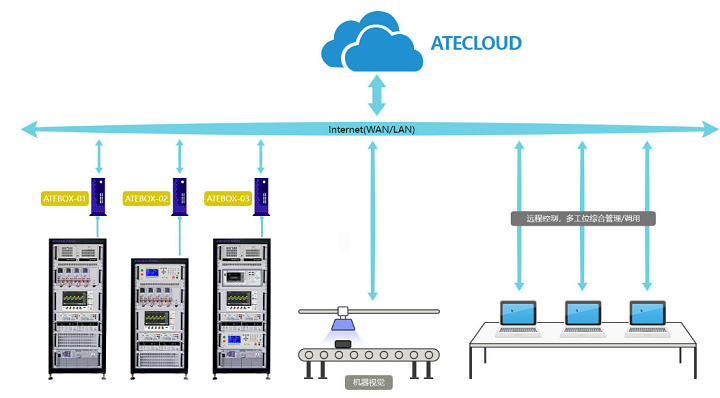

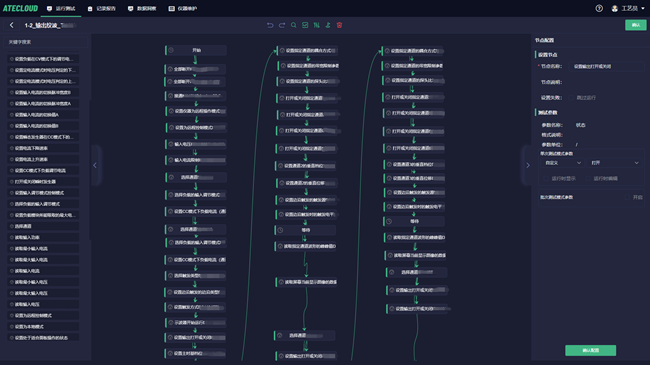

四、芯片自動化測試平臺

市面上芯片自動化測試系統五花八門,目前上市面上使用比較多的如ATECLOUD芯片自動測試平臺。使用ATECLOUD芯片自動測試系統整個過程只需1.5~2分鐘即可完成芯片諸多參數的測試,而采集數據與報告導出只需15秒即可完成,相比人工手動測試和記錄報告效率提升50-100倍,同時只需一個懂儀器操作的人員即可完成測試,極大節省了人力成本。

審核編輯黃宇

-

芯片

+關注

關注

459文章

52250瀏覽量

436814 -

自動化測試

+關注

關注

0文章

229瀏覽量

27235 -

IC

+關注

關注

36文章

6101瀏覽量

178516

發布評論請先 登錄

通用自動化測試軟件 - TAE

串口屏自動化測試

IC測試基本原理與ATE測試向量生成

全方位了解IC芯片測試流程,IC芯片自動化測試平臺分享

全方位了解IC芯片測試流程,IC芯片自動化測試平臺分享

評論