**1. Buck Layout注意事項

**

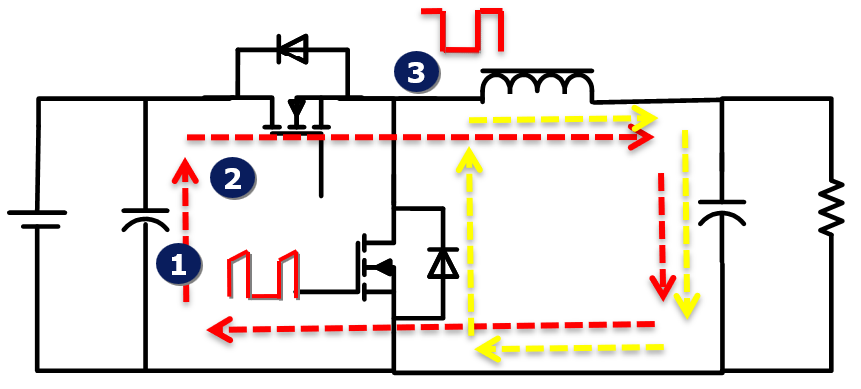

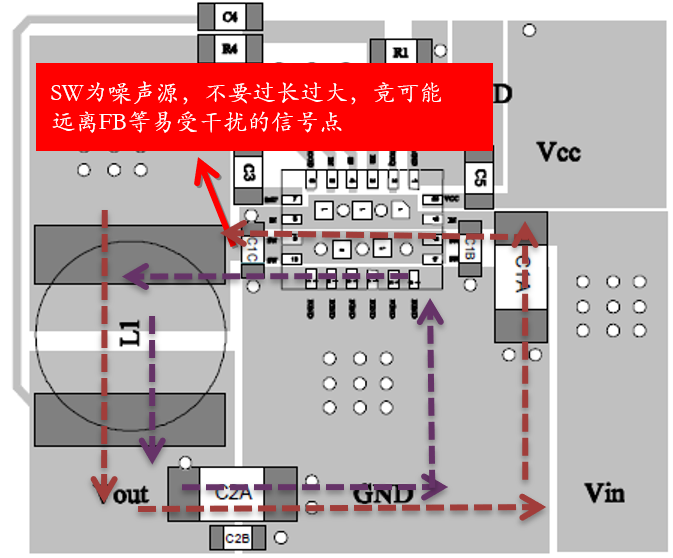

① 輸入電容就近放在芯片的輸入Vin和功率地PGND,減少寄生電感的存在,因為輸入電流不連續(xù),寄生電感引起的噪聲對芯片的耐壓以及邏輯單元造成不良影響;

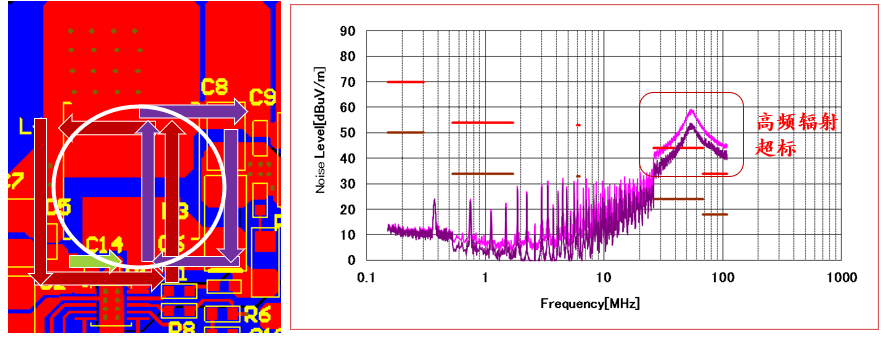

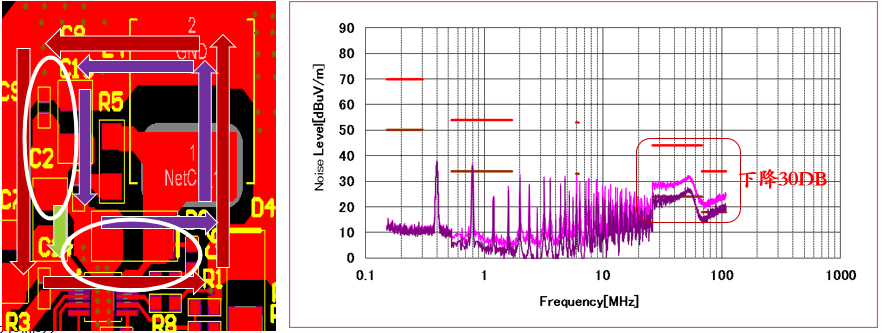

**② 功率回路盡可能的短粗,保持較小的環(huán)路面積,較少噪聲的發(fā)射;

**

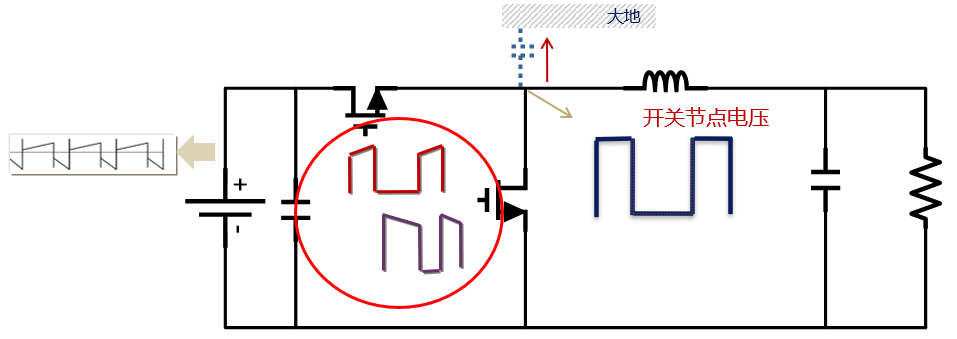

③ SW點是噪聲源,保證電流的同時保持盡量小的面積,遠(yuǎn)離敏感的易受干擾的位置;

④ VCC電容應(yīng)就近放置在芯片的VCC管腳和芯片的信號地之間,盡量在一層,沒有過孔對于信號地(AGND)和功率地PGND在一個管腳的芯片,同樣就近和該管腳連接;

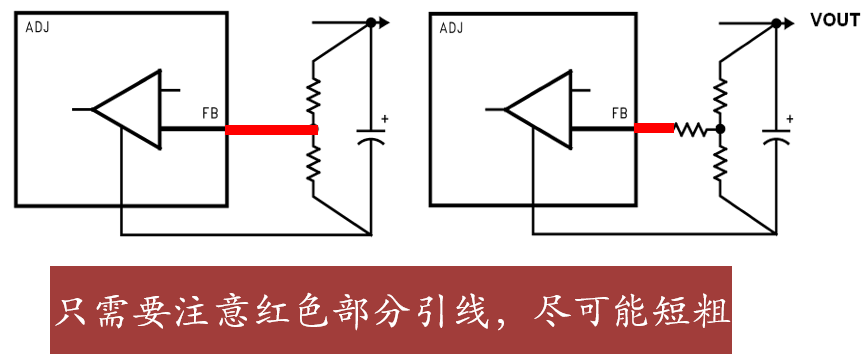

⑤ FB是芯片最敏感,最容易受干擾的部分,是引起系統(tǒng)不穩(wěn)定的最常見原因。

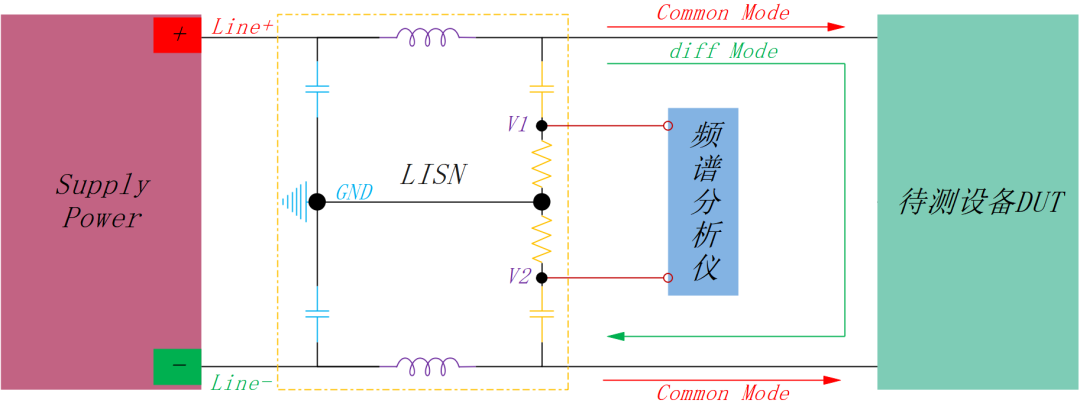

2. DCDC的噪聲來源

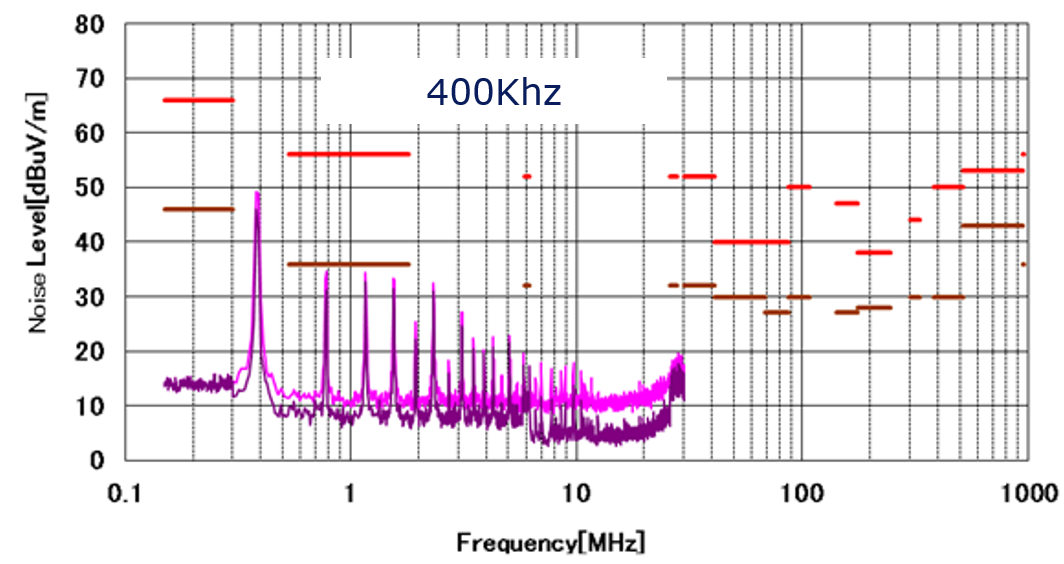

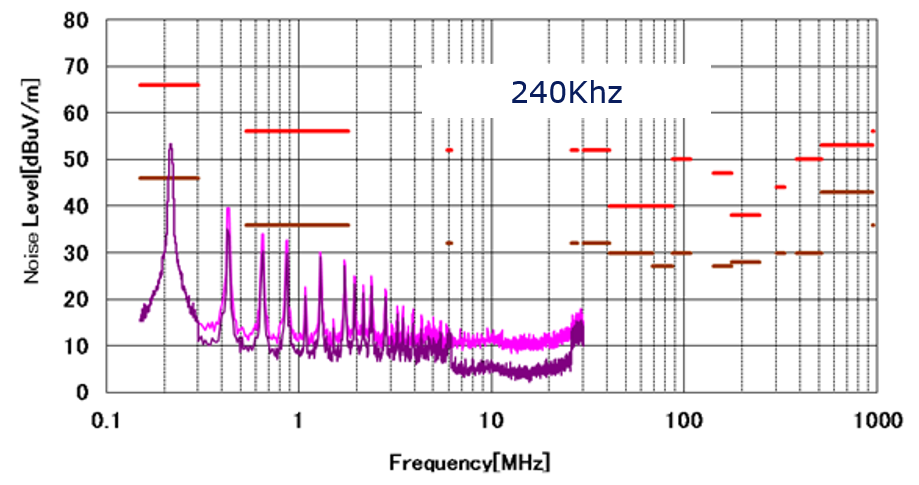

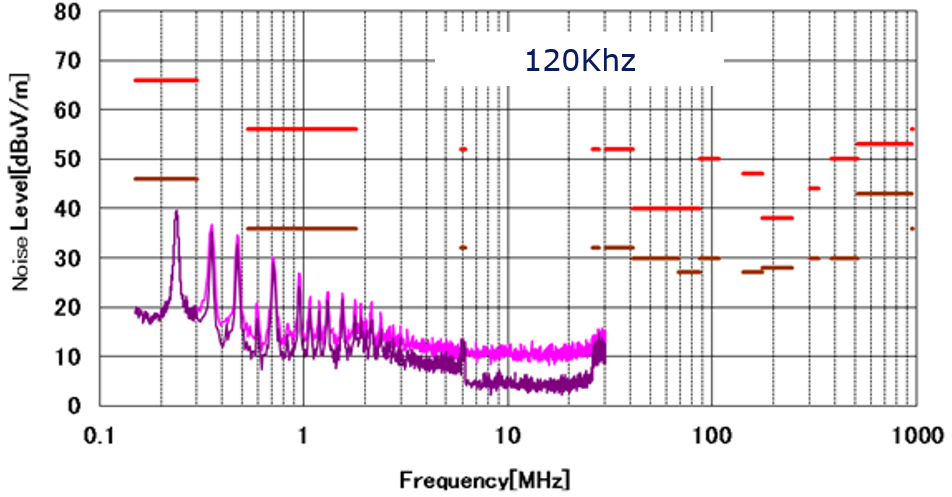

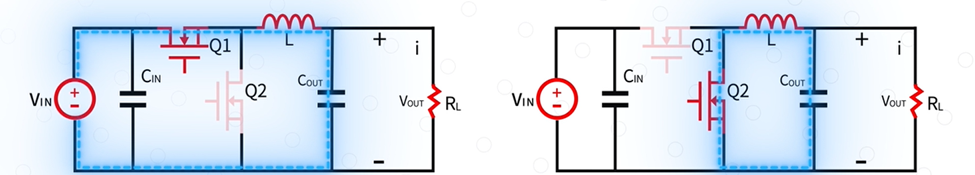

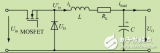

a. BUCK電路EMI的主要來源:高頻電流環(huán)路和電壓跳變

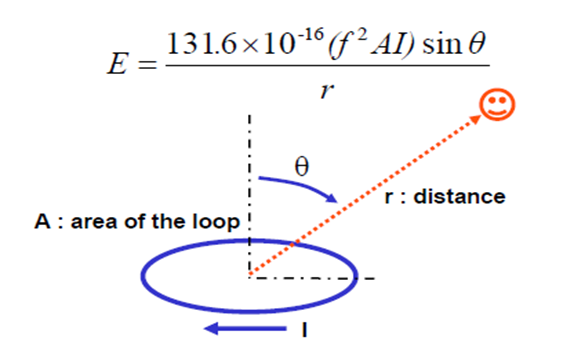

b. 環(huán)路天線原理:噪聲分量和電流大小,環(huán)路面積和頻率成正比,和距離成反比

3. DCDC的噪聲抑制辦法

a. 減慢開關(guān)速度,主要和上升時間Tr有關(guān);

b. 減小高頻環(huán)路面積,增加Vin和GND電容可以減少高頻環(huán)路的電流;

c. 減小開關(guān)節(jié)點面積,降低容性耦合。

-

芯片

+關(guān)注

關(guān)注

459文章

52253瀏覽量

437007 -

信號

+關(guān)注

關(guān)注

11文章

2844瀏覽量

77954 -

管腳

+關(guān)注

關(guān)注

1文章

230瀏覽量

32610 -

Vcc

+關(guān)注

關(guān)注

2文章

307瀏覽量

37321

發(fā)布評論請先 登錄

BUCK面臨的挑戰(zhàn):EMI問題及對應(yīng)的優(yōu)化方案

pcb layout必須要了解EMI的三要素

Buck電路中PCB layout布局設(shè)計和注意事項

DCDC BUCK通過加RC Snubber解決EMI輻射超標(biāo)的仿真和實測數(shù)據(jù)分析

如何從EMI角度看PCB layout 法規(guī)

【技術(shù)探討】BUCK電路設(shè)計技術(shù)要點

buck電路電感值如何選取

開源硬件-PMP11052.1-面向 Fly-buck 的 EMI 優(yōu)化布局設(shè)計 PCB layout 設(shè)計

SPS Layout學(xué)習(xí)筆記

buck電路是什么意思_buck電路簡介

如何在PCB的Layout階段,充分應(yīng)用改善技巧抑制EMI噪訊的強度

BUCK電路的EMI抑制方案

PMP30930.1-EMI 優(yōu)化型降壓 PCB layout 設(shè)計

Buck電路的Layout設(shè)計與EMI

Buck電路的Layout設(shè)計與EMI

評論