00 AMBA概述

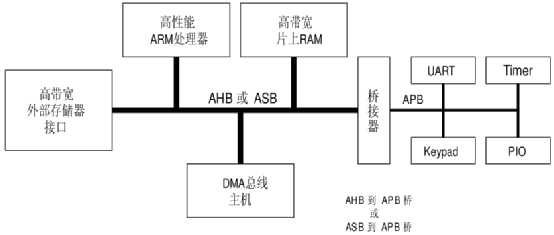

AMBA (Advanced Microcontroller Bus Architecture)高級微控制器總線架構定義了在設計高性能嵌入式微控制器的一種片上通信標準。主要包含以下四種:

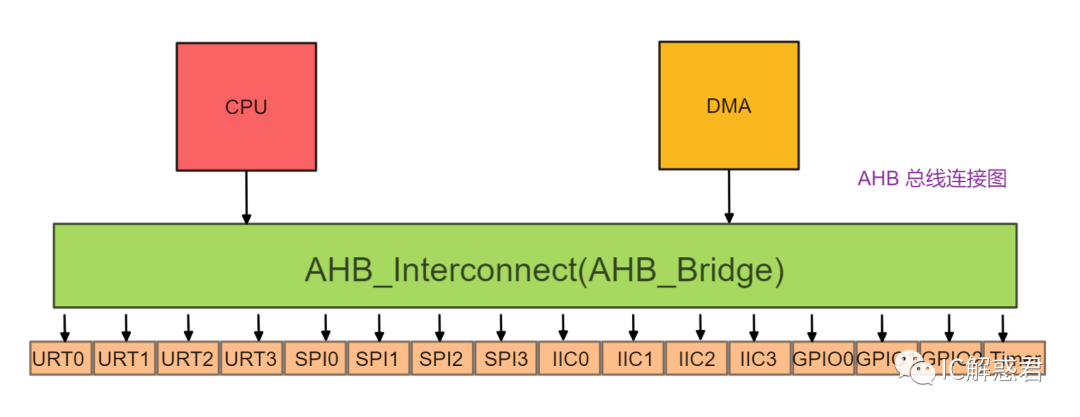

AHB (Advanced High-performance Bus) 高級高性能總線,用于高性能、高時鐘頻率的系統模塊

ASB (Advanced System Bus) 高級系統總線,用于高性能的系統模塊[現在使用較少]

APB (Advanced Peripheral Bus) 高級外圍總線,用于低功耗外設,可連接任一版本系統總線

AXI (Advanced eXtensible Interface) 高級可拓展接口,高速度、高帶寬,管道化互聯,單向通道,只需要首地址,讀寫并行,支持亂序,支持非對齊操作,有效支持初始延遲較高的外設,連線非常多。

***01 ***基本組成

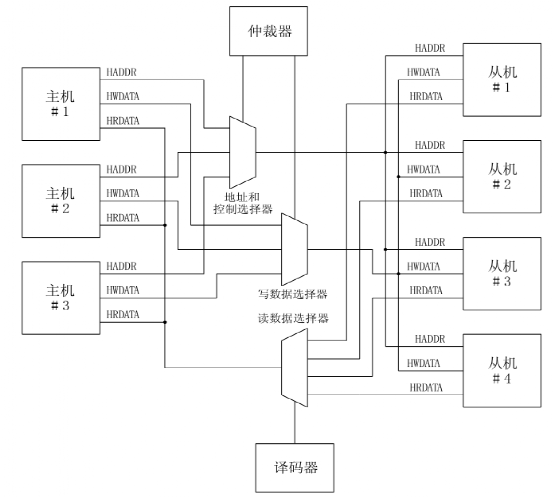

典型的AHB系統主要包含以下四部分:

AHB Master :總線主機能夠通過提供地址和控制信號進行讀寫操作,任何時候只允許一個主機處于有效狀態并使用總線。[發起端]

AHB Slave :總線從機在給定的地址空間響應讀寫操作,并將操作響應返回給有效的主機。[響應端]

AHB Arbiter :總線仲裁器確保每次只有一個總線主機被允許發起數據傳輸。

AHB Decoder : AHB譯碼器對每次傳輸的地址譯碼并在傳輸中包含一個從機選擇信號。

操作流程:

①Mater向Arbtier發送總線占用請求;

②獲得授權的Master進行總線傳輸

首先發出地址和控制信號:提供地址信息、傳輸方向等;

其次,譯碼器根據地址和控制信號選擇Slave,確定數據傳輸路徑;

最后進行數據傳輸。

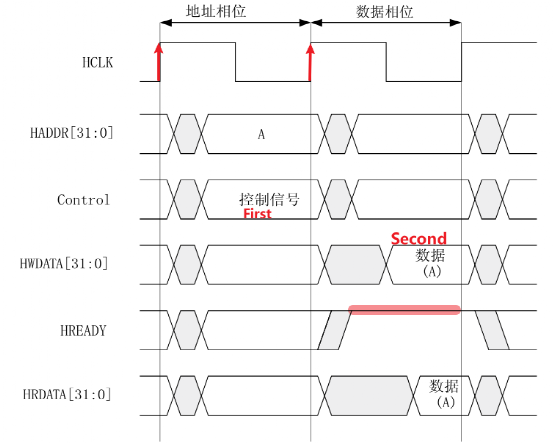

02 ** 基本傳輸**

AHB傳輸分為兩部分:地址周期和數據周期;先地址周期,再數據周期;地址周期單周期,數據周期可多周期。

1.簡單傳輸(無等待)

在第一個時鐘上升沿傳輸控制和地址信號,在第二個時鐘上升沿傳輸數據信號,同時HREADY信號為高表明數據傳輸完成。

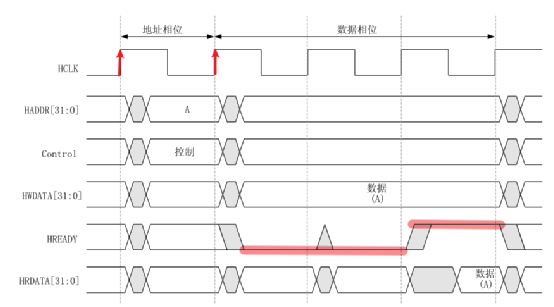

2.等待狀態的傳輸

首先是地址周期,在時鐘上升沿時傳輸地址信號和控制信號;

其次是數據周期,在下一個時鐘上升沿開始,如果HREADY信號為高則表明數據傳輸完成,HREADY信號為低則繼續傳輸。

注意:對于寫操作而言,數據在整個擴展周期要保持穩定;讀操作則無必要。

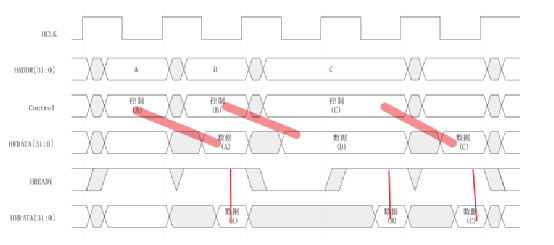

3.多重傳輸

多重傳輸采用流水線pipeline技術。

如圖,第一個周期傳輸A地址;第二個周期傳輸A數據和B地址,同時READY為高表明A傳輸完成;第三個周期傳輸B數據和C地址,由于READY信號為低,數據傳輸未完成,需要等待;第四個周期保持地址和控制信號,同時READY信號為高表明B傳輸完成;由于沒有其他操作,第五個周期僅進行C數據傳輸,同時READY信號為高表明數據傳輸完成。

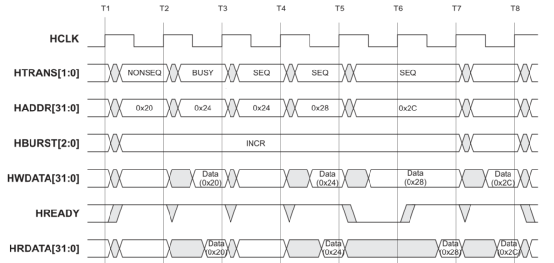

03 ** 傳輸類型HTRANS**

傳輸類型分四種:

空閑IDLE [00]:沒有數據傳輸要求

忙BUSY [01]:表明總線正被占用,下次傳輸不能立即發生

非連續NONSEQ [10]:表明一個單一傳輸或一次突發傳輸的第一個傳輸

連續SEQ [11]:突發中的剩下傳輸且地址與前一次傳輸有關

第一個傳輸是一次突發傳輸的開始,為NONSEQ類型;

由于主機不能立刻執行第二次傳輸,因此未BUSY類型來延時下一次傳輸開始;

04 ** 突發類型HBURST**

突發類型分八種:

SINGLE單一傳輸、INCR未指定長度的增量突發、

INCR4、INCR8、INCR16 分別是4拍、8拍和16拍的增量突發

WRAP4、WRAP8、WRAP16 分別是4拍、8拍和16拍的回環突發

注意:突發禁止超過1KB的地址邊界

1KB邊界限制在AHB中表示burst傳輸不能跨越1KB邊界的約束。該限制旨在防止burst傳輸從一個slave交叉到另一個slave。在實踐中,這意味著如果master必須要進行跨1KB邊界的burst傳輸則必須切分成兩次傳輸

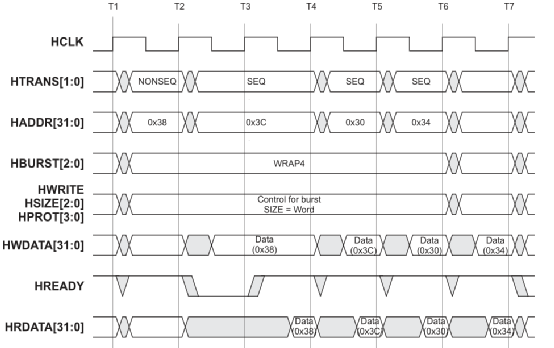

- WRAP4

起始地址為0x38, HSIZE=WORD[4byte], 突發類型是4拍回環突發,回環邊界地址=回環拍數*SIZE=4*4byte=16byte = 0x10。

由于起始地址不是16的整倍數,因此會產生折回,0x3C的下一個地址按增量為0x40,是16的整數倍,因此需要減去16,即為0x30。

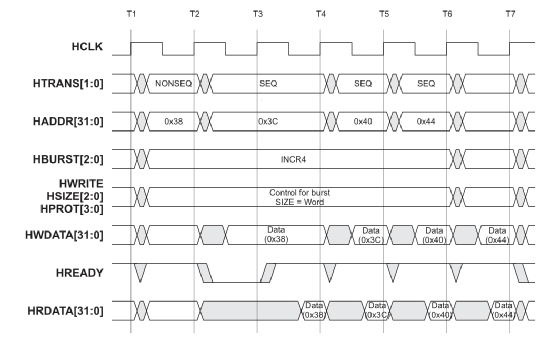

2.INCR4

起始地址為0x38, HSIZE=WORD[4byte],突發類型為4拍增量突發。

地址順序為0x38 0x3C 0x40 0x44[4次]

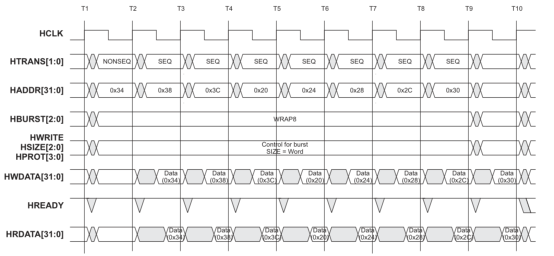

3.WRAP8

起始地址0x34, SIZE=WORD=4byte, 突發類型為WRAP8,

回環邊界地址=回環拍數*SIZE=8*4=32byte=0x20,當遇到回環邊界地址的整數倍時減去回環邊界地址。

地址順序0x34、0x38、0x3C、0x20、0x24、0x28、0x2C、0x30。

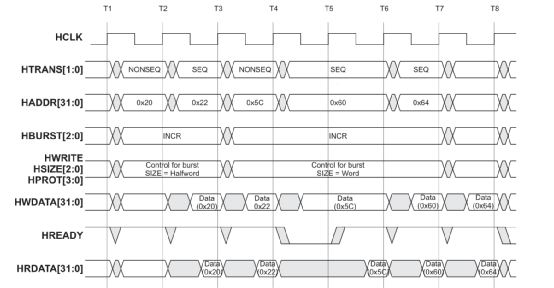

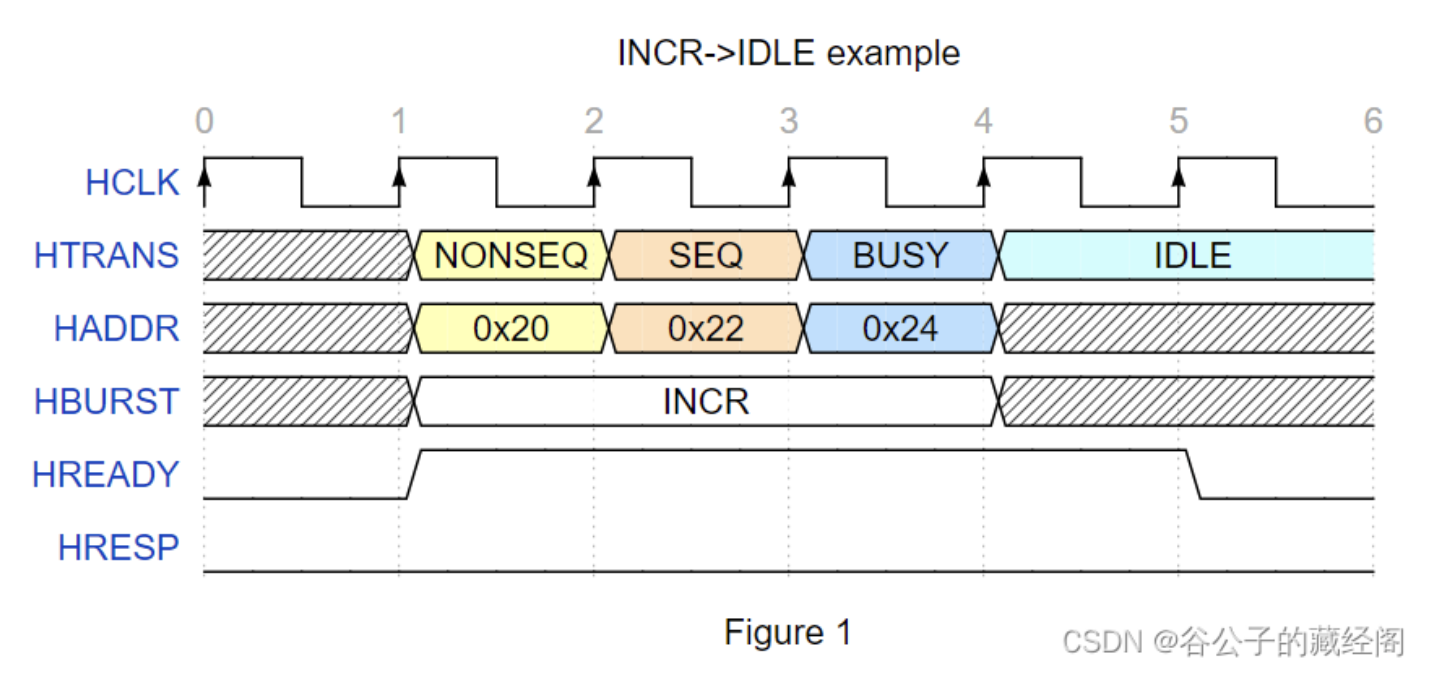

4.INCR

對于T1-T3周期,突發類型為INCR, SIZE=halfword=2byte,因此地址依次為0x20、0x22;

對于T3-T8周期,突發類型為INCR, SIZE=WORD=4Byte, 起始地址為0x5C,因此地址依次為0x5C、0x60、0x64。

05 ** 控制信號**

傳輸方向HWRITE

HWRITE=H表明寫操作,傳輸方向為MasteràSlave;

HWRITE=L表明讀操作,傳輸方向為SlaveàMaster;

傳輸大小HSIZE[2:0]

8bit(byte) 、16bit(halfword)、32bit(word)、64bit(2word)、128bit(4word)、256bit(8word)、512bit、1024bit

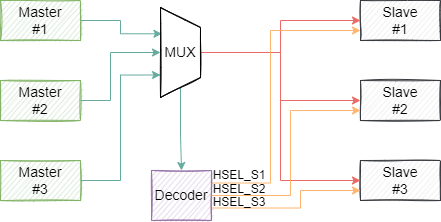

06 地址譯碼

主機發送地址信息給地址和控制多路選擇器,選擇器將地址信息發送給所有從機,同時將地址信息發送給譯碼器,譯碼器根據地址信息將相應設備的HSEL信號置高。

如果地址不存在則從機提供ERROR響應。

07 ** 從機傳輸響應**

傳輸完成HREADY

HREADY=1表明傳輸完成;

HREADY=0表明傳輸將被擴展,繼續傳輸。

傳輸響應HRESP

00 OKAY 傳輸成功完成

01 ERROR 傳輸發生錯誤

10 RETRY 重試

11 SPLIT 傳輸未完成

僅有OKAY信號是單周期給出,其他響應信號至少兩個周期。

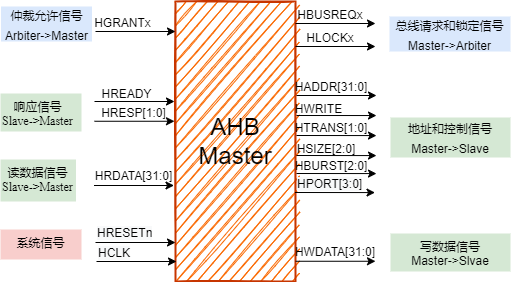

08 ** 接口框圖**

主機接口框圖

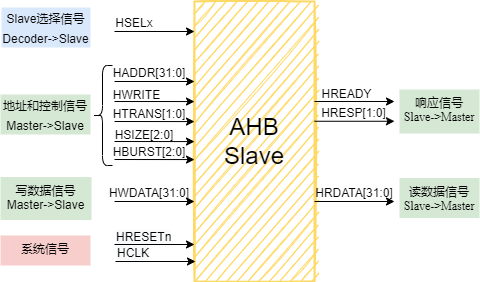

從機接口框圖

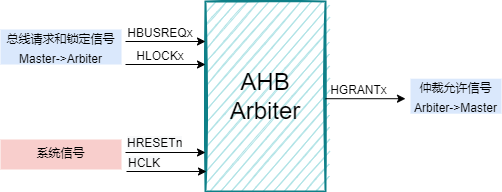

仲裁器接口框圖

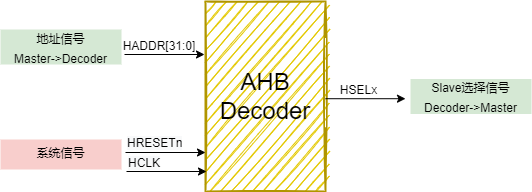

譯碼器接口框圖

-

AMBA

+關注

關注

0文章

70瀏覽量

15353 -

AHB

+關注

關注

0文章

26瀏覽量

10144 -

嵌入式微控制器

+關注

關注

1文章

12瀏覽量

2733

發布評論請先 登錄

ARM總線協議AMBA中AHB、APB的區別與聯系

AMBA、APB、AHB簡介

AMBA AHB總線與APB總線資料合集

AMBA中的AHB總線協議詳解

Arm AMBA協議集中AHB與AXI相比訪問DDR效率帶寬會差很大

Arm AMBA協議集中ahb2.0和3.0必須要有dummy master和default slave嗎?

請問一下Arm AMBA協議集中,axi burst 和ahb burst的區別是什么?

AMBA CHI協議介紹

數字IC驗證:ARM總線協議AMBA中AHB、APB的簡介、區別與聯系

AMBA AHB協議的burst termination簡析

AMBA協議之AHB介紹

AMBA協議之AHB介紹

評論