UltraRAM 原語(也稱為 URAM)可在 Xilinx UltraScale + 架構中使用,而且可用來高效地實現大容量深存儲器。由于大小和性能方面的要求,通常這類存儲器不適合使用其他存儲器資源來實現。URAM 原語具有實現高速內存訪問所需的可配置流水線屬性和專用級聯連接。流水線階段和級聯連接是使用原語上的屬性來配置的。

本篇博文描述的是通過將 URAM 矩陣配置為使用流水線寄存器來實現最佳時序性能的方法。

流水線需求

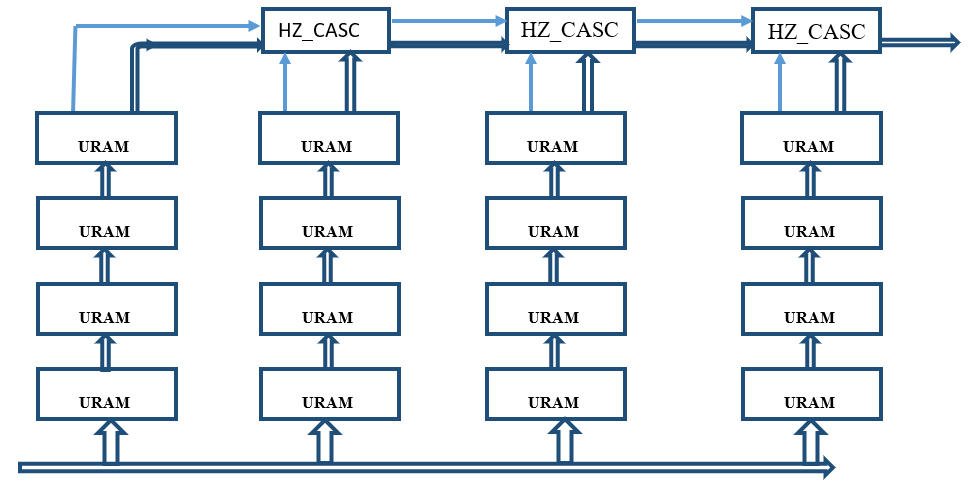

通過在矩陣結構中連接多個 URAM,從可用的 URAM 原語實現大容量深存儲器。

矩陣由 URAM 的行和列組成。一列中的 URAM 使用內置級聯電路級聯,且多列 URAM 通過外部級聯電路互連,這被稱為水平級聯電路。

作為示例,圖 1 示出了針對 64K 深 x 72 位寬存儲器的 4x4 URAM 矩陣的矩陣分解。

4 行 4 列的 URAM 矩陣(可實現 64K 深 72 位寬的存儲器)

在沒有流水線設計的情況下,深度聯結構會導致內存訪問出現大的時鐘輸出延遲。例如,在默認情況下,上述 URAM 矩陣可以達到約 350 MHz。要以更快的速度訪問內存,應插入流水線。如果在網表中指定了一定數量的輸出時延,Vivado Synthesis 即會自動實現此功能。

指定RTL設計中的流水線

有兩種方法可以用來指定 RTL 設計中的流水線的用途,可以通過使用 XPM 流程,也可以通過行為 RTL 來推斷內存。

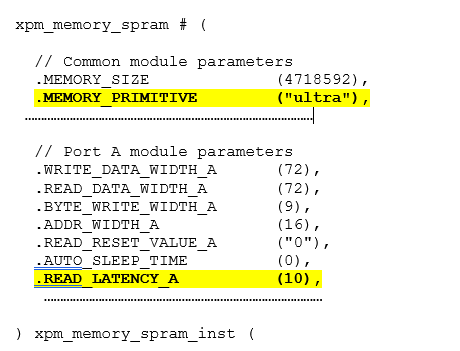

如果 RTL 設計通過 XPM 流程來創建 URAM 內存,則用戶可以將對流水線的要求指定為 XPM 實例的參數。參數“READ_LATENCY_A/B”用于捕獲內存的時延要求。

可用的流水線階段數是 LATENCY 值減去 2。例如,如果 Latency 設置為 10,則允許 8 個寄存器階段用于流水線操作。另外兩個寄存器可用來創建 URAM 本身。

使用 XPM 設置流水線設計

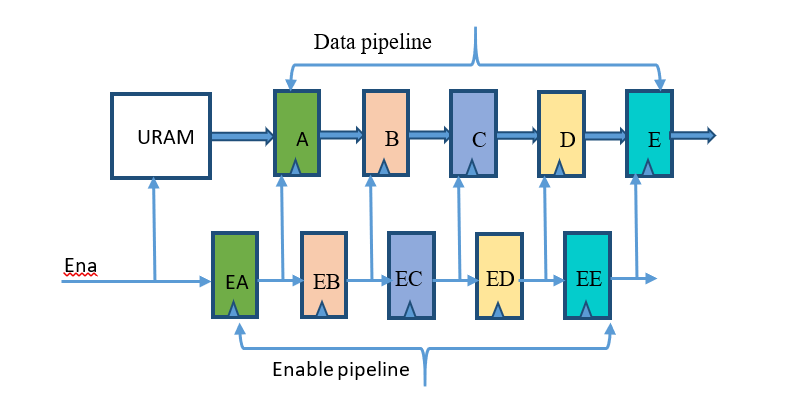

如果用戶使用 Vivado 用戶指南中提供的模板來編寫 RTL,并通過此方法來創建 URAM,那么,他們可以在 URAM 的輸出時創建盡可能多的寄存器階段。唯一的要求是,與數據一起,流水線寄存器的啟用也需要流水線化。

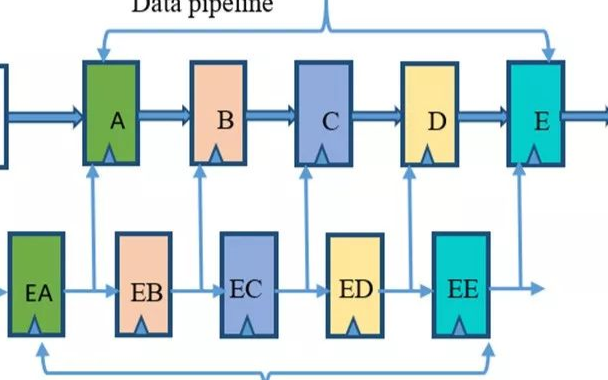

圖 3 顯示數據和流水線的啟用。

URAM 塊輸出時的數據及流水線啟用規范

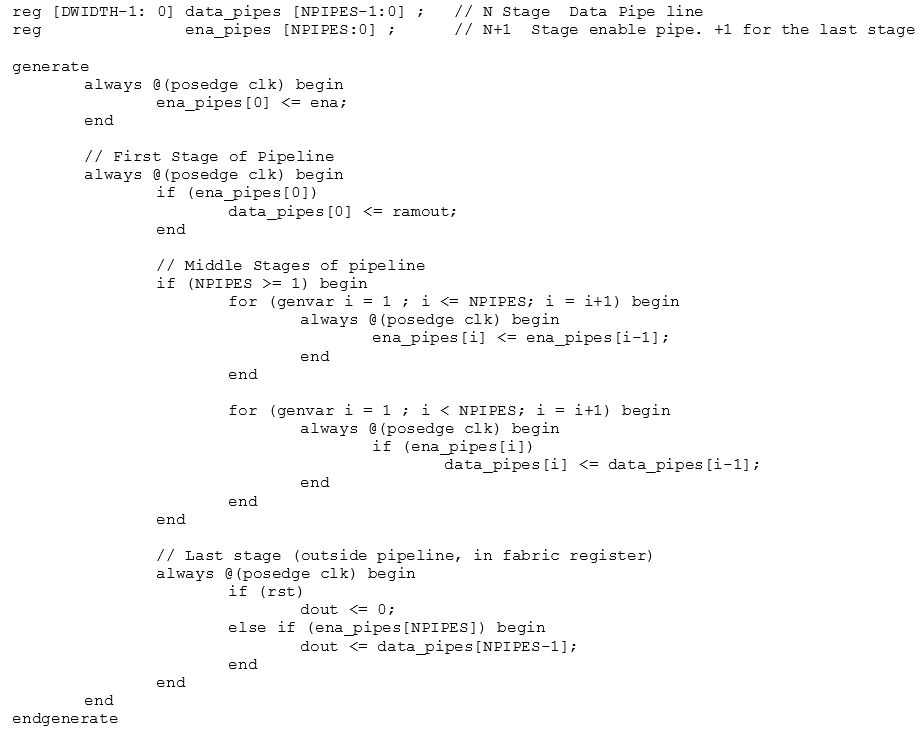

圖 4 示出了 RTL 級 RAM 流水線設計示例。

用來指定數據和流水線啟用的 verilog 模板

分析日志文件:

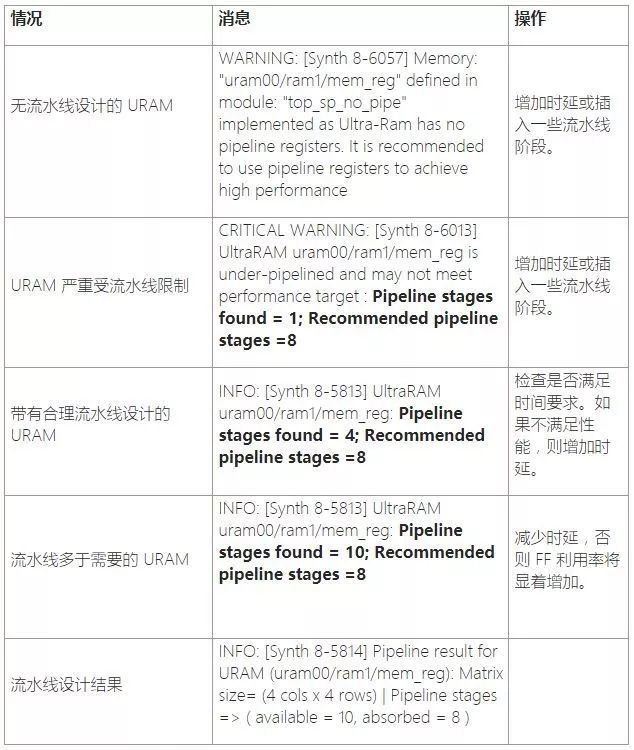

Vivado Synthesis 根據上下文環境和場景發布與 URAM 流水線相關的不同消息。下表說明要在 vivado.log 文件中查找的一些消息和要采取的相應操作。

請注意,推薦的流水線階段基于可實現最高性能(800 MHz+)的完全流水線化的矩陣。此建議不受實際時序約束的限制。

時間性能估計:

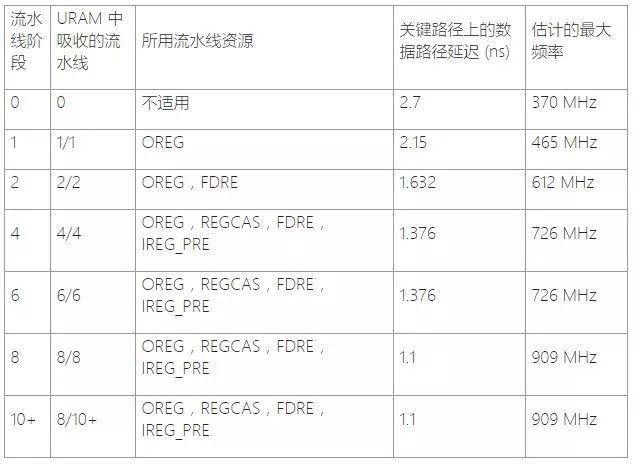

下表說明流水線寄存器的數量與可實現的最大估計頻率之間的關系。

請注意,實際的時間數仍將取決于最終地點和路線結果。

下列數字基于 speedgrade-2 Virtex UltraScale+ 部件以及我們使用 4x4 矩陣實現的 64K x 72 URAM 示例工程。

數據路徑延遲具有以下一個或多個組件。

Tco = 1.38 ns, Clk To CascadeOut on URAM

Tco = 0.82 ns, Clk To CascadeOut on URAM with OREG=true

Tco = 0.726 ns, Clk to Dataout on URAM with OREG=true, CASCADE_ORDER = LAST

URAM -> URAM級聯延遲= 0.2 ns

URAM -> LUT信號網絡延遲= 0.3 ns

LUT傳輸延遲= 0.125 ns

LUT -> LUT信號網絡延遲= 0.2 ns

LUT5 -> FF延遲= 0.05

結 論

URAM 原語是創建容量非常大的 RAM 結構的有效方法。它們被設置為易于級聯以便在您的設計中創建容量更大的 RAM。

但是,太多這類結構級聯在一起可能會通過 RAM 產生很大的延遲。從長遠來看,花時間讓您的 RAM 完全流水線化會帶來很多好處。

URAM 原語是創建容量非常大的 RAM 結構的有效方法。它們被設置為易于級聯以便在您的設計中創建容量更大的 RAM。

但是,太多這類結構級聯在一起可能會通過 RAM 產生很大的延遲。從長遠來看,花時間讓您的 RAM 完全流水線化會帶來很多好處。

審核編輯:湯梓紅

-

存儲器

+關注

關注

38文章

7637瀏覽量

166529 -

Xilinx

+關注

關注

73文章

2183瀏覽量

124464 -

流水線

+關注

關注

0文章

124瀏覽量

26514 -

RTL

+關注

關注

1文章

388瀏覽量

60729 -

Vivado

+關注

關注

19文章

831瀏覽量

68308

原文標題:干貨 | 如何通過 Vivado Synthesis 中的 URAM 矩陣自動流水線化來實現最佳時序性能

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

自動化流水線電子看板系統

FPGA中的流水線設計

ARM架構系列中的流水線設計

現代RISC中的流水線技術

嵌入式_流水線

MT6701磁編碼IC在自動化插件流水線中的應用

工業讀碼器解決方案在自動化流水線上掃描條碼的應用

如何通過Vivado Synthesis中的URAM矩陣自動流水線化來實現最佳時序性能

如何通過Vivado Synthesis中的URAM矩陣自動流水線化來實現最佳時序性能

評論