大俠好,歡迎來到FPGA技術江湖。本系列將帶來FPGA的系統性學習,從最基本的數字電路基礎開始,最詳細操作步驟,最直白的言語描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業學生、初入職場小白及打算進階提升的職業開發者都可以有系統性學習的機會。

系統性的掌握技術開發以及相關要求,對個人就業以及職業發展都有著潛在的幫助,希望對大家有所幫助。后續會陸續更新 Xilinx 的 Vivado、ISE 及相關操作軟件的開發的相關內容,學習FPGA設計方法及設計思想的同時,實操結合各類操作軟件,會讓你在技術學習道路上無比的順暢,告別技術學習小BUG卡破腦殼,告別目前忽悠性的培訓誘導,真正的去學習去實戰應用,這種快樂試試你就會懂的。話不多說,上貨。

數字電路中的時序邏輯

在各種復雜的數字電路中,不但需要對二值信號進行算數運算和邏輯運算,還經常需要將這些信號和運算結果保存起來。為此,需要使用具有記憶功能的基本邏輯單元。能夠存儲1位的二進制數碼的單元電路稱為觸發器。

為了實現記憶1位二值信號的功能,觸發器必須具備以下兩個基本特點:

具有兩個能自行保持的穩定狀態,用來表示邏輯狀態的0和1,或二進制數的0和1。

在觸發信號的操作下,根據不同的輸入信號可以置成1或0狀態

由于采用的電路結構形式不同,觸發信號的觸發方式也不一樣。觸發方式分為電平觸發、脈沖觸發、邊沿觸發三種。

SR鎖存器是各種觸發器電路的基本構成部分。

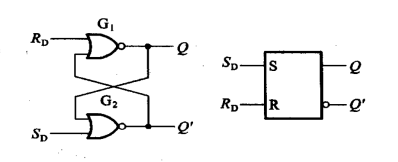

圖1 :SR鎖存器(或非門)的電路結構和圖像符號

從電路結構中可以看出,它是由兩個交叉反饋或非門組成的。它有兩個輸入端,SD表示置位,RD表示復位,輸入端為1時表示有激勵信號,為0時表示無激勵信號;有兩個輸出端,Q是輸出,正常工作時,Q’是Q的反變量。

思考:分析SR鎖存器(或非門構成)的工作原理?

當RD =0,SD=1時,不論觸發器的初始狀態如何,Q’一定為0,由于“與非”門G1的輸入全是0,Q端為1。稱觸發器為1狀態,SD為置1端。

當RD =1,SD=0時,不論觸發器的初始狀態如何,Q’一定為1,從而使Q為0。稱觸發器為0狀態,RD置0端。

當RD =0,SD =0時,如前所述,Q及Q’狀態保持原狀態不變。

當RD =1,SD =1時,不論觸發器的初始狀態如何,Q=Q’=0,若RD、SD同時由1變成0,在兩個門的性能完全一致的情況下, Q及Q’哪一個為1,哪一個為0是不定的,在應用時不允許RD和SD同時為1。

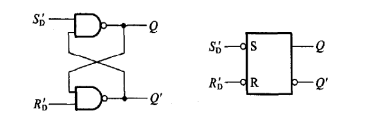

SR鎖存器也可以用與非門構成。

圖2 :SR鎖存器(與非門)的電路結構和圖像符號

與非門構成的SR鎖存器的工作原理和或非門構成的SR鎖存器類似,具體不在敘述。

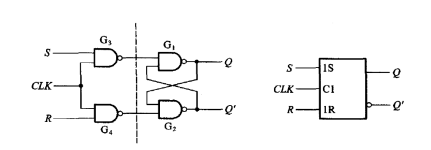

在電平觸發的觸發器電路中,除了置1、置0輸入端以外,又增加了一個觸發信號輸入端。只有觸發信號變為有效電平后,觸發器才能按照輸入的置1、置0信號置成相應的狀態。將觸發信號記作CLK。

圖3 :電平觸發的SR觸發器的電路結構和圖形符號

思考:電平觸發的SR觸發器的工作原理?

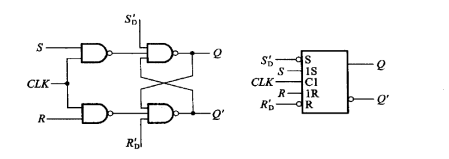

在某些應用場合,有時需要在CLK的有效電平到達之前預先將觸發器置成指定狀態,為此,在實用的電路上往往設置有異步置1輸入端SD‘和異步置0輸入端RD’。

圖4:帶有異步置位、復位端的電平觸發的SR觸發器的電路結構和圖形符號

思考 :帶有異步置位、復位端的電平觸發的SR觸發器的工作原理?

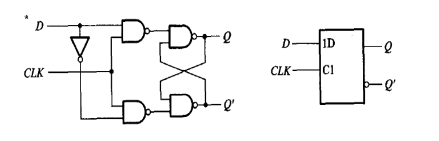

為了能適應單端輸入信號的需要,在一些集成電路產品中,將電平觸發的SR觸發器經過修改,得到了電平觸發的D觸發器,也稱D型鎖存器。

圖5:電平觸發的D觸發器的電路結構和圖形符號

思考 :電平觸發的D觸發器的工作原理。

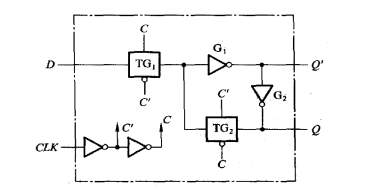

在CMOS電路中,經常利用CMOS傳輸門組成電平觸發D觸發器,如圖6。

圖6 :利用CMOS傳輸門組成的電平觸發的D觸發器

在CLK的有效電平期間輸出狀態始終跟隨輸入狀態變化,輸出與輸入的狀態保持相同,所以又將這個電路稱為“透明的D型鎖存器”。

為了提高觸發器工作的可靠性,希望在每個CLK周期里輸出端的狀態只能改變一次。因此,在電平觸發的觸發器的基礎上,設計了脈沖觸發的觸發器。

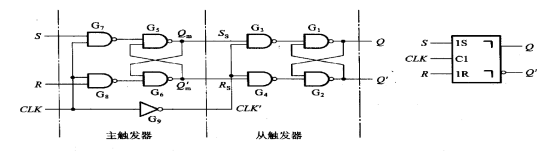

圖7 :主從SR觸發器的電路結構和圖形符號

思考 :主從SR觸發器的工作原理?

在使用主從結構觸發器時經常會遇到這樣的一個情況,就是在CLK=1期間輸入信號發生過變化以后,CLK下降沿到達時從觸發器的狀態不一定能按照此刻輸入信號的狀態來確定,而必須考慮整個CLK=1期間輸入信號的變化過程才能確定觸發器的次態。

例:在CLK=1時,首先將S=1;R=0;此時主觸發器置1。然后S=0,R=0,此時主觸發器依然是置1的。當CLK=0時,從觸發器就會按照置1的方式去驅動,而不是S=0,R=0的情況。

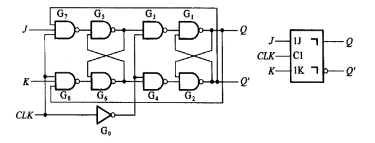

為了使用方便,希望即使出現了S=R=1的情況,觸發器的次態也是確定,因而需要進一步改進觸發器的電路結構。因此設計了主從結構JK觸發器。

圖8 :主從結構JK觸發器的電路結構和圖形符號

思考 :主從結構JK觸發器的工作原理?

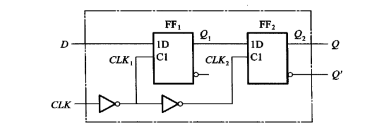

為了提高觸發器的可靠性,增強抗干擾能力,希望觸發器的次態僅僅取決于CLK信號下降沿(或上升沿)到達時刻輸入信號的狀態。而在此之前和之后輸入狀態的變化對觸發器的次態沒有影響。為實現這一設想,設計了用兩個電平觸發的D觸發器組成的邊沿觸發器。

圖9 :用兩個電平觸發的D觸發器組成的邊沿觸發器

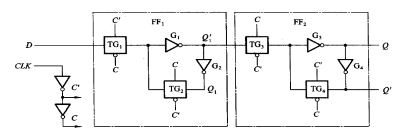

圖10 :CMOS邊沿觸發D觸發器

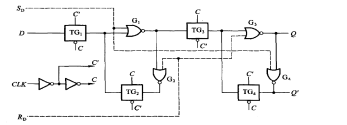

圖11 :帶有異步置位、復位端的CMOS邊沿觸發D觸發器

思考:分析邊沿觸發的D觸發器的工作原理?

為了保證觸發器在工作時能可靠地翻轉,對于輸入信號、時鐘信號以及它們互相配合關系的都有一定的要求。

輸入信號的寬度有一定的要求;各個單元電路都有一定的延遲,輸入信號給定后,輸出信號會延遲一段時間才會出現;輸入信號要求在CLK有效沿到來之前的一段時間內穩定,這段時間稱為建立時間;輸入信號要求在CLK有效沿過去之后的一段時間內穩定,這段時間稱為保持時間;CLK的變化頻率會有一定的上限。對于每個具體型號的集成觸發器,可以從手冊上查到這些動態參數,在工作時應符合這些參數所規定的條件。

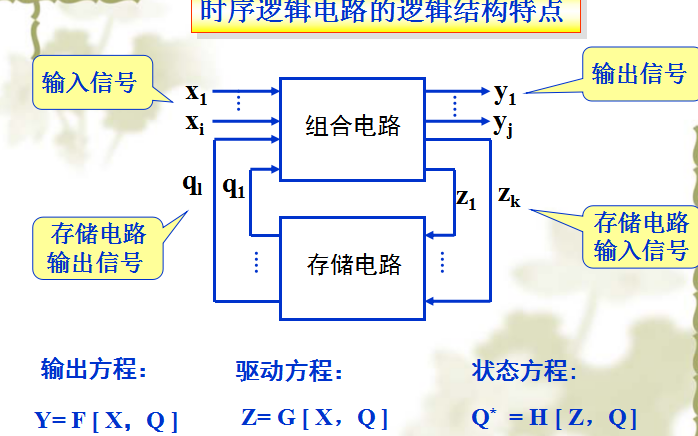

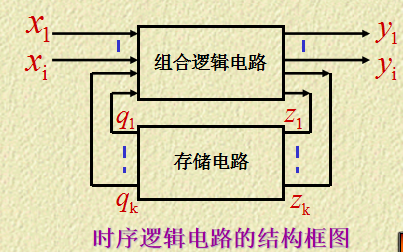

組合邏輯電路中,任一時刻的輸出信號僅取決于當時的輸入信號。時序邏輯電路(簡稱為時序電路)中,任一時刻的輸出信號不僅取決于當時的輸入信號,而且還取決于電路原來的狀態,或者說,還與以前的輸入有關。

例如:目前需設計一個自動售貨機,販賣售價為三元的飲料,要求每次只能投入一個一元的硬幣。可想而知,我們投入第一個硬幣沒有反應;投入第二個硬幣沒有反應;當我們投入第三個硬幣時,售貨機會給我們一瓶飲料。如果內部是組合邏輯的話,三次投硬幣的輸入并沒有任何改變,但是產生了不同的結果,顯然內部結構不是單純的組合邏輯。內部的功能有一定的記憶性功能,能夠清楚的記得之前我們投入的硬幣的數量。

時序邏輯電路 = 組合邏輯電路 + 時序邏輯器件(觸發器)。

根據輸出信號的特點將時序電路劃分為米利型(Mealy)和穆爾型(Moore)兩種。在米利型電路中,輸出信號不僅取決于存儲電路的狀態,而且還取決于輸入變量;在穆爾型電路中,輸出信號僅僅取決于存儲電路的狀態。穆爾型電路只不過是米利型電路的一種特例而已。

鑒于時序電路在工作時是在電路的有限狀態間按一定的規律轉換的,所以又將時序電路稱為狀態機(state machine SM)或算法狀態機(algorithmic state machine ASM)。

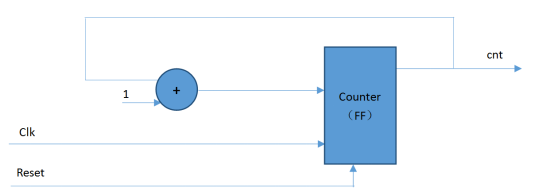

計數器的時序電路如下:

圖12 :計數器(自加一)電路結構

思考 :分析計數器(自加一)工作原理?

寄存器(Register)用于寄存一組二值代碼,它被廣泛地用于各類數字系統和數字計算機中。一個觸發器能儲存1位二值數碼,用N個觸發器組成的寄存器能夠儲存一組N位的二值數碼。

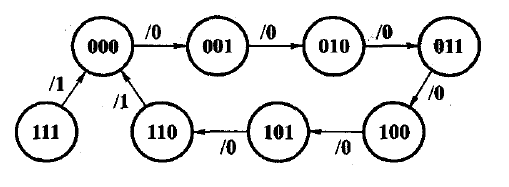

狀態轉換圖:在狀態轉換圖中以圓圈表示電路的各個狀態,以箭頭表示狀態的轉換方向。在箭頭的旁邊注明了狀態轉換前的輸入變量取值和輸出值。通常將輸入變量取值寫在斜線以上,將輸出值寫在斜線以下。當沒有輸入變量時,斜線上方不寫任何東西。

圖13 :狀態轉移圖(示例)

簡單時序邏輯電路的設計方法如下:

邏輯抽象,得出電路的狀態轉換圖或狀態轉換表。

狀態化簡

若兩個電路狀態在相同的輸入下有相同的輸出,并且轉換到同樣一個狀態去,則稱這兩個狀態為等價狀態。顯然,等價狀態是重復的,可以合并為一個。電路的狀態數越少,設計出來的電路就越簡單。狀態化簡的目的就在于將等價狀態合并,以求得最簡的狀態轉移圖。

狀態分配

狀態分配又稱狀態編碼。時序邏輯電路的狀態是用觸發器狀態的不同組合來表示的。首先,需要確定觸發器的數目n。因為n個觸發器共有2的n次冪種狀態,要保證觸發器能表示的狀態數要大于等于設計需要的狀態數。

選定觸發器的類型,求出電路的狀態方程、驅動方程和輸出方程

根據得到的方程式畫出邏輯圖

檢查設計的電路能夠自啟動

在設計復雜的時序電路時,通常采用層次化結構設計方法,或者稱為模塊化設計方法。層次化結構設計方法有“自頂向下”(top - to - down)和“自底向上”(bottom - to - up )兩種做法。采用自頂向下的做法時,首先需要將所設計電路的功能逐級劃分為更簡單的功能模塊,直到這些模塊都能用簡單的邏輯電路實現為止。由于自頂向下劃分模塊的過程中完全從獲得最佳電路性能觸發的,并未考慮這些模塊電路是否已經有成熟的設計存在了,所以必須從頭設計每個模塊電路,然后進行仿真和測試。在發現問題時,還需要反復修改。

在采取自底向上的做法時,首先要考慮有哪些已有的,成熟的模塊電路可以利用。這些模塊電路可能是標準化的集成電路器件,也可能是經過驗證的電路單元。將電路劃分為功能塊時,最后要劃分到能利用這些已有的模塊電路來實現為止。直接采用這些模塊電路能大大減少設計的工作量。然而有時由于需要遷就已有的模塊電路,這就會使電路的某些性能收到一些影響。另外,也不可能任何一種功能模塊都有現成的成熟設計,因此多數情況下都采用自頂向下和自底向上相結合的方法,以求達到既能滿足設計要求,又能提高設計速度、降低設計成本的目標。

時序邏輯電路通常包含組合邏輯電路和存儲電路(觸發器)兩個組成部分。所以它的競爭-冒險現象也包含兩個方面。

組合邏輯電路可能發生競爭-冒險現象。產生原因和方法已經在1.4組合邏輯中敘述過,不在過多敘述。

觸發器在工作工程中也有可能發生競爭-冒險現象。為了保證觸發器可靠地翻轉,輸入信號和時鐘信號在時間配合上應滿足一定的要求。然而當輸入信號和時鐘信號同時改變,而且途徑不同路徑到達同一觸發器時,便產生了競爭。競爭的結果有可能導致觸發器誤動作,這種現象稱為存儲電路(觸發器)的競爭-冒險現象。

在大多數的時序邏輯電路中,我們都可以分解成為一個帶有“變化”數據功能的組合邏輯和一個帶有“存儲”數據功能的觸發器。在組合邏輯如何避免競爭冒險時,我們給出一種解決方案:引入選通脈沖。也就是在數據穩定后,選通脈沖再過來。那么現在,如果組合邏輯后續電路是經過觸發器存儲的,那么可以直接把選通脈沖當作觸發器的CLK。只要能夠確定CLK是在數字穩定后有效的,那么對于時序邏輯電路就沒有競爭冒險。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1643文章

21973瀏覽量

614328 -

Xilinx

+關注

關注

73文章

2182瀏覽量

124391 -

數字電路

+關注

關注

193文章

1637瀏覽量

81610 -

觸發器

+關注

關注

14文章

2032瀏覽量

61892 -

時序邏輯

+關注

關注

0文章

39瀏覽量

9341

原文標題:【教程分享】FPGA零基礎學習:數字電路中的時序邏輯

文章出處:【微信號:gh_9b9470648b3c,微信公眾號:電子發燒友論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

新編數字電路與數字邏輯

FPGA零基礎學習:數字電路中的邏輯代數基礎

FPGA零基礎學習:數字電路中的組合邏輯

在FPGA中何時用組合邏輯或時序邏輯

數字電路該怎么學_數字電路的學習方法(要點、注意事項)

數字電路基礎教程之時序邏輯電路的詳細資料概述

數字電路教程之時序邏輯電路課件的詳細資料免費下載

FPGA零基礎學習:數字電路中的時序邏輯

FPGA零基礎學習:數字電路中的時序邏輯

評論