亞穩態在電路設計中是常見的屬性現象,是指系統處于一種不穩定的狀態,雖然不是平衡狀態,但可在短時間內保持相對穩定的狀態。對工程師來說,亞穩態的存在可以帶來獨特的性質和應用,如非晶態材料、晶體缺陷等。

在材料制備和應用方面,亞穩態也常常是一個挑戰。如何克服亞穩態,使材料轉化為更穩定的狀態,是一個重要的問題。以下是一些克服亞穩態的方法:

1、熱處理

熱處理是一種克服亞穩態的有效方法。通過加熱材料至一定溫度,可以使材料的能量增加,從而突破亞穩態的能壘,轉變為穩定態。熱處理也可以用于改變材料的結構和性質,例如退火可以使晶體缺陷減少,晶粒長大,提高材料的強度和韌性。

2、添加合金元素

添加合金元素也是一種克服亞穩態的方法。合金元素可以改變材料的晶體結構和化學成分,從而降低能壘,使亞穩態轉變為穩定態。例如,將鋰添加到鋼中可以形成亞穩態的奧氏體,從而提高鋼的強度和塑性。

3、熱機械處理

熱機械處理是一種將熱處理和機械加工結合起來的方法,可以通過熱壓、軋制等方式將材料加工成形,使其突破亞穩態能壘,轉變為穩定態。例如,通過軋制可以將亞穩態的合金材料轉變為均勻的晶粒結構,提高材料的強度和韌性。

總之,亞穩態是一種普遍存在的現象。在材料制備和應用方面,克服亞穩態是一個重要的問題。采用熱處理、添加合金元素和熱機械處理等方法,可以提高材料的穩定性和性能。

-

電路設計

+關注

關注

6701文章

2531瀏覽量

213687 -

熱處理

+關注

關注

0文章

117瀏覽量

18566 -

亞穩態

+關注

關注

0文章

47瀏覽量

13492

發布評論請先 登錄

利用IDDR簡化亞穩態方案

xilinx資料:利用IDDR簡化亞穩態

FPGA中亞穩態——讓你無處可逃

FPGA觸發器的亞穩態認識

亞穩態問題解析

簡談FPGA學習中亞穩態現象

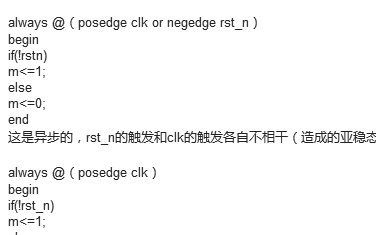

在FPGA復位電路中產生亞穩態的原因

FPGA--中復位電路產生亞穩態的原因

簡談FPGA學習中亞穩態現象

什么是亞穩態?如何克服亞穩態?

什么是亞穩態?如何克服亞穩態?

評論