大家好,又到了每日學(xué)習(xí)的時(shí)間了,今天我們來聊一聊FPGA學(xué)習(xí)中,亞穩(wěn)態(tài)現(xiàn)象。

說起亞穩(wěn)態(tài),首先我們先來了解一下什么叫做亞穩(wěn)態(tài)。亞穩(wěn)態(tài)現(xiàn)象:信號在無關(guān)信號或者異步時(shí)鐘域之間傳輸時(shí)導(dǎo)致數(shù)字器件失效的一種現(xiàn)象。

接下來主要討論在異步時(shí)鐘域之間數(shù)據(jù)傳輸所產(chǎn)生的亞穩(wěn)態(tài)現(xiàn)象,以及如何降低亞穩(wěn)態(tài)現(xiàn)象發(fā)生的概率(只能降低,不能消除),這在FPGA設(shè)計(jì)(尤其是大工程中)是非常重要的。

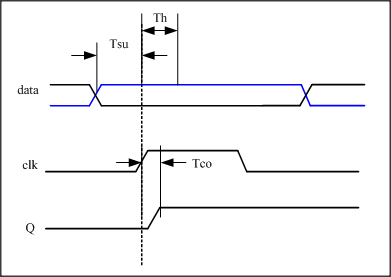

亞穩(wěn)態(tài)的產(chǎn)生:所有的器件都定義了一個(gè)信號時(shí)序要求,只有滿足了這個(gè)要求,才能夠正常的在輸入端獲取數(shù)據(jù),在輸出端輸出數(shù)據(jù)。正常的數(shù)據(jù)傳遞是:在觸發(fā)時(shí)鐘沿前必須有一小段時(shí)間(Tsu)用來穩(wěn)定輸入信號(0 or 1),觸發(fā)時(shí)鐘沿之后需要有一小段特定的時(shí)間(Th)再次穩(wěn)定一下,最后再經(jīng)過一個(gè)特定的始終到輸出延時(shí)(Tco)后才有效。如果數(shù)據(jù)的傳遞過程違反了這個(gè)時(shí)間約束,那么寄存器輸出就會出現(xiàn)亞穩(wěn)態(tài),此時(shí)輸出的詩句是不穩(wěn)定的(在0和1之間游蕩)。但是這種現(xiàn)象并不是絕對的,但是我們在實(shí)際設(shè)計(jì)中應(yīng)當(dāng)盡量避免這種現(xiàn)象。

同步時(shí)鐘系統(tǒng)由于是同步的,沒有兩個(gè)異步的觸發(fā)信號對信號的輸入輸出干擾,所以亞穩(wěn)態(tài)的幾率很小。

異步時(shí)鐘系統(tǒng):先舉個(gè)例子,如下:

always @(posedge clk or negedge rst_n)

begin

if(!rstn)

m<=1;

else

m<=0;

end

這是異步的,rst_n的觸發(fā)和clk的觸發(fā)各自不相干(造成的亞穩(wěn)態(tài)概率較高)。

always @(posedge clk)

begin

if(!rst_n)

m<=1;

else

m<=0;

end

這是同步的,rst_n在clk上升沿的時(shí)候才產(chǎn)生影響,此時(shí)造成的亞穩(wěn)態(tài)概率低很多。

異步時(shí)鐘系統(tǒng)充分的利用了寄存器的端口,無需增加另外的資源,但是亞穩(wěn)態(tài)的概率相對高;

同步時(shí)鐘系統(tǒng)少用了clk復(fù)位端口,額外消耗了了資源,但是降低了亞穩(wěn)態(tài)的發(fā)生概率。

上述異步例子中,如果clk上升沿時(shí),rst-n=0,那么執(zhí)行m<=1;但是rst_n和clk變化的時(shí)間差很短,不滿足穩(wěn)態(tài)時(shí)間要求的就會相互干擾,造成亞穩(wěn)態(tài)的發(fā)生。當(dāng)然有的人會認(rèn)為同步似乎也會產(chǎn)生這種影響,但是相對而言幾率小得多。

在此前提下,在特權(quán)同學(xué)的書中,提出了異步復(fù)位,同步釋放的電路概念。(電路網(wǎng)上好多),該電路目的:既不解決了同步復(fù)位的資源消耗問題,也極大的降低了異步復(fù)位的亞穩(wěn)態(tài)風(fēng)險(xiǎn)。

異步復(fù)位:當(dāng)rst_n= 0 時(shí),一個(gè)clk的上升沿,輸出的rstn_out=0,實(shí)現(xiàn)了異步復(fù)位功能(當(dāng)然這在只有一個(gè)寄存器的一級緩沖下也能實(shí)現(xiàn)),重點(diǎn)在于同步釋放環(huán)節(jié)。

同步釋放:當(dāng)rst_n在clk上升沿后很短的時(shí)間內(nèi)回歸1,那么就會造成前一級的亞穩(wěn)態(tài)的出現(xiàn),其實(shí)后一級也出現(xiàn)了,但是如果rst_n被認(rèn)為任然是0,那么輸出也就是0,如果被認(rèn)為是1,rstn_out接受的是前一級的上一個(gè)輸出值(還是0),這就是同步釋放的由來,完美解決問題。

這僅是本人學(xué)習(xí)初學(xué)FPGA的學(xué)習(xí)筆記,僅供參考。

今天就聊到這里,各位,加油。

發(fā)布評論請先 登錄

FPGA中亞穩(wěn)態(tài)——讓你無處可逃

FPGA中亞穩(wěn)態(tài)——讓你無處可逃

FPGA觸發(fā)器的亞穩(wěn)態(tài)認(rèn)識

亞穩(wěn)態(tài)問題解析

簡談FPGA學(xué)習(xí)中亞穩(wěn)態(tài)現(xiàn)象

FPGA的亞穩(wěn)態(tài)現(xiàn)象是什么?

在FPGA復(fù)位電路中產(chǎn)生亞穩(wěn)態(tài)的原因

簡談FPGA設(shè)計(jì)中亞穩(wěn)態(tài)現(xiàn)象

在FPGA中,同步信號、異步信號和亞穩(wěn)態(tài)的理解

簡述FPGA中亞穩(wěn)態(tài)的產(chǎn)生機(jī)理及其消除方法

如何理解FPGA設(shè)計(jì)中的打拍(寄存)和亞穩(wěn)態(tài)

什么是亞穩(wěn)態(tài)?如何克服亞穩(wěn)態(tài)?

FPGA設(shè)計(jì)中的亞穩(wěn)態(tài)解析

簡談FPGA學(xué)習(xí)中亞穩(wěn)態(tài)現(xiàn)象

簡談FPGA學(xué)習(xí)中亞穩(wěn)態(tài)現(xiàn)象

評論