前言

本文介紹了設(shè)計(jì)濾波器的FPGA實(shí)現(xiàn)步驟,并結(jié)合杜勇老師的書籍中的并行FIR濾波器部分進(jìn)行一步步實(shí)現(xiàn)硬件設(shè)計(jì),對書中的架構(gòu)做了復(fù)現(xiàn)以及解讀,并進(jìn)行了仿真驗(yàn)證。

并行FIR濾波器FPGA實(shí)現(xiàn)

FIR濾波器的結(jié)構(gòu)形式時,介紹了直接型、級聯(lián)型、頻率取樣型和快速卷積型4種。在FPGA實(shí)現(xiàn)時,最常用的是最簡單的直接型結(jié)構(gòu)。FPGA實(shí)現(xiàn)直接型結(jié)構(gòu)的FIR濾波器,可以采用串行結(jié)構(gòu)、并行結(jié)構(gòu)等不同中的結(jié)構(gòu)設(shè)計(jì),上文根據(jù)書中提供的架構(gòu)完成了串行 FIR濾波器的實(shí)現(xiàn),本文沿用上文的基本代碼結(jié)構(gòu),按照并行FIR濾波器的架構(gòu)完成電路描述。

FIR濾波器需求

設(shè)計(jì)一個15階(長度為16)的低通線性相位FIR濾波器,采用窗函數(shù)設(shè)計(jì),截止頻率為500 Hz,采樣頻率為2 000 Hz;采用FPGA實(shí)現(xiàn)并行結(jié)構(gòu)的濾波器,系數(shù)的量化位數(shù)為12比特,輸入數(shù)據(jù)位寬為12比特,輸出數(shù)據(jù)位寬為29比特,系統(tǒng)時鐘為16 kHz。

濾波器系數(shù)確定與量化

確定濾波器的結(jié)構(gòu)后,就根據(jù)濾波器進(jìn)行設(shè)計(jì)代碼仿真,這里引用書中的仿真設(shè)計(jì),并將濾波器參數(shù)系數(shù)量化。確定濾波器系數(shù)的方法有很多,可以使用MATLAB中豐富的函數(shù)實(shí)現(xiàn),或者使用相關(guān)濾波器設(shè)計(jì)的軟件工具,定制滿足當(dāng)前需求的窗函數(shù)的濾波器系數(shù)。具體量化系數(shù)確定可參考上文《數(shù)字信號處理-09-串行FIR濾波器MATLAB與FPGA實(shí)現(xiàn)》中的相關(guān)內(nèi)容,或者參考杜勇老師的書中的內(nèi)容。

硬件架構(gòu)

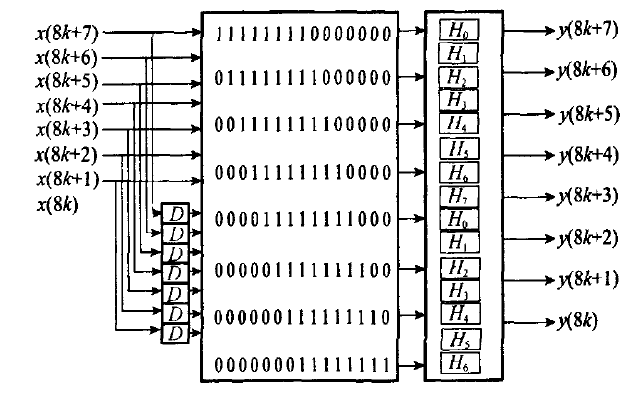

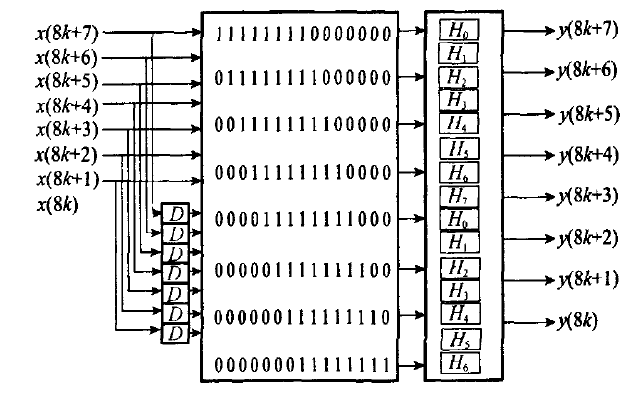

下圖為杜勇老師的《數(shù)字濾波器的MATLAB與FPGA實(shí)現(xiàn)》實(shí)現(xiàn)的并行FIR濾波器的結(jié)構(gòu)圖。因?yàn)镕IR濾波器參數(shù)對稱,所以同時計(jì)算相應(yīng)的對稱結(jié)構(gòu)的值,將對稱系數(shù)的X(n)相加后,可調(diào)用8個乘法器,完成對濾波器的乘法運(yùn)算,所以針對并行濾波器的架構(gòu)數(shù)據(jù)的輸入速率和時鐘可以相同,每一個時鐘周期流水輸出一個濾波后的信號值。圖中的8輸入的加法器,可以替換成N/2;這樣就得到了一個通用化的并行FIR濾波器結(jié)構(gòu)圖。

并行FIR濾波器

并行實(shí)現(xiàn)FIR濾波器,雖然浪費(fèi)了加法器和乘法器的資源,但是提升了整個濾波器實(shí)現(xiàn)的性能,當(dāng)濾波器的系數(shù)長度N增大時,數(shù)據(jù)的吞吐速率不變(暫且不考慮面積增大對性能的影響),但帶來的壞處就是會用掉相應(yīng)倍數(shù)的邏輯資源和運(yùn)算資源,速度和面積本來就是魚和熊掌的關(guān)系,在實(shí)際應(yīng)用中應(yīng)當(dāng)做相應(yīng)的權(quán)衡和割舍。

根據(jù)架構(gòu)描述電路

根據(jù)杜勇老師書中提供的架構(gòu),對電路進(jìn)行描述,同樣沿用了前文的通用化的模板,后期可根據(jù)參數(shù)輸入來適配不同濾波器長度的設(shè)計(jì)。

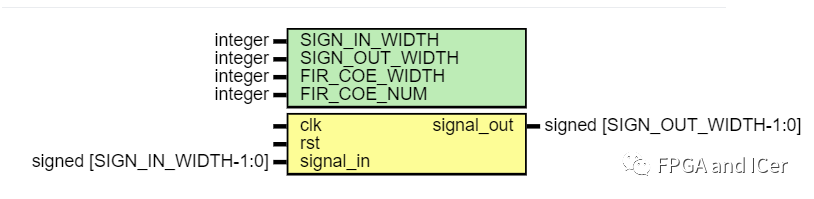

實(shí)現(xiàn)模塊框圖

接口描述如下:

接口描述

參數(shù)描述如下:

參數(shù)描述

代碼如下:

`timescale 1ns / 1ps

module Fir_Parallel(

input clk,//!系統(tǒng)時鐘

input rst,//!復(fù)位信號

input signed [SIGN_IN_WIDTH-1:0] signal_in,//!信號輸入

output signed [SIGN_OUT_WIDTH-1:0] signal_out//!信號輸出,信號輸出速度和輸入速度相同

);

//

parameter integer SIGN_IN_WIDTH = 12 ;//!信號輸入位寬

parameter integer SIGN_OUT_WIDTH = 29 ;//!信號輸出位寬

parameter integer FIR_COE_WIDTH = 12 ;//!濾波器系數(shù)位寬

parameter integer FIR_COE_NUM = 16 ;//!濾波器長度

localparam integer FIR_WIDTH_DIV_2 = FIR_COE_NUM/2 ;

function [FIR_COE_WIDTH-1:0] coe_data;

input [FIR_WIDTH_DIV_2-1:0] index;

begin

case(index)

'd0:coe_data='h000;

'd1:coe_data='hffd;

'd2:coe_data='h00f;

'd3:coe_data='h02e;

'd4:coe_data='hf8b;

'd5:coe_data='hef9;

'd6:coe_data='h24e;

'd7:coe_data='h7ff;

endcase

end

endfunction

integer i;

genvar j;

//!濾波器系數(shù)加載

wire signed [FIR_COE_WIDTH-1:0] coe[FIR_WIDTH_DIV_2-1:0];

generate

for (j=0; j

代碼解讀

關(guān)于加載濾波器系數(shù)的部分,我這里使用了function做了包裝,以便于后續(xù)修改濾波器長度時,可以通過腳本生成function去增加濾波器系數(shù)的長度。

function [FIR_COE_WIDTH-1:0] coe_data;

input [FIR_WIDTH_DIV_2-1:0] index;

begin

case(index)

'd0:coe_data='h000;

'd1:coe_data='hffd;

'd2:coe_data='h00f;

'd3:coe_data='h02e;

'd4:coe_data='hf8b;

'd5:coe_data='hef9;

'd6:coe_data='h24e;

'd7:coe_data='h7ff;

endcase

end

endfunction

針對乘法運(yùn)算,這里沒有使用IP,但是為了使得該部分運(yùn)算使用DSP資源,更好地提升性能,因此該信號的運(yùn)算使用dsp48資源,所以在信號聲明時前面加了(*use_dsp48="yes"*)。

關(guān)于杜勇老師書中寫的信號與系數(shù)相乘后的結(jié)果針對sum信號使用了阻塞賦值的部分,個人覺得這個在時序邏輯中是不太好的設(shè)計(jì),使用的代碼如下,雖然會簡化乘累加的過程,但是針對實(shí)際使用的工程來說,這個是不好的代碼風(fēng)格。

always @(posedge clk)begin

if (rst=='b1)begin

sum = 'd0;

sign_out <= 'd0;

end

else begin

sign_out <= sum;

sum = 'd0;

for (i=0; i

所以這里我直接做了展開處理,將8個結(jié)果做了加法。

電路架構(gòu)優(yōu)化

我認(rèn)為在隨著濾波器規(guī)模變大運(yùn)算的數(shù)據(jù)位寬增加時,信號與系數(shù)相乘后的結(jié)果進(jìn)行累加操作的部分,組合邏輯的延時相對會增加很多,為了進(jìn)一步提升電路架構(gòu)的性能,可對該部分進(jìn)行加法樹的平衡,打拍優(yōu)化加法樹結(jié)構(gòu),應(yīng)該有可能進(jìn)一步提升電路架構(gòu)的性能。

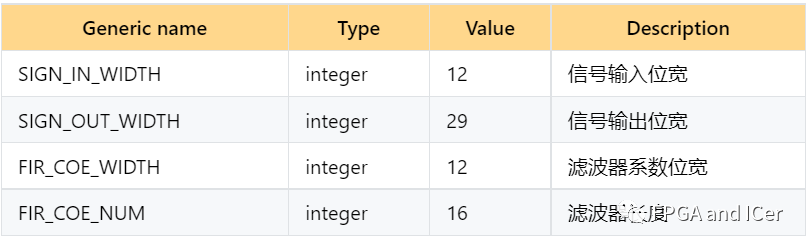

仿真設(shè)計(jì)

仿真數(shù)據(jù)設(shè)計(jì)

為了驗(yàn)證并行設(shè)計(jì)代碼的正確性。這里使用MATLAB腳本產(chǎn)生了一個混頻信號,混頻的頻率為100hz和700hz的疊加,然后將混頻信號進(jìn)行量化處理并導(dǎo)出txt文件以供仿真文件讀取。

clc;close all;clear all;

Fs = 2000; %采樣頻率

N = 2^10; %采樣點(diǎn)數(shù)

f1=300; %正弦波1頻率

f2=400; %正弦波1頻率

t=[0:N-1]/Fs; %時間序列

s1 = sin(2*pi*f1*t) ;

s2 = sin(2*pi*f2*t) ;

s = s1 .* s2;

figure(1);

subplot(1,2,1);

plot(t,s,'r','LineWidth',1.2);

title('時域波形');

axis([0,100/Fs,-3,3]);

set(gca,'LineWidth',1.2);

%轉(zhuǎn)化為位寬12bit數(shù)據(jù)

s_12bit=s./max(s).*(2.^11 - 1); % DA輸入波形,量化到16bit

s_12bit(find(s_12bit<0) ) = s_12bit(find(s_12bit<0) ) + 2^12 - 1;

s_12bit = fix(s_12bit);

s_12bit = dec2hex(s_12bit);

% %生成文件

fid= fopen('sin_data.txt','w+');

%生成十六進(jìn)制

for i=1:N

fprintf(fid,'%s',s_12bit(i,:));

fprintf(fid,'\\r\\n');

end

fclose(fid);

%% 設(shè)計(jì)驗(yàn)證

N=16; %濾波器長度

fs=2000; %采樣頻率

fc=500; %低通濾波器的截止頻率

B=12; %量化位數(shù)

%生成各種窗函數(shù)

w_kais=blackman(N)';

%采用fir1函數(shù)設(shè)計(jì)FIR濾波器

b_kais=fir1(N-1,fc*2/fs,w_kais);

ss=conv(b_kais,s);

subplot(1,2,2);

plot(t(20:1000),ss(20:1000));

title('濾波后信號');

axis([0,100/Fs,-1,1]);

set(gca,'LineWidth',1.2);

運(yùn)行仿真后,根據(jù)設(shè)計(jì)的濾波器系數(shù)進(jìn)行仿真,發(fā)現(xiàn)可以正常濾波除去高頻分量。

濾波仿真效果

仿真激勵文件編寫

`timescale 1ns / 1ps

module Fir_Parallel_tb;

// Parameters

localparam integer SIGN_IN_WIDTH = 12;

localparam integer SIGN_OUT_WIDTH = 29;

localparam integer FIR_COE_WIDTH = 12;

localparam integer FIR_COE_NUM = 16;

// Ports

reg clk = 1;

reg rst = 1;

reg [SIGN_IN_WIDTH-1:0] signal_in;

wire [SIGN_OUT_WIDTH-1:0] signal_out;

Fir_Parallel #(

.SIGN_IN_WIDTH(SIGN_IN_WIDTH ),

.SIGN_OUT_WIDTH(SIGN_OUT_WIDTH ),

.FIR_COE_WIDTH(FIR_COE_WIDTH ),

.FIR_COE_NUM (FIR_COE_NUM )

)Fir_Parallel_dut (

.clk (clk ),

.rst (rst ),

.signal_in (signal_in ),

.signal_out ( signal_out)

);

reg [11:0] mem [0:99];

reg [9:0] addr ;

// reg [11:0]data_out ;

always #(10*1)

begin

if(rst==0)

addr = addr + 10'd1;

signal_in = mem[addr][11:0];

end

always

#5 clk = ! clk ;

initial

begin

signal_in =0;

$readmemh("sin_data.txt",mem);

addr = 10'd0;

#10;

rst = 0;

end

endmodule

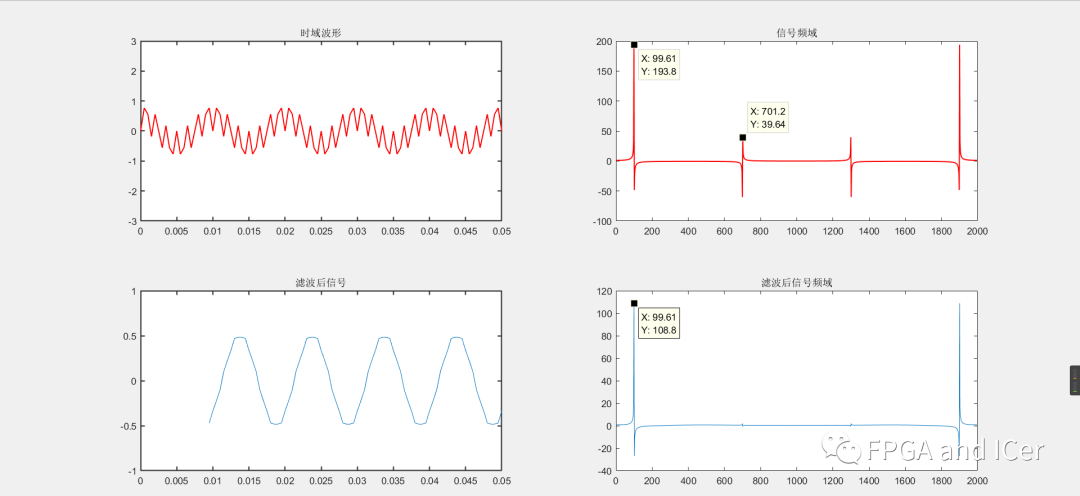

運(yùn)行仿真,查看波形可見,濾波效果和仿真結(jié)果一致。

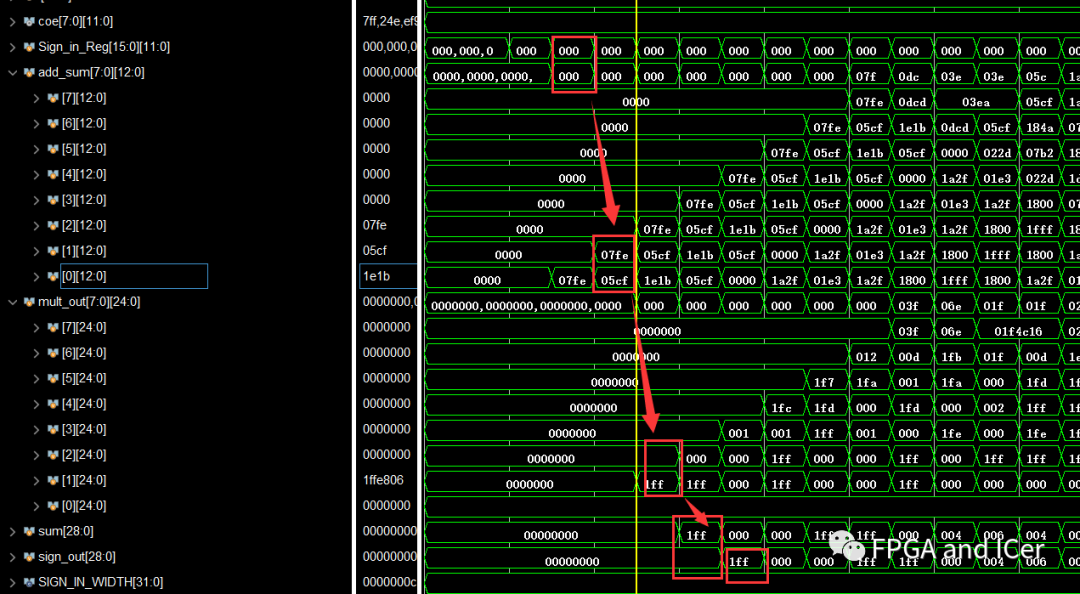

仿真波形

延遲分析

該架構(gòu)的數(shù)據(jù)輸入后,每四個時鐘周期后輸出一個數(shù)據(jù),其中,一個時鐘周期用于X(n)的加和,一個時鐘周期用于計(jì)算信號和濾波器系數(shù)相乘的結(jié)果,一個時鐘周期用于乘法輸出后的數(shù)據(jù)做累加處理,一個時鐘用于讀取累加后的結(jié)果。

延時分析

-

FPGA

+關(guān)注

關(guān)注

1643文章

21983瀏覽量

614617 -

matlab

+關(guān)注

關(guān)注

188文章

2998瀏覽量

233383 -

濾波器

+關(guān)注

關(guān)注

162文章

8095瀏覽量

181209 -

FIR

+關(guān)注

關(guān)注

4文章

151瀏覽量

34074 -

函數(shù)

+關(guān)注

關(guān)注

3文章

4372瀏覽量

64302

發(fā)布評論請先 登錄

matlab與FPGA數(shù)字信號處理系列 Verilog 實(shí)現(xiàn)并行 FIR 濾波器

基于FPGA的FIR濾波器設(shè)計(jì)與實(shí)現(xiàn)

并行FIR濾波器Verilog設(shè)計(jì)

怎么利用FPGA實(shí)現(xiàn)FIR濾波器?

如何用用FPGA實(shí)現(xiàn)FIR濾波器

基于MATLAB及FPGA的FIR低通濾波器的設(shè)計(jì)

基于Matlab的FIR帶通濾波器設(shè)計(jì)與實(shí)現(xiàn)

基于MATLAB與FPGA的FIR濾波器設(shè)計(jì)與仿真

基于Matlab/Simulink的FIR數(shù)字濾波器的設(shè)計(jì)與實(shí)現(xiàn)

基于matlab和fpga的FIR濾波器設(shè)計(jì)

基于FPGA的FIR濾波器設(shè)計(jì)與實(shí)現(xiàn)

FIR濾波器的FPGA設(shè)計(jì)與實(shí)現(xiàn)

如何使用FPGA實(shí)現(xiàn)實(shí)現(xiàn)高速并行FIR濾波器

如何使用FPGA實(shí)現(xiàn)實(shí)現(xiàn)高速并行FIR濾波器

并行FIR濾波器MATLAB與FPGA實(shí)現(xiàn)

并行FIR濾波器MATLAB與FPGA實(shí)現(xiàn)

評論