隨著數(shù)據(jù)中心和人工智能應(yīng)用成為中心舞臺,過去幾年見證了各種高帶寬互連技術(shù)的出現(xiàn)。計算高速鏈路 (CXL) 是一種有抱負(fù)的新型互連技術(shù),適用于高帶寬設(shè)備,例如帶內(nèi)存的加速器、高密度計算卡和由 GPU 組成的加速器。Synopsys 開發(fā)了一個全面的 CXL 驗證子系統(tǒng),計劃發(fā)布其第一個 CXL 應(yīng)用程序的早期采用者已經(jīng)使用該系統(tǒng)。CXL 驗證子系統(tǒng)利用業(yè)界流行的 Synopsys PCI Express 驗證 IP。

CXL 是一種在主機(jī)(通常是 CPU)和設(shè)備(通常是附加了內(nèi)存的加速器)之間實現(xiàn)高帶寬、低延遲鏈接的技術(shù)。CXL 堆棧專為低延遲而設(shè)計,使用 PCIe 電氣和附加卡的標(biāo)準(zhǔn) PCIe 外形規(guī)格。CXL 使用靈活的處理器端口,可以自動協(xié)商到標(biāo)準(zhǔn) PCIe 事務(wù)協(xié)議或備用 CXL 事務(wù)協(xié)議。

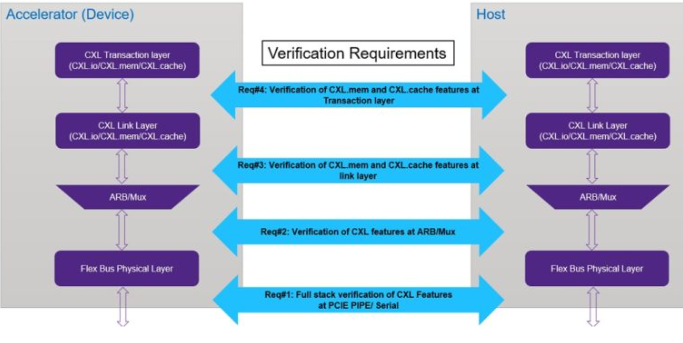

CXL 規(guī)范建立在完善的 PCIe 基礎(chǔ)架構(gòu)之上,并利用其基于層的架構(gòu),每一層都有一個目標(biāo)角色。

圖 1:CXL 分層體系結(jié)構(gòu)和驗證要求

CXL 事務(wù)層

CXL 事務(wù)層分為 PCIe/CXL.io 事務(wù)層和 CXL.cache+CXL.mem 事務(wù)層。CXL.cache+CXL.mem 事務(wù)層支持生成請求、響應(yīng)和數(shù)據(jù)的功能。

CXL 鏈路層

CXL 鏈路層分為 PCIe/CXL.io 鏈路層和 CXL.cache+CXL.mem 鏈路層。鏈路層是事務(wù)層和物理層之間的中間層。它有助于維護(hù)整個鏈路上的事務(wù)的可靠性。

CXL ARB/MUX

CXL ARB/MUX 提供 CXL.io 和 CXL.cache+CXL.mem 流量的仲裁和多路復(fù)用,朝向物理層。

CXL 物理層

物理層由邏輯子塊和電氣子塊組成。邏輯子塊最初在 PCIe 模式下運(yùn)行,并根據(jù)備用協(xié)議協(xié)商切換到 CXL 模式。電氣子塊始終遵循 PCIe 規(guī)范。

對于 CXL 流量,數(shù)據(jù)速率與 PCIe 規(guī)范定義的速率一致。在 CXL 模式下,支持 8 GT/s、16 GT/s 或 32 GT/s 的數(shù)據(jù)速率。在 CXL 模式下,支持 x16、x8、x4、x2 的鏈接寬度。x1 的鏈路寬度也支持降級模式。

數(shù)據(jù)的爆炸式增長以及AI和加密的快速創(chuàng)新催生了GPU加速器,需要與處理器建立高性能連接。雖然存在其他互連協(xié)議,但 CXL 在提供 CPU/設(shè)備內(nèi)存一致性、降低設(shè)備復(fù)雜性以及捆綁在單一技術(shù)中的行業(yè)標(biāo)準(zhǔn)物理和電氣接口方面是獨(dú)一無二的,可實現(xiàn)最佳的即插即用體驗。

審核編輯:郭婷

-

主機(jī)

+關(guān)注

關(guān)注

0文章

1036瀏覽量

35905 -

PCIe

+關(guān)注

關(guān)注

16文章

1331瀏覽量

84912 -

加速器卡

+關(guān)注

關(guān)注

0文章

19瀏覽量

8842

發(fā)布評論請先 登錄

揭開特斯拉超級大廠Gigafactory的神秘面紗

[分享]揭開zzz 手機(jī)神秘面紗

揭開連接出現(xiàn)小嘆號不能上網(wǎng)問題的神秘面紗

蘋果iPhone手機(jī)神秘面紗被揭開

揭開實時以太網(wǎng)神秘的面紗

揭開vivo APEX全面屏的神秘面紗

Duskers - 揭開科幻生存游戲中的神秘面紗

MT-001: 揭開公式(SNR = 6.02N + 1.76dB)的神秘面紗

揭開醫(yī)療警報設(shè)計的神秘面紗,第1部分:IEC60601-1-8標(biāo)準(zhǔn)要求

揭開數(shù)字健康應(yīng)用的AI和機(jī)器學(xué)習(xí)的神秘面紗

揭開快充芯片的神秘面紗

用智能DAC揭開醫(yī)療報警設(shè)計的神秘面紗

揭開CXL的神秘面紗:概述

揭開CXL的神秘面紗:概述

評論