重新綜合時間太長?

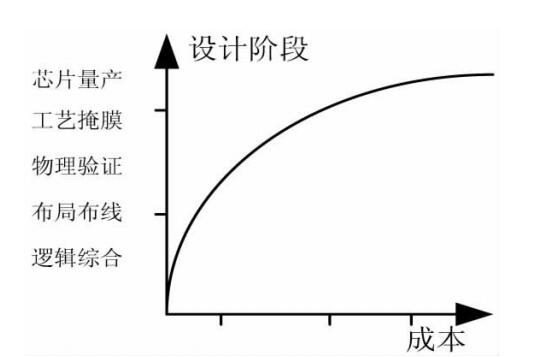

近幾年,芯片設計規模越來越大,這使得重跑一次綜合需要長達數小時,甚至幾天時間。

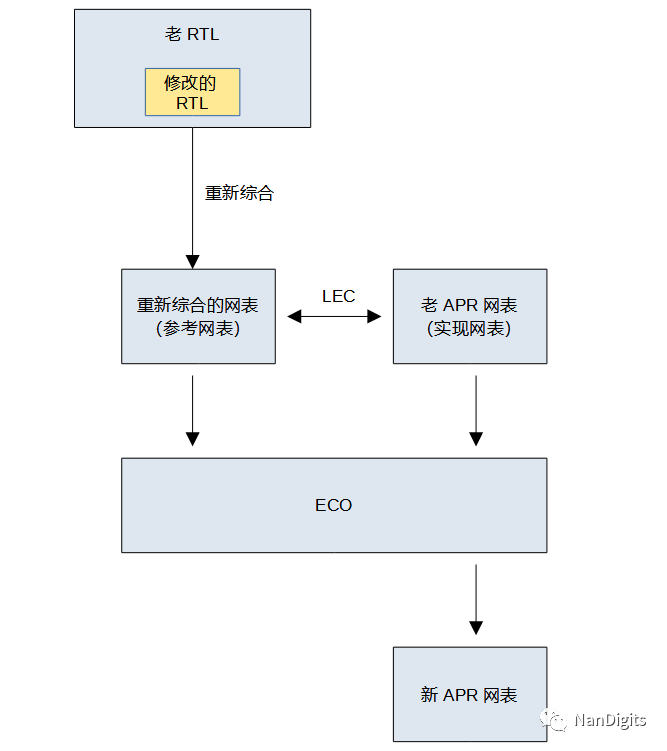

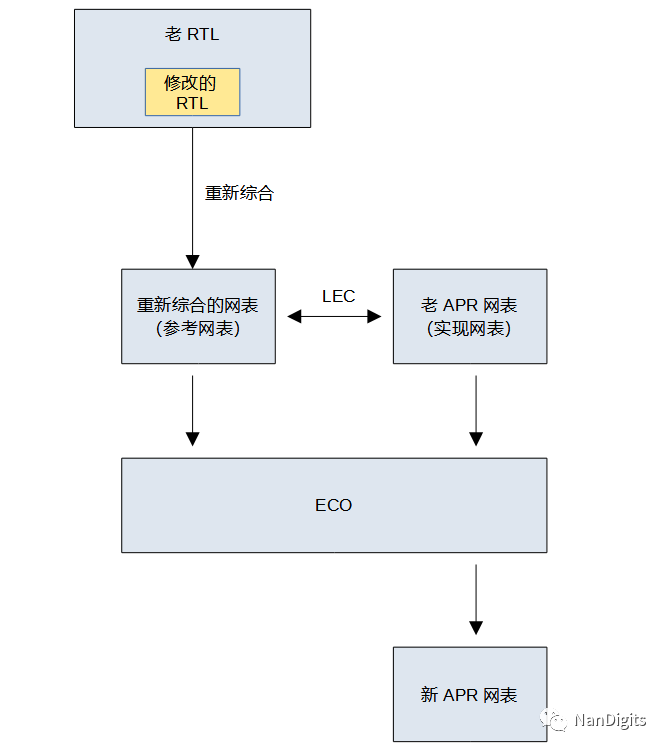

傳統的自動功能ECO流程需要把修改后的所有RTL(包括修改過的和沒有修改過的)重新綜合成參考網表,如下圖。即使是RTL層面很小的、非常簡單的修改,也必須重走一遍綜合流程。重新綜合會消耗大量的時間,尤其對于大型項目,重新綜合會嚴重影響芯片功能ECO的進度。

一種全新的解決方案

針對這種場景,我們想到了一種解決方案:直接在需要ECO的網表(比如APR網表)里插入RTL代碼。

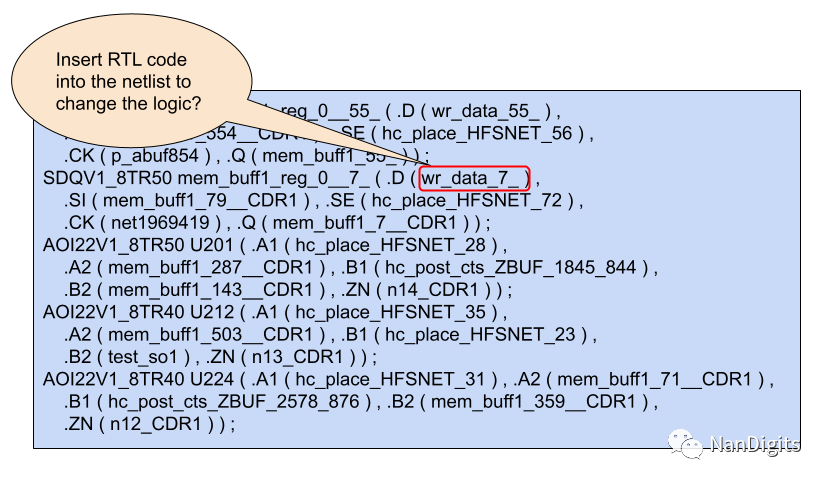

我們來看下面這個例子,比如ECO時需要對DFF的D端的net wr_data_7_做一些預處理。下圖是原網表。

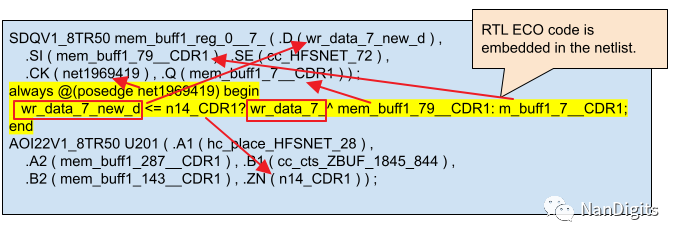

我們在網表里直接插入了RTL的always語句,對wr_data_7_進行了打拍和簡單邏輯處理(新加的邏輯所需要的輸入信號都可以在原網表中找到),把處理后的信號wr_data_7_new_d接到原DFF的D端,如下圖中的箭頭。這種在網表里直接插入和修改的RTL也叫做RTL補丁。

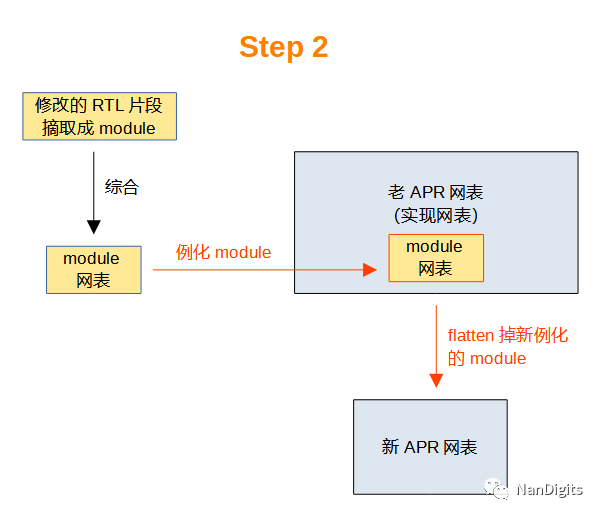

GOF ECO讀入包含插入RTL補丁的網表,做遞增式綜合。遞增式綜合會根據RTL補丁的改動,對網表做必要的修改。所以,最終的ECO網表里就精確反映了邏輯補丁。當處理相對簡單,單一的邏輯修改時,傳統的方法是摘取這個修改的代碼片段為一個新的module,對這個新模塊進行綜合,再把綜合得到的網表片段(也叫邏輯補丁)插回原網表里,如下圖。有一個要特別注意的是,插回網表時net名字可能沖突。

GOF ECO提供了一種全自動化的、可行的解決辦法來在網表里直接插入RTL補丁,來幫助遞增式綜合。在遞增式綜合過程中,GOF ECO只針對RTL補丁,不影響網表的其余部分,這可以最小程度地影響原網表。采用這種方法,GOFECO可以生成更優化的網表,同時也盡可能保留原網表的結構和格式。

這種方法不需要完整的重新綜合,就可以把RTL修改的部分無縫的集成到原網表里。所以,只有設計中有修改的部分才會做遞增式綜合,這會顯著地節省完整的重新綜合所需要的時間。

利用遞增式RTL補丁做功能ECO的方法,前端設計工程師也可高效地做功能修改,而不用擔心影響項目進度。這種方法是最佳的ECO實現方案,它不僅能把插入的RTL遞增式綜合成網表補丁,還可以盡量保持原網表的完整性。

GOFECO還提供了更多插入RTL的便捷方法

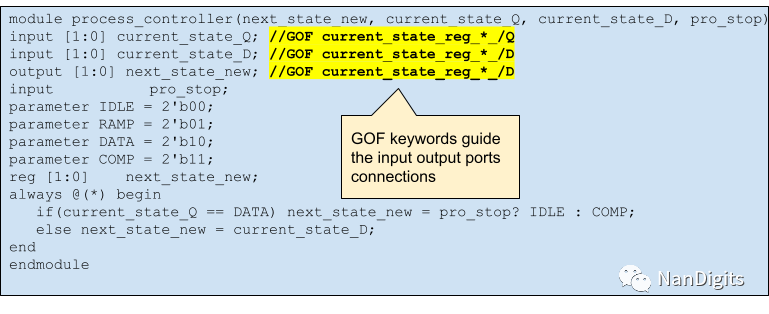

如下圖,在寫獨立RTL補丁文件時,GOF ECO提供了一些便捷方法:在module端口聲明的后面用特殊的注釋來指明連接關系。這個例子中,通過注釋指明了補丁模塊信號與狀態機如何連接。GOF ECO讀到RTL補丁中的這些特殊注釋后,會自動執行對應的修改和連接。

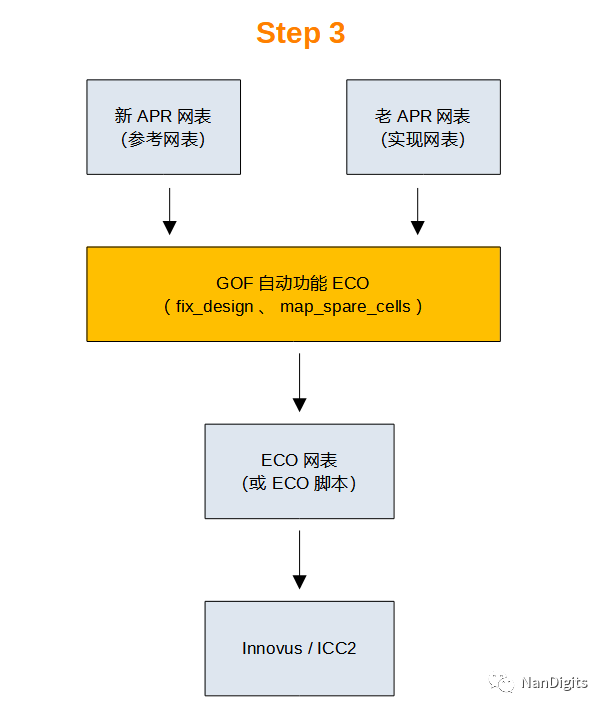

生成最終的ECO網表

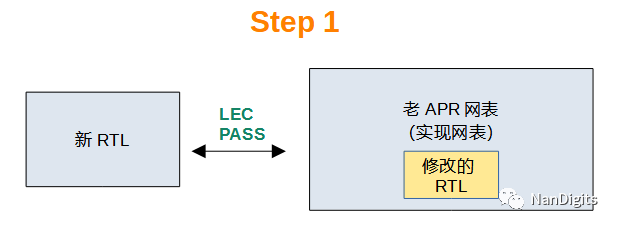

最后,我們利用Step2得到網表作為參考網表,對原APR網表進行自動功能ECO。從RTL補丁到網表補丁、再map成spare cells補丁,這樣我們就得到最終的ECO網表或者ECO腳本(根據情況二選一即可)。

-

芯片設計

+關注

關注

15文章

1074瀏覽量

55513 -

RTL

+關注

關注

1文章

388瀏覽量

60795 -

ECO

+關注

關注

0文章

52瀏覽量

15140

原文標題:直接在網表中插入RTL來快速做芯片功能ECO

文章出處:【微信號:ExASIC,微信公眾號:ExASIC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

使用ORCAD做原理圖PADS做PCB的方法步驟

RTL8309SC ***原裝進口 瑞昱 芯片 光耦IC 以太網控制芯片 電子元器件

有利于驗證未測試功能的RTL緩沖器插入和故障分級技術

ECO技術在SoC芯片設計中的應用

自動ECO參考網表來自動修改實現網表

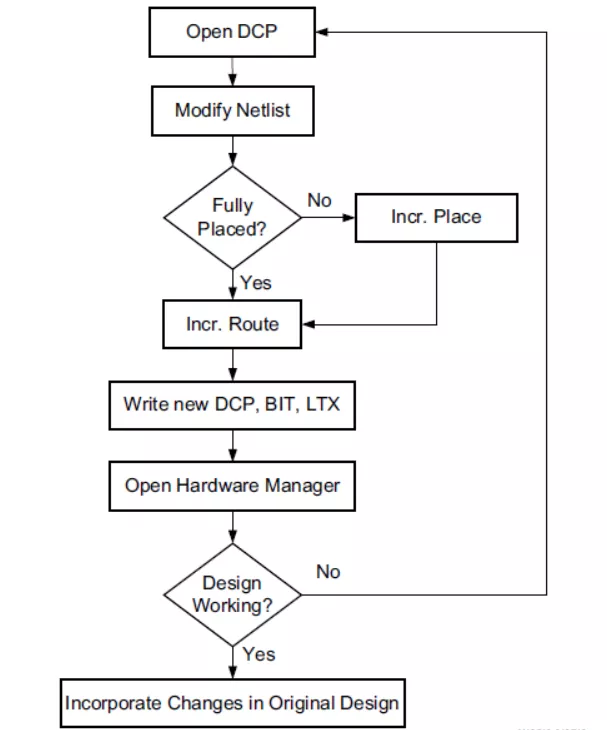

詳解Xilinx FPGA的ECO功能

直接在網表中插入RTL來快速做芯片功能ECO

直接在網表中插入RTL來快速做芯片功能ECO

評論