1. 背景介紹

1.1. Tensilica介紹

Tensilica 是一個(gè)迅速成長(zhǎng)的公司,公司主要產(chǎn)品是在專業(yè)性應(yīng)用程序微處理器上,為現(xiàn)今高容量嵌入式系統(tǒng)提供最優(yōu)良的解決方案。公司成立于1997年7月,該公司的投資者包括三家聲名卓著的創(chuàng)投公司:Oak Investment Partners, Worldview Technology Partners 和 Foundation Capital, 與高科技電子業(yè)內(nèi)著名的五家公司:Cisco Systems,Inc,Matsushita Electric Industrial Company Ltd, Altera Corporation,NEC Corporation 和 Conexant Systems。Tensilica的創(chuàng)始人為Chris Rowen,同時(shí)也是第一任CEO,他原來曾任職于Intel,Stanford,MIPS,SGI和Synopsys,同時(shí)他也是可重構(gòu)處理思想的提出者和實(shí)踐者。

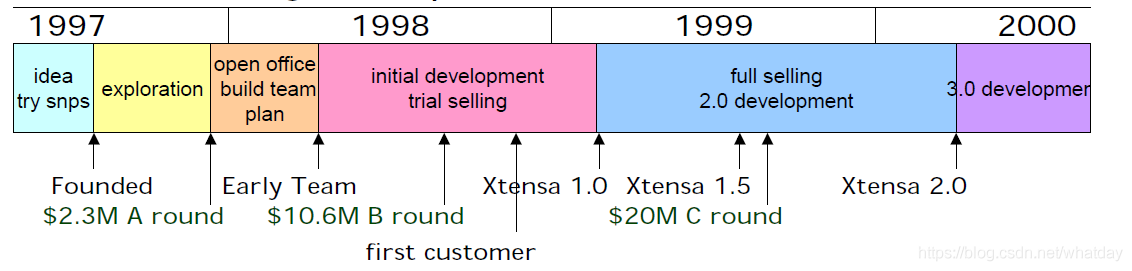

Tensilica公司創(chuàng)立的目的則是提供一種可以實(shí)現(xiàn)可重構(gòu)的、核基于ASIC的、擁有對(duì)應(yīng)軟件開發(fā)工具的專用微處理器解決方法。通過前期技術(shù)上的發(fā)展以及三輪融資,Xtensa處理器誕生了。圖1展示了Tensilica公司創(chuàng)業(yè)起步階段的發(fā)展?fàn)顩r:

圖1:Tensilica公司創(chuàng)業(yè)起步階段的發(fā)展?fàn)顩r

Tensilica公司于2013年3月被Cadence公司以3.8億的價(jià)格收購,為Cadence在當(dāng)時(shí)最大的一次收購。Tensilica公司2012年銷售額為4400萬美元,收購價(jià)超過其營(yíng)業(yè)額的八倍,這也充分顯示了Tensilica公司的價(jià)值。

1.2. SOC處理器

在如今復(fù)雜的SOC設(shè)計(jì)中可以看到有很多種的嵌入式處理器,從通用的處理器到專用的處理器。

通用的嵌入式處理器雖然可以很好的處理各種的控制任務(wù),但當(dāng)遇到像神經(jīng)網(wǎng)路處理、基帶數(shù)據(jù)包處理、圖像處理、音頻處理以及信息加密處理這中復(fù)雜的大數(shù)據(jù)處理時(shí),它們的結(jié)構(gòu)、處理方法以及帶寬的限制使其顯示出極大地劣勢(shì)。而且對(duì)于內(nèi)存大小、cache尺寸和總線接口等的可選擇性較小,一般是通過提升頻率來提高性能,限制較大。

芯片設(shè)計(jì)者也曾將目光轉(zhuǎn)向硬接線邏輯(設(shè)計(jì)RTL級(jí)blocks)來提升某些主要功能的性能。不過RTL設(shè)計(jì)的設(shè)計(jì)周期很長(zhǎng),而且驗(yàn)證所花費(fèi)的時(shí)間更長(zhǎng),同時(shí)它也缺少必要的可編程性和靈活性。

Xtensa LX系列處理器具有很強(qiáng)的可重構(gòu)性和可拓展性,是進(jìn)行復(fù)雜密集型數(shù)字信號(hào)處理應(yīng)用的理想之選,而一個(gè)固化的RTL應(yīng)用也只能作為其他選擇。Xtensa 處理器具有不同于其它傳統(tǒng)式的嵌入式處理器核心,改變了單芯片系統(tǒng)的設(shè)計(jì)規(guī)則。采用 Xtensa 的技術(shù)時(shí),系統(tǒng)設(shè)計(jì)工程師可以挑選所需的單元架構(gòu),再加上自創(chuàng)的新指令與硬件執(zhí)行單元,就可以設(shè)計(jì)出比其它傳統(tǒng)方式強(qiáng)大數(shù)倍的處理器核心。Xtensa 生產(chǎn)器可以針對(duì)每一個(gè)處理器的特殊組合,自動(dòng)有效地產(chǎn)生出一套包括操作系統(tǒng),完善周全的軟件工具。可以自由裝組的 Xtensa 處理器,其設(shè)計(jì)方式彈性大,功效高,是所有高合成的單芯片系統(tǒng)的最佳選擇。它采用硬件可重構(gòu)加軟件編程的方式,既提升了處理器的運(yùn)算性能又通過軟件便于實(shí)現(xiàn)控制[1]。

2. Xtensa處理器的結(jié)構(gòu)

對(duì)于Xtensa處理器結(jié)構(gòu),接下來分硬件結(jié)構(gòu)和指令集架構(gòu)兩部分分別介紹。

2.1. Xtensa處理器的硬件結(jié)構(gòu)

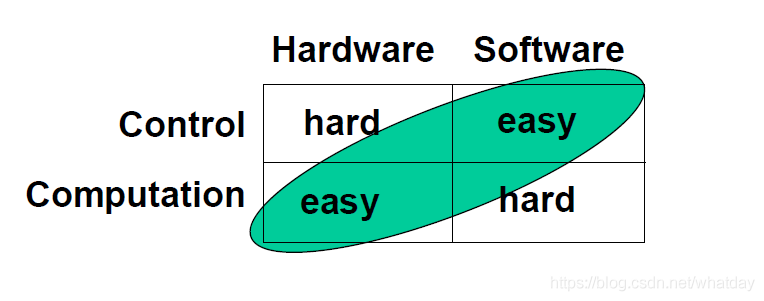

純硬件的系統(tǒng)便于進(jìn)行計(jì)算,不便于實(shí)現(xiàn)控制,而軟件系統(tǒng)則正好相反(如圖2),Xtensa處理器正好利用了兩者的優(yōu)勢(shì)來進(jìn)行處理器設(shè)計(jì),它采用硬件可重構(gòu)加軟件編程的方式,既提升了處理器的運(yùn)算性能又通過軟件便于實(shí)現(xiàn)控制。

圖2 軟硬件在計(jì)算和控制方面的優(yōu)劣勢(shì)[2]

Xtensa LX7處理器結(jié)構(gòu)如圖3所示。

圖3 Xtensa LX7處理器結(jié)構(gòu)圖[3]

由上圖可以看到,Xtensa LX7處理器的硬件結(jié)構(gòu)包含基本模塊、可重構(gòu)模塊、可選擇模塊、用戶定義模塊、功能模塊、以及拓展模塊。Xtensa LX7處理器以基本模塊為核心,SOC開發(fā)者可以根據(jù)需要的功能在功能模塊通過編碼或者圖形界面選擇相應(yīng)的模塊進(jìn)行組合或者對(duì)可重構(gòu)模塊進(jìn)行對(duì)應(yīng)重構(gòu)來優(yōu)化運(yùn)算的性能,并能夠使用戶在較短的時(shí)間內(nèi)設(shè)計(jì)出面向特定應(yīng)用的處理器。

基本模塊包含Instruction Fetch/Decode模塊,用來進(jìn)行指令的抓取和譯碼;Base ALU模塊,是一個(gè)基本的32位的ALU;控制模塊和一些寄存器模塊,用來實(shí)現(xiàn)控制和寄存。

可重構(gòu)模塊包含Instruction/Data Memory Management and Error Protection模塊,用來實(shí)現(xiàn)對(duì)指令和數(shù)據(jù)存儲(chǔ)器尺寸、奇偶校驗(yàn)和ECC的重構(gòu);Data Load/Store模塊,用來重構(gòu)Load/Store通路的位寬以及單雙向;Base Register File模塊,可重構(gòu)Register的尺寸;Processor Interface Control模塊,可以實(shí)現(xiàn)對(duì)接口不再對(duì)系統(tǒng)總線進(jìn)行依賴,可以實(shí)現(xiàn)對(duì)interface、port和queue的重構(gòu);Write Buffer 模塊,可以實(shí)現(xiàn)對(duì)1-32個(gè)buffer的選擇;iDMA模塊,通過重構(gòu)實(shí)現(xiàn)接口直接讀取處理器的本地?cái)?shù)據(jù);還有Instruction/Data 的一些存儲(chǔ)(Cache、RAMs和ROMs)、一些寄存器(Data-Address Watch Rrgisters、Instruction-Address Watch Register)以及timer和中斷控制同樣是可充配置的。

用戶自定義模塊包含Designer-Defined Functional Units,用來實(shí)現(xiàn)基礎(chǔ)功能之外的用戶自定義的一些功能;Designer-Defined Data Load/Store Unit,可以實(shí)現(xiàn)多路的Load/Store通路,提升性能。

外部模塊包含連接在數(shù)據(jù)總線上的一些外設(shè)包括RAM、DMA、Device以及一些與端口接口相連的Memory。

2.2. Xtensa處理器的ISA

這個(gè)32位的Xtensa LX7處理器的結(jié)構(gòu)特色是有一套專門為嵌入式系統(tǒng)設(shè)計(jì)、精簡(jiǎn)而高效能的16與24位指令集。其基本結(jié)構(gòu)擁有80個(gè) RISC 指令,其中包括32位基本的ALU,6個(gè)管理特殊功能的寄存器,32或64個(gè)普通功能32位寄存器。這些32位寄存器都設(shè)有加速運(yùn)作功能的窗口。下面分別介紹一些Xtensa處理器ISA的特性。

2.2.1. 基礎(chǔ)性質(zhì)

Xtensa處理器有大量的可重構(gòu)的選項(xiàng),可以讓用戶獲取實(shí)現(xiàn)所需功能和性能的邏輯;高效能的16/24位指令集和用戶自定義的可變長(zhǎng)度指令集(長(zhǎng)度為4-16bytes的任意值)使內(nèi)存長(zhǎng)度和性能達(dá)到最佳狀態(tài);選用5-7級(jí)ISA流水來對(duì)不同的內(nèi)存進(jìn)行加速;拓展的DSP也可實(shí)現(xiàn)最高31級(jí)流水;可選擇的隊(duì)列(FIFO)、端口(GPIO)和查找接口有著幾乎無限的I/O帶寬來進(jìn)行數(shù)據(jù)的傳輸,不受系統(tǒng)帶寬的影響;可以選擇通過硬件的預(yù)取來降低內(nèi)存的延遲;自動(dòng)生成細(xì)粒度的門控時(shí)鐘可以實(shí)現(xiàn)功耗的降低;可以通過FLIX來實(shí)現(xiàn)指令的并行。

2.2.2. 兼容性

兼容性是Xtensa處理器ISA的根本,因?yàn)橹挥芯哂泻軓?qiáng)的兼容性才能很好的應(yīng)用到第三方的應(yīng)用軟件和開發(fā)工具上去。所有的可重構(gòu)、可拓展的Xtensa處理器都對(duì)主要的操作系統(tǒng)、調(diào)試工具以及輸入校驗(yàn)設(shè)備兼容。同時(shí)所有版本的處理器都向上兼容,同時(shí)用戶自定義的指令可以重復(fù)使用。

2.2.3. 拓展性

Xtensa處理器可以很方便的將指令無縫的添加到處理器的數(shù)據(jù)通路中。任何相關(guān)的C數(shù)據(jù)類型、軟件工具鏈和需要的進(jìn)行綜合的EDA腳本都是自動(dòng)生成。數(shù)據(jù)通路、相關(guān)的指令以及C數(shù)據(jù)類型都是用TIE(Tensilica Instruction Extension)語言來寫的。

2.2.4. 可重構(gòu)性

Xtensa處理器提供預(yù)驗(yàn)證的模塊,當(dāng)用戶的設(shè)計(jì)需要時(shí)隨時(shí)可以將其添加到設(shè)計(jì)中去,可以又快又好的實(shí)現(xiàn)所需設(shè)計(jì)。所有可重構(gòu)的選項(xiàng)如圖4所示。由圖可知可重構(gòu)的部分包含:在不同的應(yīng)用下選用不同的DSP (HiFi DSPs for Audio/Voice/Speech,Vision P5 and P6 DSPs for Imaging and Vision,ConnX BBE16EP, BBE32EP and BBE64EP DSPs,F(xiàn)usion F1 DSP,F(xiàn)usion G3 DSP),實(shí)現(xiàn)DSP的重構(gòu);多重自定義長(zhǎng)度的GPIO ports對(duì)外設(shè)進(jìn)行控制和監(jiān)測(cè);Queue中的接口寬度可選擇;32位乘法器與16位的乘法器和MAC;單精度/雙精度,標(biāo)量/矢量浮點(diǎn)數(shù)模塊的選擇;對(duì)于VLIW和一般的指令可以通過三路64位的FLIX實(shí)現(xiàn)交叉存取。

圖4 Xtensa LX7 處理器最大范圍的可重構(gòu)選項(xiàng)

2.2.5. 其他性能

高低字節(jié)排序的可選擇;1或2個(gè)通用的load/store unit,每個(gè)的尺寸為32-,64-,128-,256-,512-bits可選;1-32個(gè)輸入可選擇輸入buffer; 多重自定義長(zhǎng)度的接口是數(shù)據(jù)通過FIFO進(jìn)出;FLIX的長(zhǎng)度可選,最高128bits;數(shù)據(jù)和指定的Cache采用4路組相連,最大為128K,運(yùn)用write-back和write-through的cache寫入?yún)f(xié)議;可選擇的對(duì)本地內(nèi)存的奇偶校驗(yàn)和ECC。

動(dòng)態(tài)功耗和漏電流功耗較小;通過中斷控制來進(jìn)行片上調(diào)試;可選擇的16位處理器ID,支持大規(guī)模并行陣列結(jié)構(gòu);支持第三方的JTAG debug probe進(jìn)行片上調(diào)試的硬件。

3. 通過Xtensa處理器為SOC設(shè)計(jì)增加靈活性和拓展性

Cadence為Soc設(shè)計(jì)者提供可以通過軟件編程使其設(shè)計(jì)更加靈活性和長(zhǎng)壽命的解決方案,以及對(duì)于特定的應(yīng)用提供定制處理器。現(xiàn)在用戶可以通過TIE(Tensilica Instruction Extension)語言設(shè)計(jì)一款功能、指令設(shè)定可拓展原始處理器設(shè)計(jì)者從未想過的特性。

TIE語言可以描述指令、寄存器、拓展單元和I/O,然后這些會(huì)自動(dòng)生成并添加到處理器中。TIE語言與verilog類似,用來描述希望的指令、操作數(shù)、編碼和執(zhí)行語義。TIE文件是Xtensa處理器發(fā)生器的輸入文件,處理器發(fā)生器自動(dòng)的建立重構(gòu)的處理器和完整的軟件工具鏈,該軟件工具鏈包含所有的可重構(gòu)的功能和新的TIE指令。

TIE語言可以讓用戶將產(chǎn)品性能提升和創(chuàng)造其獨(dú)特性。Xtensa處理器的拓展性可以將優(yōu)化的特性添加或者應(yīng)用到任何需要優(yōu)化處理器成本、功耗、應(yīng)用性能的平臺(tái)上。

3.1. 靈活性

就像你可以從一系列預(yù)先確定的功能選項(xiàng)中選擇特定的功能來提升處理器的性能,現(xiàn)在可以創(chuàng)造可以提升標(biāo)準(zhǔn)或者自定義算法指令以及更大的帶寬的數(shù)據(jù)接口。通過使用提供的工具,應(yīng)用的熱點(diǎn)可以被定義,同時(shí)添加用來更高性能處理這些熱點(diǎn)的指令,從而不再需要提升時(shí)鐘頻率或者重寫大量的軟件。

3.2. 獨(dú)一性

對(duì)于通用處理器固化的功能,不同算法運(yùn)算可能性能會(huì)有差異。通用處理器在進(jìn)行通用計(jì)算時(shí)有優(yōu)勢(shì),但是不擅長(zhǎng)計(jì)算任何一個(gè)特定的算法。Xtensa處理器為用戶提供了通過能夠加速特定算法的硬件來區(qū)別的高性能的執(zhí)行各種算法(其思想如圖5所示)。這意味著只要用戶定義的處理器達(dá)到了在相同軟件上執(zhí)行的性能,該設(shè)計(jì)就不可能被復(fù)制。

圖5 Xtensa LX7處理器提供的添加用戶定義的功能和接口的思想

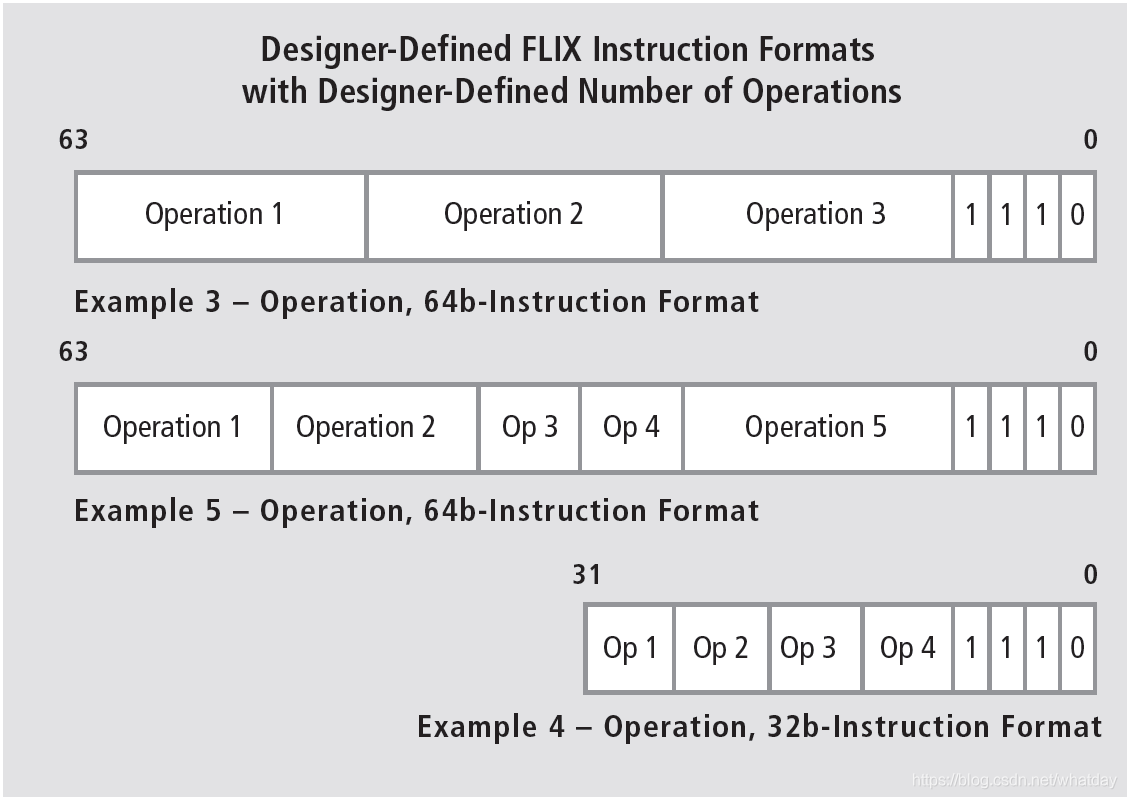

3.3. 通過FLIX進(jìn)行并行操作

由圖5可知,用戶自定義功能的實(shí)現(xiàn)是通過FLIX。FLIX結(jié)構(gòu)使得Xtensa LX7處理器稱為一個(gè)VLIW處理器,如果需要可以實(shí)現(xiàn)2-30的并行。FLIX指令的長(zhǎng)度為4bytes到16bytes之間的任意值。這種可變長(zhǎng)度的FLIX指令可以與Xtensa處理器標(biāo)準(zhǔn)的16/32 bits指令無縫混合,所以不會(huì)有模式轉(zhuǎn)換上的損失。圖6展示了用戶使用FLIX創(chuàng)造VLIW進(jìn)行2-30級(jí)的并行操作

通過FLIX(可變長(zhǎng)度指令字)Xtensa處理器可以除去在使用VLIW時(shí)指令寄存器的冗余損失。事實(shí)上,使用FLIX的Xtensa可以同時(shí)提供高性能和曉得代碼長(zhǎng)度。使用FLIX的損失是很小的,只是增加了2000個(gè)門用來進(jìn)行指令的控制和譯碼,但是帶來的好處是很大的。

Xtensa的C/C++編譯器自動(dòng)的從源代碼中提取出并行操作并將多種操作加到FLIX中,所以即使不通過額外的軟件資源同樣可以獲得并行計(jì)算好處。通過這種方法,一個(gè)three-issue的Xtensa LX7處理器在一個(gè)較低的頻率下運(yùn)行也可以達(dá)到對(duì)應(yīng)其他設(shè)備在相當(dāng)高時(shí)鐘頻率下的性能。

圖6. 用戶使用FLIX創(chuàng)造VLIW進(jìn)行2-30級(jí)的并行操作

還有關(guān)于接口的可重構(gòu)方法,以及對(duì)應(yīng)的軟件部分由同組其他成員調(diào)研,在此不做講解。

4. 總結(jié)

Xtensa 處理器的實(shí)現(xiàn)了對(duì)硬件和軟件的共同設(shè)計(jì),通過硬件重構(gòu)進(jìn)行高性能的計(jì)算,通過軟件編程進(jìn)行高效率的控制。而且Xtensa 處理器結(jié)構(gòu)技術(shù)先進(jìn)、指令精簡(jiǎn),可以幫助系統(tǒng)設(shè)計(jì)師大量縮減編碼的長(zhǎng)度,從而提高指令的密集度并降低能耗。這對(duì)于高合成的單芯片系統(tǒng) ASIC 而言,是減低成本的重要關(guān)健。

審核編輯 黃宇

-

處理器

+關(guān)注

關(guān)注

68文章

19825瀏覽量

233735 -

asic

+關(guān)注

關(guān)注

34文章

1243瀏覽量

122056

發(fā)布評(píng)論請(qǐng)先 登錄

國民技術(shù)能否開展一個(gè)M7處理器的試用活動(dòng)。

Cadence推出Tensilica NeuroEdge 130 AI協(xié)處理器

瑞芯微RK3562處理器的基本特性

自主創(chuàng)新,安全可控:申威SW831處理器與國產(chǎn)終端產(chǎn)品推薦

RK3126處理器:高效四核Cortex-A7多媒體處理平臺(tái)

RV1109處理器概述

面向NXP i.MX8處理器的電源解決方案

ADS8361與TMS470處理器的接口

ADS786x與TMS470處理器的接口

恩智浦i.MX8處理器的集成電源設(shè)計(jì)

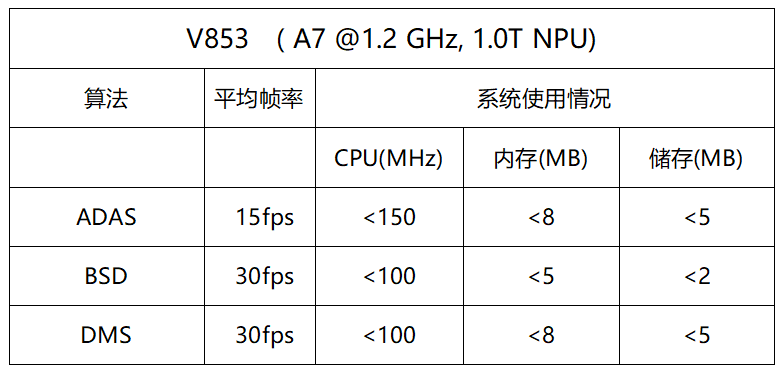

基于全志V853處理器的智能輔助駕駛算法介紹

使用TPS6521815 PMIC為NXP i.MX 7處理器供電

Tensilica處理器及Xtensa LX7處理器介紹

Tensilica處理器及Xtensa LX7處理器介紹

評(píng)論