低通FIR將基帶信號的旁瓣濾去,保留基帶信號的主瓣。基帶信號之所以是基帶信號,正是因為它處在零中頻附近。實際上,信號之所以在高頻甚至射頻的原因主要有:

1.接收天線的長度與電磁波的波長存在正比例關系,所以波長越小,接收天線也可以做的越小。電磁波波長與頻率存在反比例關系,所以需要將基帶信號上變頻至高頻部分,方便天線接收。

2.方便擴展信號帶寬,提高頻帶利用率。

本文將通過DDS IP核輸出的正弦波,與基帶信號混頻上變頻至高頻部分,將涉及一點數字信號處理內容。

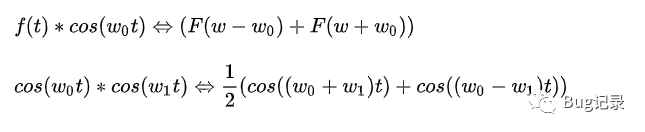

首先,簡單寫一下上變頻的數學理論基礎,

基帶信號乘以一個正弦波,頻域卷積,頻譜上會將基帶信號的頻譜搬移到正弦波的頻率。

所以,我們需要做的就是生成一個所需的正弦波,并與基帶信號相乘。這個過程就需要使用到Xilinx的DDS IP核以及DSP IP核。

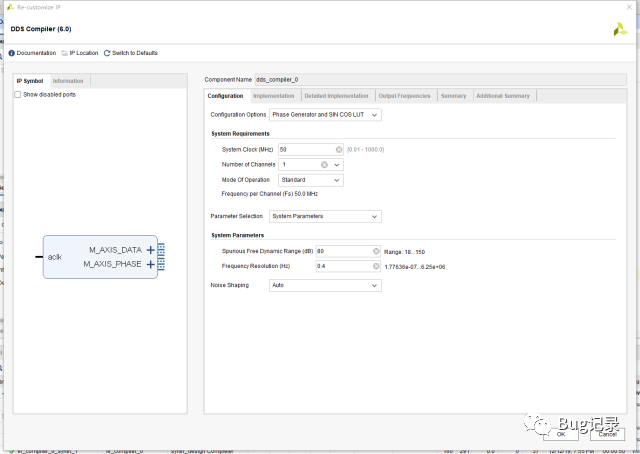

在Vivado中IP Catalog中找到DDS IP核,

DDS IP核設置

系統時鐘選擇50MHz,通選數量選擇1,其他的可以保持默認。注意Configuration Option,這里選擇Phase Generator and SIN COS LUT,這個模式會根據GUI設置自動產生所需要的頻率的正弦波;而另一種模式SIN COS LUT ONLY,會根據輸入的相位信息phase_data輸出對應的正弦波值,相位信息需要不斷地自加獲取輸出的正弦波值。兩種模式各有利弊,第一種模式設置更方便,第二種模式不需要固定輸入時鐘,可以改變參數獲取不同的頻率的正弦波。

第一種模式下,dds實例化,只需要取m_axis_data_tdata的數據即可,輸出的波形按照GUI設置的要求。

dds_compiler_0 dds_inst (

.aclk(clk_50m), // input wire aclk

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(cos_o), // output wire [15 : 0] m_axis_data_tdata 13 - 2

.m_axis_phase_tvalid(), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata() // output wire [31 : 0] m_axis_phase_tdata

);

第二種模式下,dds實例化,需要不斷地自加相位數據,DDS會根據相位數據輸出對應的正弦波值。這更像ROM表,相位數據為ROM地址,根據ROM地址輸出相應地址的數據。

always @ (posedge clk or posedge rst)beginif (rst)

phase_data <= 16'd0;

else

phase_data <= phase_data + fre_word;end

dds_compiler_0 dds_i (

.aclk(clk), // input wire aclk

.aclken(1'b1), // input wire aclken

.s_axis_phase_tvalid(1'b1), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata(phase_data), // input wire [15 : 0] s_axis_phase_tdata

.m_axis_data_tvalid(), // output wire m_axis_data_tvalid

.m_axis_data_tdata(t_data) // output wire [31 : 0] m_axis_data_tdata);

其實DDS的原理正是ROM表存儲,相位數據就是地址信息,根據地址信息查找表,輸出對應數據,FPGA擅長的正是查表。第一種模式固定了相位數據和相位差,簡化了操作但固定了使用時的輸出頻率;第二種模式開放了相位數據接口,輸出的頻率更加多變。

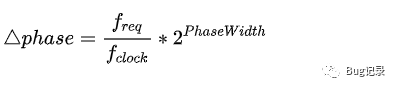

根據公式可知,

上面示例中的fre_word計算來源于這個公式。

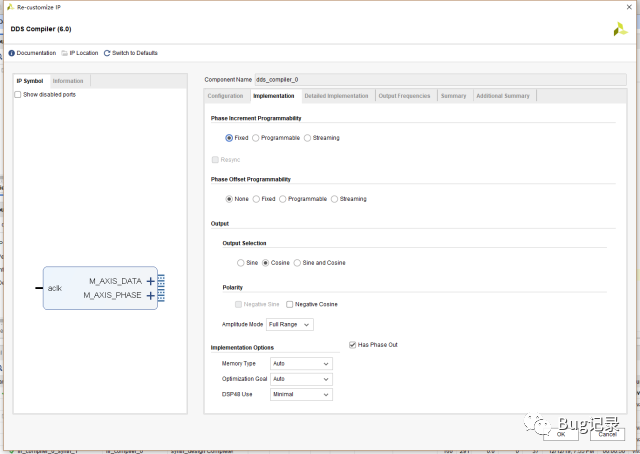

DDS IP核設置

Output Selection可以選擇輸出的波形是Sine,Cosine,Sine and Cosine。注意選擇Sine and Cosine時輸出的信號寬度是Sine,Cosine的兩倍,需要使用截位的方法將信號的前半段與后半段分開。高半段為Sine,低半段為Cosine。

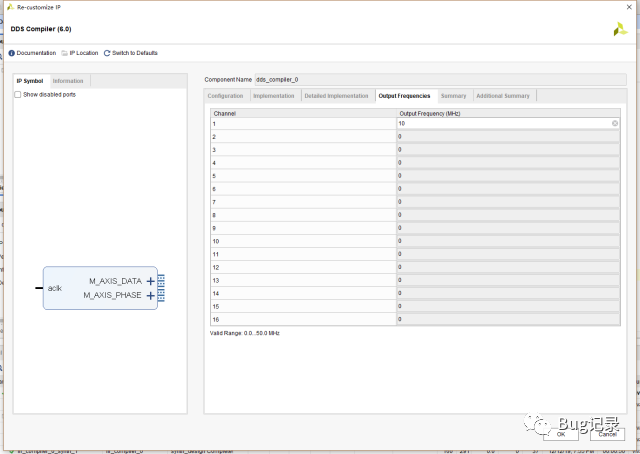

DDS IP核設置

這個部分根據需要的頻率進行設置。

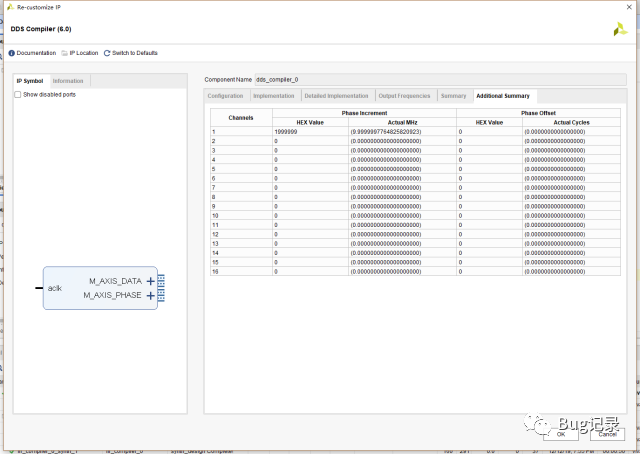

DDS IP核設置

可以看到預想10M,但由于精度的問題,實際輸出的頻率是9.9999MHz,非常接近了。

接下來就是DSP IP核的使用,在Vivado中IP Catalog中找到DDS IP核。

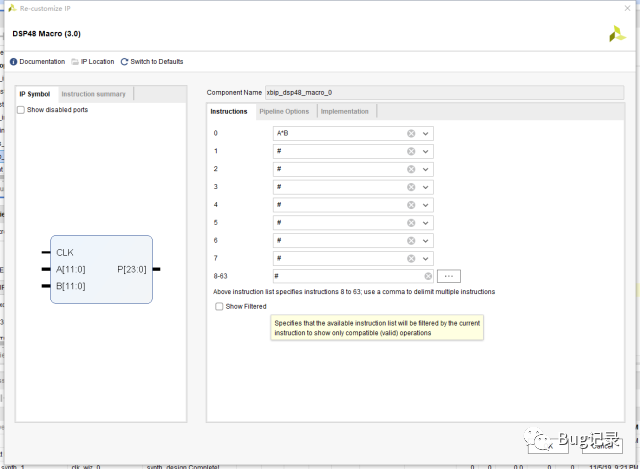

DSP IP核

使用最簡單的乘法功能,其他通道不選擇。

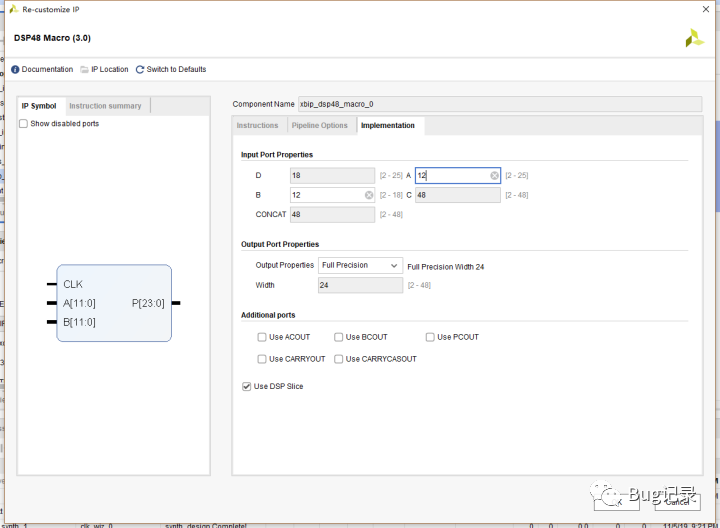

DSP IP核

設定A,B的位數以及輸出數據的位寬之后就完成了DSP IP核的設置。

xbip_dsp48_macro_0 dsp_product_inst (

.CLK(clk_50m), // input wire CLK

.A(fir_out[19:8]), // input wire [11 : 0] A

.B(cos_o[13:2]), // input wire [11 : 0] B

.P(out_data) // output wire [23 : 0] P

);

為了平衡性能與面積,所以A,B設置的12位輸入,分別對FIR和DDS的正弦波進行了截位

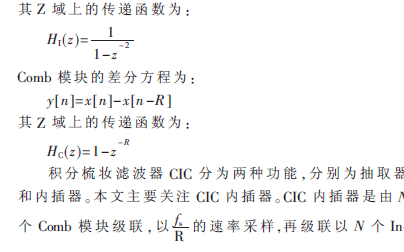

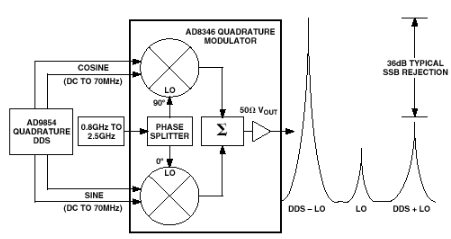

由此,就完成了基帶信號的上變頻操作;但是,這樣的上變頻會帶來雙邊帶問題,占用了2倍的基帶信號帶寬。為了解決這個問題,又可以引入IQ調制。IQ調制如何操作以及它的原理等待后續的文章梳理。

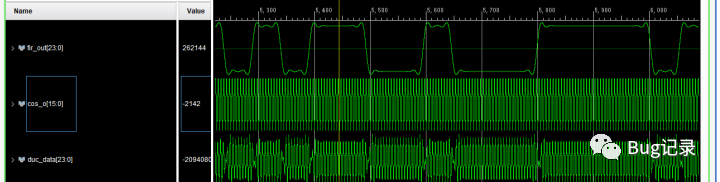

最后,上板測試可以看到如下圖所示。

實測圖

duc_data是搬移到高頻之后的信號,最后可以對duc_data進行截位操作,以適應實際中DAC的位數限制。

-

正弦波

+關注

關注

11文章

653瀏覽量

56378 -

DDS

+關注

關注

22文章

672瀏覽量

154160 -

信號處理器

+關注

關注

1文章

257瀏覽量

25699 -

電磁波

+關注

關注

21文章

1479瀏覽量

54505 -

FIR濾波

+關注

關注

0文章

6瀏覽量

9933

發布評論請先 登錄

基于數字上變頻器的中頻調制器

AD9789基帶數字上變頻頻率為什么能到Fdac/16?

在DAC3482中,采用片內混頻器實現上變頻功能需要保證兩路輸入信號的正交性嗎?

有關AD9361的上變頻

AD9789基帶數字上變頻頻率為什么能到Fdac/16

多天線多載波數字上下變頻的FPGA實現方法有哪些?

PXI 5610實現上變頻信號發送

AD9739上變頻功能實現原理是什么?

基于QDUC的雷達上變頻電路的設計

通信系統中數字上變頻技術的研究與設計

基于FPGA的高效靈活數字上變頻實現設計

正交DDS信號至800至2500MHz頻段的單邊帶上變頻

使用DDS將基帶信號上變頻

使用DDS將基帶信號上變頻

評論