前 言

近年來,隨著中國新基建、中國制造2025的持續推進,單ARM處理器越來越難勝任工業現場的功能要求,特別是能源電力、工業控制、智慧醫療等行業通常需要ARM+FPGA架構的處理器平臺來實現特定的功能,例如多路/高速AD采集、多路網口、多路串口、多路/高速并行DI/DO、高速數據并行處理等。

那么我們先來看看ARM+FPGA架構有什么優勢?ARM:接口資源豐富、功耗低,擅長多媒體顯示、邏輯控制等。FPGA:擅長多通道或高速AD采集、接口拓展、高速信號傳輸、高速數據并行處理等。

因此,ARM+FPGA架構能帶來性能、成本、功耗等綜合比較優勢,ARM與FPGA既可各司其職,各自發揮原本架構的獨特優勢,亦可相互協作處理更復雜的問題。

對于成本不敏感且通信速率要求的較高分立式ARM+FPGA場合,一般使用PCIe通信接口。但對成本敏感的分立式ARM+FPGA場合,PCIe通信接口則令FPGA芯片成本高居不下。

對于能源電力、工業控制等眾多工業領域,真正需要的是性能與成本均具有競爭力的方案,既要求能做到ARM與FPGA的高速通信,又要做到成本最優,并且最好能基于國產方案。

在這種需求背景下,創龍科技提供了基于國產ARM與低成本FPGA高速通信的3種方案。

* 硬件平臺介紹(全志科技T3/A40i)

創龍科技TLT3-EVM/TLA40i-EVM是一款基于全志科技T3/A40i處理器設計的4核ARM Cortex-A7國產工業評估板,每核主頻高達1.2GHz,由核心板和評估底板組成。T3與A40i兩者pin to pin兼容。

評估板接口資源豐富,引出雙路網口、雙路CAN、雙路USB、雙路RS485等通信接口,板載Bluetooth、WIFI、4G(選配)模塊,同時引出MIPI LCD、LVDS LCD、TFT LCD、HDMI OUT、CVBS OUT、CAMERA、LINE IN、H/P OUT等音視頻多媒體接口,支持雙屏異顯、Mali400 MP2 GPU,1080P@45fps H.264視頻硬件編碼、1080P@60fps H.264視頻硬件解碼,并支持SATA大容量存儲接口。

核心板采用100%國產元器件方案,并經過專業的PCB Layout和高低溫測試驗證,穩定可靠,可滿足各種工業應用環境。評估底板大部分元器件均采用國產方案,方便用戶快速進行產品方案評估與技術預研。

*官方商城選購入口:https://tronlong.tmall.com

本文主要介紹全志科技T3/A40i與紫光同創PGL25G/Xilinx Spartan-6基于SPI、SDIO、CSI的3種高速通信方案,最高通信速率可達到55.1MB/s。

為了簡化描述,正文僅摘錄方案功能描述與測試結果,詳細開發文檔請掃描文末二維碼下載。

備注:目前,創龍科技已推出T3/A40i+PGL25G全國產一體化工業核心板方案,國產化率100%(連接器亦為國產),歡迎咨詢。

圖 3 T3/A40i+PGL25G全國產工業核心板(國產化率100%)

1 spi_rw案例

1.1 案例說明

案例功能:主要演示T3/A40i(ARM Cortex-A7)與PGL25G/Spartan-6(FPGA)處理器之間的SPI通信。

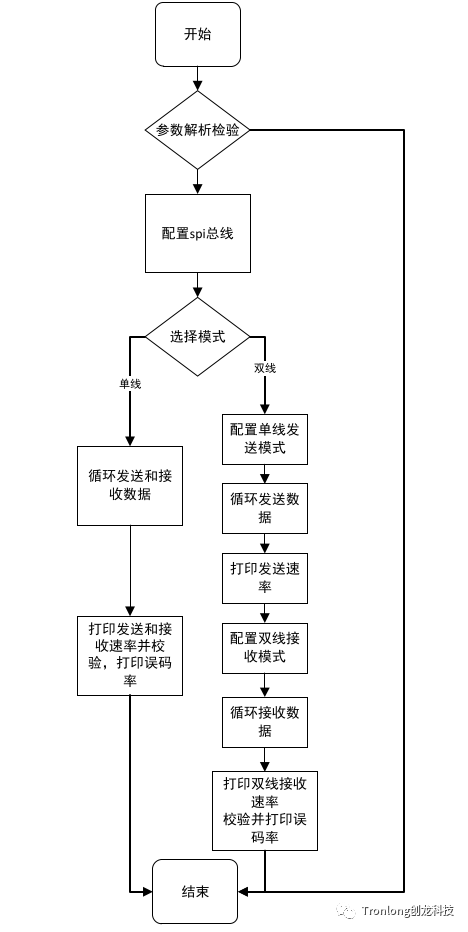

ARM端實現SPI Master功能a.打開SPI設備節點,如:/dev/spidev0.0。b.使用ioctl配置SPI總線,如SPI總線極性和相位、通信速率、數據字長度等。c.選擇模式為單線模式或雙線模式。當SPI總線為雙線模式時,發送數據是單線模式,接收數據是雙線模式。d.發送數據至SPI總線,并從SPI總線讀取數據。(備注:如單次傳輸數據大于64Byte,驅動程序將會自動啟用DMA傳輸功能。)e.打印發送和接收速率。f.校驗讀寫數據,然后打印誤碼率。

FPGA端實現SPI Slave功能a.FPGA將SPI Master發送的2KByte數據保存至BRAM。b.SPI Master發起讀數據時,FPGA從BRAM讀取2KByte通過SPI總線傳輸給SPI Master。c.當SPI總線為雙線模式,接收數據支持雙線模式,而發送數據不支持雙線模式。

圖 4ARM端程序流程圖

測試結果(1)SPI單線模式根據官方數據手冊,SPI總線通信時鐘頻率理論值最大為100MHz。本次測試指定SPI總線通信時鐘頻率為最大值100MHz,則SPI單線模式理論速率為:(100000000/1024/1024/8)MB/s ≈ 11.92MB/s。實測SPI單線模式寫速率為:10.924MB/s,SPI單線模式讀速率為:10.924MB/s。

(2)SPI雙線模式根據官方數據手冊,SPI總線通信時鐘頻率理論值最大為100MHz。本次測試指定SPI總線通信時鐘頻率為最大值100MHz,則SPI單線模式理論速率為:(100000000/1024/1024/8)MB/s ≈ 11.92MB/s;則SPI雙線模式理論速率為:(100000000/1024/1024/4)MB/s ≈ 23.84MB/s。本次實測SPI單線模式寫速率為11.631MB/s,SPI雙線模式讀速率為17.807MB/s。

2rt_spi_rw案例

2.1案例說明案例功能:基于Linux-RT系統,演示T3/A40i(ARM Cortex-A7)與PGL25G/Spartan-6(FPGA)處理器之間的SPI通信(單線模式)。

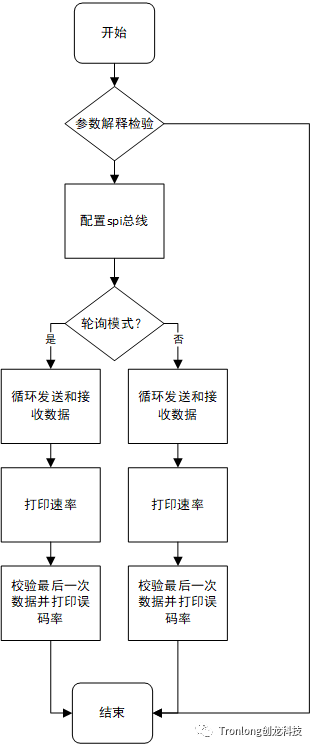

ARM端實現SPI Master功能a.打開SPI設備節點。如:/dev/spidev0.0。b.使用ioctl配置SPI總線。如SPI總線極性和相位、通信速率、數據字長度等。c.創建實時線程。d.發送數據至SPI總線,以及從SPI總線讀取數據。e.打印發送、接收的速率和傳輸耗時。f.校驗讀寫數據,然后打印誤碼率。

FPGA端實現SPI Slave功能a.FPGA將SPI Master發送的2KByte數據保存至BRAM。b.SPI Master發起讀數據時,FPGA從BRAM讀取2KByte通過SPI總線傳輸給SPI Master。

圖 5ARM端程序流程圖

測試結果(1)非輪詢方式根據官方數據手冊可知,SPI總線通信時鐘頻率理論值最大為100MHz。本次測試指定SPI總線通信時鐘頻率為最大值100MHz,則理論速率為:(100000000/1024/1024/8)MB/s ≈ 11.92MB/s。實測傳輸4Byte數據的最小耗時為49us,最大耗時為662us,平均耗時為227us;寫速率為0.017MB/s,讀速率為0.017MB/s。

(2)輪詢方式根據官方數據手冊可知,SPI總線通信時鐘頻率理論值最大為100MHz。本次測試指定SPI總線通信時鐘頻率為最大值100MHz,則理論速率為:(100000000/1024/1024/8)MB/s ≈ 11.92MB/s。實測傳輸4Byte數據的最小耗時為14us,最大耗時為59us,平均耗時為14us;寫速率為0.239MB/s,讀速率為0.239MB/s。

3sdio_test案例

3.1案例說明案例功能:演示T3/A40i(ARM Cortex-A7)與PGL25G/Spartan-6(FPGA)處理器之間的SDIO通信。

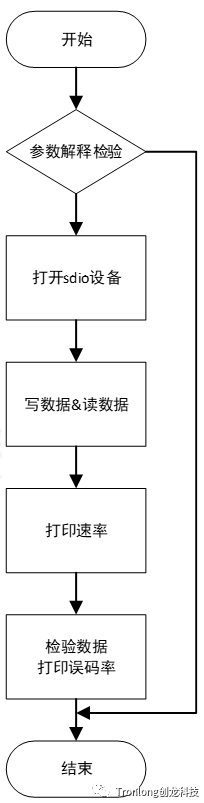

ARM端實現SDIO Master功能a.打開SDIO設備節點,如:/dev/generic_sdio0。b.發送數據至SDIO總線,以及從SDIO總線讀取數據。c.打印發送和接收速率。d.校驗讀寫數據,然后打印誤碼率。

FPGA端實現SDIO Slave功能a.FPGA將SDIO Master發送的2KByte數據保存至BRAM。b.SDIO Master發起讀數據時,FPGA從BRAM讀取2KByte通過SDIO總線傳輸給SDIO Master。

圖6ARM端程序流程圖

測試結果本次測試指定SDIO總線通信時鐘頻率為25MHz(最高50MHz),則理論通信速率為:(25 x 4 / 8)MB/s = 12.5MB/s。實測寫速率為5.113MB/s,讀速率為5.440MB/s,誤碼率為0.0%。

4csi_test案例

4.1案例說明案例功能:演示T3/A40i(ARM Cortex-A7)與PGL25G/Spartan-6(FPGA)處理器之間的CSI通信案例。

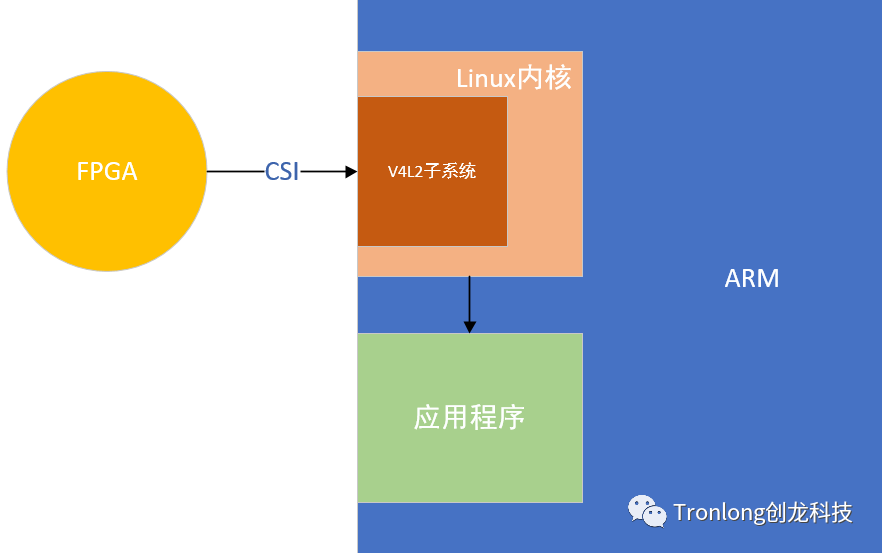

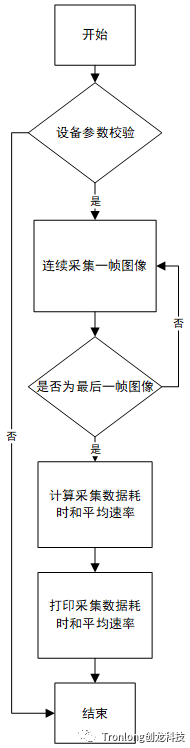

ARM端功能a)基于Linux子系統V4L2。b)通過CSI總線,采集指定幀數數據。c)計算總耗時。d)打印平均采集速率,并校驗最后一幀圖像的數據。

FPGA端功能a)將測試數據(0x00 ~ 0xFF)寫入FIFO。b)從FIFO讀出數據,按行與幀的方式、1024 x 512的分辨率,通過CSI總線發送至ARM端。使用的CSI總線為CSI0,最高支持分辨率為1080P30,數據位寬為8bit。功能框圖與程序流程圖,如下圖所示。

圖 7功能框圖

圖 8ARM端程序流程圖

測試結果FPGA端將CSI_PCLK設置為65MHz,測試數據寫入FIFO的時鐘FIFO_WR_CLK設置為59MHz。由于FPGA端需將數據寫入FIFO再從FIFO讀出后發送,每一行與每一幀之間的間隔時間會受FIFO寫入的速率影響,因此CSI通信的實際理論傳輸帶寬應為:(59MHz x 8bit / 8)MB/s = 59MB/s。實測傳輸速率為55.1MB/s,誤碼率為0.0%

-

ARM

+關注

關注

134文章

9270瀏覽量

373433 -

嵌入式

+關注

關注

5125文章

19438瀏覽量

312992 -

核心板

+關注

關注

5文章

1083瀏覽量

30504

發布評論請先 登錄

相關推薦

國產ARM與低成本FPGA高速通信的3種方案,基于全志T3/A40i!

國產ARM與低成本FPGA高速通信的3種方案,基于全志T3/A40i!

評論