半導體產業本就是一個下游應用需求拉動的市場。化。

數智化是推動未來經濟發展的重要引擎,新能源汽車的暴漲給汽車芯片帶來了旺盛的需求。兩大風口加持下,也給作為半導體行業底層科技的EDA帶來各種變化。在這新春伊始,我們將重點談談,由此帶來的芯片開發將面臨的多重驗證挑戰。

No.1

兩大未來風口:

數智化+汽車芯片

利用大數據、云計算、物聯網、AI、5G及自動駕駛等新技術的運用,使得企業整個組織系統和業務鏈迅速升級,更助推著各細分領域頭部的整合。而芯片又為其提供著底層技術的支持。不知不覺,芯片-終端-軟件,整個半導體行業已經進入了應用定義硬件的時代。

AI應用不斷激增、異構計算需求旺盛,基于智能多元化應用產生的海量數據,無疑推動市場對算力的需求。高性能計算和通信、數據存儲等領域逐漸成為下一代風口。

此外,2022年的缺芯危機曾引來一波“投資”高潮。如今潮水褪去,支撐起未來半導體的卻是汽車芯片。新能源汽車近年來發展勢不可擋,層層剝繭之下,汽車賽道的下半場是智能化的征途,本質還是芯片算力的群雄逐鹿。高算力、高帶寬、多核異構的高性能芯片是未來發展的關鍵,也是決定智能汽車的性能和表現的核心,這也更進一步推動了高性能芯片需求的快速增長。

數智化和汽車芯片,無疑是未來經濟增長的兩大風口,也是未來半導體產業發展增長的新方向。

No.2

多重驗證挑戰

應對這兩大風口,半導體產業下游倒逼中游,中游推動上游。無論是支撐高算力的智能芯片,還是適用于汽車的多核異構的高性能芯片,芯片的設計開發,及其支撐技術也因此迎來新的改變,更面臨著多重驗證挑戰。縱觀整個芯片開發流程,重中之重的是芯片前期的設計與驗證。因為通常芯片驗證在整個研發項目進度中占據過半,并且決定了芯片的成敗。以研發一顆GPU SoC為例,大約70%的投入都是在數字前端設計。首先,隨著芯片設計成本日益高漲,以及算力與儲存需求爆發式增長,系統級芯片驗證變得極其復雜,先進SoC的驗證壓力也呈指數及增長。工程師們所需要的驗證工具早已不僅僅局限在滿足功能驗證需求,更多需要從設計、架構、軟硬協同、功耗等方面優化探索。

“造芯的第一步是選對芯片架構。”思爾芯總裁林鎧鵬表示,“但數智化推動市場快速變化,新技術的到來讓應用更多元化,這也讓IC設計公司很難根據芯片未來的使用場景明確芯片定位。為了適應其變化,工程師們需要更靈活的架構探索,以及更多重的驗證手段。”

例如在現流行的異構集成中,會通過異構計算整合不同架構的運算單元來進行并行計算,這也已經成為當前解決算力瓶頸的重要方式之一。它的出現讓整個設計驗證流程發生了根本性變化,異構驗證是如今的工程師們所期待的新方法。

因為不同的運算單元有不同的架構設計,對信息流也有不同的處理方式,這些都需要針對其特性使用不同驗證的方法學。在驗證的難度越來越大的今天,單一工具并不能保證設計的可靠性。

此外,EDA服務云計算技術迭代的同時,云計算也在反哺EDA。特別是芯片設計變得愈發復雜之后,算力和存儲這兩塊開始出現了瓶頸,傳統的自建數據中心已不堪重負。如何幫助IC設計企業獲得算力的充沛及彈性供給,減少IT基礎設施,還能獲得更多的EDA工具,以及IP相關資源的整合,大幅降低時間與成本,也是如今芯片設計驗證面臨的挑戰。

No.3

異構驗證平臺

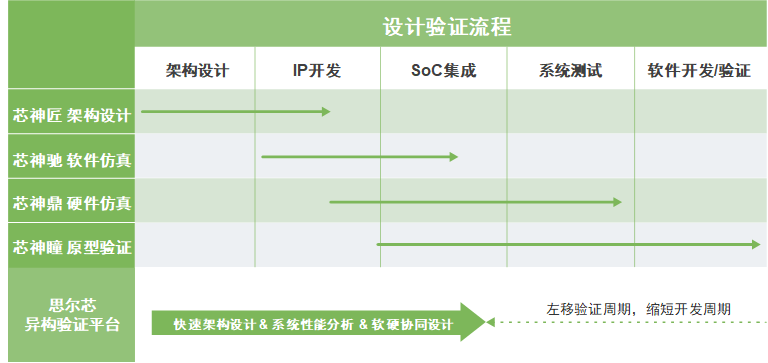

如何應對新風口下的多重驗證挑戰?思爾芯,這家國產原型驗證的龍頭企業,最近并購和自研不斷,為高算力、多核異構的高性能芯片的驗證挑戰提供了高效的解決方案。思爾芯董事長兼CEO林俊雄表示,“在芯片設計的不同節點,工程師所用的工具是不一樣的。當前思爾芯已有豐富的產品線,覆蓋驗證云服務、架構設計、軟件仿真、硬件仿真、原型驗證等工具。廣泛應用于物聯網、云計算、5G通信、智慧醫療、汽車電子等終端領域。我們的異構驗證方法學,在研究怎樣降低驗證工程復雜度的同時,還能保證驗證的可靠性,提升驗證效率。”重捋一下芯片設計的流程,思爾芯的驗證工具是如何覆蓋整個芯片設計驗證的全流程?

需求分析與架構設計

芯片設計的起點都是需求分析。在一顆芯片的設計之初,思爾芯的Genesis芯神匠架構設計軟件就可以給工程師提供一個建模,分析,仿真和軟硬件協作的平臺,利用建模方法學實現電子系統級(Electronic System Level,ESL)設計流程,可用于開發半導體、航空和電子系統產品。通過該方案可創建周期精度的模型以便進行早期性能和功耗分析,也可進行時序和功耗的仿真,還能搭配芯神瞳原型驗證平臺提前進行軟硬件協同設計。

面對龐雜的代碼,工程師想要確保設計可靠性,這就需要對設計進行驗證,即功能驗證。軟件仿真、硬件仿真和原型驗證等方法學基本覆蓋了整個功能驗證方法,工程師們針對不同階段需結合使用不同驗證的方法學。

軟件仿真

軟件仿真適合小型設計和模塊級仿真。其實從早期的需求分析與架構探索就可以使用,還可以覆蓋功能驗證中的RTL級仿真、超大容量硬件仿真加速器、快速原型系統等多個應用場景。可以說是每個驗證工程師常規必備的EDA工具。

PegaSim 芯神馳是思爾芯近日推出的一款高性能、多語言混合的商用數字軟件仿真工具,已得到多家海內外廠商驗證。其采用了創新的架構算法,實現了高性能的仿真和約束求解器引擎,對System Verilog語言、Verilog 語言、VHDL語言和UVM方法學等提供了廣泛的支持,同時支持時序反標和門級后仿真,并可提供功能覆蓋率、代碼覆蓋率分析等功能。同時創新的軟件架構允許仿真器支持不同的處理器架構—— x86-64、RISC-V、ARM等。

此款商用數字軟件仿真工具采用創新的商業模式,可以很好地滿足企業多樣化的需求,幫助企業解決license使用緊張、算力不足、license被設計工程師長期占用等問題。真正為企業做到降本增效,加速芯片設計,確保整個芯片設計流程對需求規格的完整實現,以及項目按照預期的驗證計劃高效地推進。

硬件仿真

硬件仿真是對完整的SoC設計進行加速仿真并調試,包括SoC設計的系統級功能驗證、IP設計驗證,多應用于設計前期的RTL功能驗證。與原型驗證系統相比,最大的優點就是其強大的調試能力,可以檢查出有沒有深度錯誤或性能瓶頸。

OmniArk 芯神鼎是近日思爾芯通過并購整合推出的一款企業級硬件仿真系統。其采用超大規模可擴展商用陣列架構設計,最大設計規模可達20億門,滿足從IP級到系統級的功能驗證。基于創新的全自動編譯流程、高效調試糾錯能力、豐富的仿真驗證模式,以及千倍以上的仿真加速,讓這款企業級硬件仿真系統成為思爾芯開啟EDA驗證新時代的重磅產品。

原型驗證

原型驗證通過將RTL移植到現場可編程門陣列來驗證芯片功能。它會幫助工程師在芯片設計過程中搭建軟硬件一體的系統驗證環境,多用于SoC設計后期的系統級功能和性能驗證。在流片前工程師們就可以在SoC的基本功能驗證通過后,立刻開始驅動和應用軟件開發。甚至可以在流片前就給有需求的客戶進行芯片演示,進行預售。而且縮短了整個驗證周期,加速了產品上市時間。

思爾芯的Prodigy 芯神瞳原型驗證解決方案是業內領先的數字集成電路前端驗證解決方案,幫助全球頂尖的芯片企業開發IC和驗證,適用于驗證專門應用的集成電路(ASIC)和片上系統(SoC)的系統級功能和性能驗證。還可以幫助芯片開發者提早進行嵌入式軟件開發及軟硬件協同設計,從而加快芯片產品上市速度,搶占市場先機。該解決方案包含原型驗證硬件、自動原型編譯軟件、深度調試套件、協同仿真套件、云管理軟件以及外置應用庫。多組合方案能夠為開發者提供多種容量范圍,并覆蓋各類ASIC以及SoC設計的驗證需求。

驗證云服務

思爾芯還推出了驗證云服務,主要用于超大規模數字集成電路前端功能驗證,包括架構探索、算法驗證、IP/模塊級驗證、芯片級驗證、固件驗證、軟件驗證以及兼容性測試等。通過將驗證算力資源的云端虛擬化,實現算力管理、集群管理、多用戶管理、虛機/容器資源管理等一系列功能。

在數智化驅動半導體行業快速發展的同時,作為支撐起數字經濟的底座科技EDA也在悄然發生改變。在新的一年里,想要大展宏圖的芯片開發也正積極應對以上挑戰。無論是拓展到更多的領域,還是前瞻未來更多創新領域,思爾芯始終著眼于未來,不斷激發研發人員的創新活力,快速響應市場變化,用成熟穩定的產品服務于每一個客戶。相信不久的未來,因為有更多像思爾芯這樣的活力領軍企業,將有一個更好的生態,更輝煌的未來。

//

關于思爾芯S2C

思爾芯(S2C)自2004年設立上海總部以來始終專注于集成電路EDA領域。作為業內知名的EDA解決方案專家,公司業務聚焦于數字芯片的前端驗證,已覆蓋驗證云服務、架構設計、軟件仿真、硬件仿真、原型驗證等工具。已與超過600家國內外企業建立了良好的合作關系,服務于人工智能、超級計算、圖像處理、數據存儲、信號處理等數字電路設計功能的實現,廣泛應用于物聯網、云計算、5G通信、智慧醫療、汽車電子等終端領域。

公司總部位于上海,并建立了全球化的技術研發與市場服務網絡,在北京、深圳、西安、香港、東京、首爾及圣何塞等地均設有分支機構或辦事處。

思爾芯在EDA領域的技術實力受到了業界的廣泛認可,通過多年耕耘,已在原型驗證領域構筑了技術與市場的雙領先優勢。并參與了我國EDA團體標準的制定,承擔了多項國家及地方重大科研項目。

-

芯片

+關注

關注

459文章

52253瀏覽量

436956 -

eda

+關注

關注

71文章

2901瀏覽量

176626

發布評論請先 登錄

AI?時代來襲,手機芯片面臨哪些新挑戰?

智慧路燈的推廣面臨哪些挑戰?

【創無限 智未來】南京大展儀器的新品DZDR-AS導熱系數測定儀發布會

全面剖析倒裝芯片封裝技術的內在機制、特性優勢、面臨的挑戰及未來走向

EDA2俠客島難題挑戰·2025已正式開啟

蘋果無邊框OLED iPhone開發面臨挑戰

AMD MI300X AI芯片面臨挑戰

7納米工藝面臨的各種挑戰與解決方案

解決驗證“最后一公里”的挑戰:芯神覺Claryti如何助力提升調試效率

大算力芯片面臨的技術挑戰和解決策略

康謀分享 | 在基于場景的AD/ADAS驗證過程中,識別挑戰性場景!

大展宏兔的芯片開發又將面臨哪些驗證挑戰?

大展宏兔的芯片開發又將面臨哪些驗證挑戰?

評論