本文將幫助您了解比較器IC數(shù)據(jù)手冊(cè)中常見的一些關(guān)鍵比較器參數(shù)或規(guī)格。

您在比較器的數(shù)據(jù)表中可能遇到的一些主要參數(shù)是:

傳播延遲

電流消耗

輸出級(jí)類型(集電極開路/漏極或推挽式)

輸入失調(diào)電壓、遲滯

輸出電流能力

上升和下降時(shí)間

輸入共模電壓范圍

除此之外,您還可以找到其他參數(shù),例如:輸入偏置電流、共模和電源抑制比、采樣/保持功能和啟動(dòng)時(shí)間。

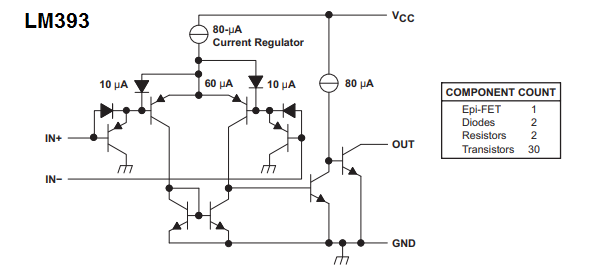

大多數(shù)情況下,單個(gè)比較器芯片將有 5 個(gè)引腳:幾個(gè)引腳用于電源輸入 VCC+、VCC-,兩個(gè)引腳用于饋送輸入信號(hào) IN+、IN-

和一個(gè)輸出輸出引腳。在某些IC中,可能有一個(gè)額外的引腳用于待機(jī)功能。

從我們之前的討論中我們知道,當(dāng)VIN(+)》VIN(-)時(shí),輸出處于高電平狀態(tài),如果VIN(+)《VIN(-),則輸出處于低電平狀態(tài)。

換句話說,當(dāng)同相輸入(+)的電壓水平高于反相輸入(-)時(shí),計(jì)算機(jī)內(nèi)部的輸出晶體管將被關(guān)閉。

這意味著其集電極引腳將顯示開路條件。由于該集電極引腳應(yīng)通過上拉電阻與正電源軌連接,因此在這種情況下允許集電極具有正或高邏輯輸出。

輸出級(jí)類型(集電極開路/漏極或推挽式)

關(guān)于輸出引腳配置,比較器有兩種類型:推挽式和集電極開路(漏極開路)。

在推挽式配置中,負(fù)載可以直接連接在電容器的集電極引腳和正極線之間,從而允許負(fù)載根據(jù)輸入信號(hào)條件打開/關(guān)閉。這就像推挽式開關(guān),因此得名。

或者,集電極引腳可以通過上拉電阻與正電源軌連接,然后集電極輸出可用作推挽邏輯輸出。一種

os這種配置的優(yōu)點(diǎn)是它允許與比較器的Vcc不同的電壓電平用于負(fù)載。

在集電極開路模式下,比較器只能吸收電流,但不能向負(fù)載提供電流。由于其范圍有限,該模式很少使用,盡管它允許在指定應(yīng)用的OR門模式下連接多個(gè)輸出。

比較器數(shù)據(jù)表參數(shù)

輸入共模電壓范圍 - VICM :

輸入共模電壓范圍是電壓的量度,該電壓在計(jì)算機(jī)可接受的輸入范圍內(nèi)。

這是一個(gè)電壓范圍,在該范圍內(nèi),計(jì)算機(jī)的兩個(gè)輸入都強(qiáng)制用于確保配置的功能。

在這種模式下,輸入在其輸入引腳上采用完整的Vcc至0V電源范圍工作,因此也稱為軌到軌輸入級(jí)。

但是,除非必要,否則建議避免使用軌到軌共模輸入范圍,以最大限度地降低器件的功耗。

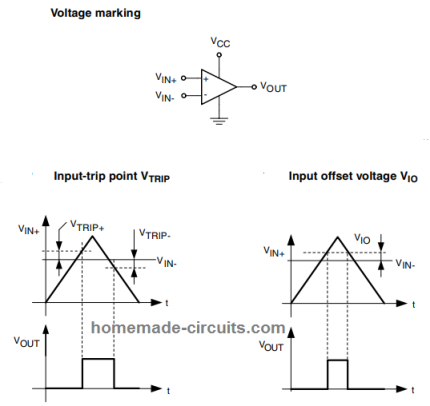

輸入失調(diào)電壓 - VIO (VTRIP)

VIO

參數(shù)是最小輸入差值,可能即將導(dǎo)致輸出切換其狀態(tài)。輸入端的輸入失調(diào)電壓差分電平會(huì)影響比較器的分辨率,因?yàn)樵摬罘址瓤赡芊浅P。?dǎo)致輸出切換狀態(tài)不穩(wěn)定。因此,這種小的偏移信號(hào)可能會(huì)導(dǎo)致輸出行為異常或根本不切換。

低差分可能導(dǎo)致比較器晶體管變得不穩(wěn)定,從而導(dǎo)致輸入失調(diào)電壓條件的增加增加。

對(duì)于啟用了內(nèi)部遲滯的組件,VIO 定義為 VTRIP+ 和 VTRIP- 之和的平均值,VHYST = VTRIP+ - VTRIP- 的遲滯值,其中

VTRIP+ 和 VTRIP- 構(gòu)成輸入差分電壓,分別導(dǎo)致輸出從低狀態(tài)切換到高狀態(tài)或高狀態(tài)切換到低狀態(tài)。

CMRR 和 SVR

CMRR代表共模電壓抑制比,提供輸入失調(diào)電壓VIO和輸入共模電壓VICM之間的關(guān)系。這可以理解為共模電壓值與輸入失調(diào)電壓的比率。此參數(shù)通常以對(duì)數(shù)刻度表示為:

CMRR [dB] = 20 ? log (| ΔVICM /ΔVIO| )

CMRR是通過測(cè)量?jī)煞N不同輸入共模電壓(通常為0 V和VCC)的兩個(gè)輸入失調(diào)電壓幅度來計(jì)算的。

術(shù)語SVR代表“電源電壓抑制”,定義為提供輸入失調(diào)電壓VIO與電源電壓之間關(guān)系的參數(shù)。

改變電源電壓能夠在一定程度上影響輸入差分晶體管對(duì)的偏置。這意味著這種變化還可能導(dǎo)致輸入失調(diào)電壓略有變化。

這通過以下公式表示:

SVR [dB] = 20 ? log (| ΔVCC /ΔVIO| )

電壓增益

該參數(shù)有助于我們了解比較器的凈增益。當(dāng)比較器具有更高的增益規(guī)格時(shí),這意味著器件對(duì)小輸入信號(hào)差分的響應(yīng)得到改善。

通常,一臺(tái)公司的AVD范圍可以是200V/mV(106dB)。理論上,當(dāng)200mV輸入放大1dB時(shí),可實(shí)現(xiàn)106V的幅度。但是,對(duì)于實(shí)際設(shè)備,峰值電平擺幅將受到Vcc值的限制。

請(qǐng)注意,AVD 永遠(yuǎn)不會(huì)對(duì)外部遲滯產(chǎn)生任何影響,因?yàn)檩敵鰧⑻幱诟唠娖交虻碗娖綘顟B(tài),并且永遠(yuǎn)不會(huì)介于兩者之間。

傳播延遲

TPD定義為輸入信號(hào)剛好越過參考輸入電平的時(shí)刻與輸出狀態(tài)剛剛改變狀態(tài)的時(shí)刻之間的時(shí)間差。

從我們之前的討論中我們知道,補(bǔ)償器的輸出會(huì)根據(jù)輸入引腳電壓差而切換。

傳播延遲 TPD 為我們提供了規(guī)范,該規(guī)范表明輸入引腳能夠以多快的速度檢測(cè)差異并毫無問題地切換輸出。

基本上,TPD告訴我們比較器可以輕松處理的輸入頻率電平,以產(chǎn)生有效的輸出響應(yīng)。

磁滯現(xiàn)象

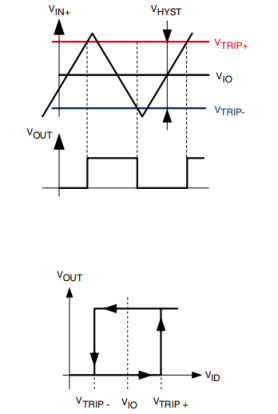

我們知道,遲滯是一個(gè)參數(shù),它禁止輸出快速變化以響應(yīng)不穩(wěn)定或波動(dòng)的輸入。

通常,在比較器中,當(dāng)輸入差分信號(hào)懸停在基準(zhǔn)值附近時(shí),輸出電壓會(huì)快速振蕩或波動(dòng)。或者,當(dāng)輸入信號(hào)的幅度非常低時(shí),可能會(huì)發(fā)生這種情況,從而導(dǎo)致輸入差分電平快速變化。

內(nèi)置遲滯

實(shí)際上,有許多比較器器件具有內(nèi)置遲滯功能。這可能在幾mV左右,這足以抑制不需要的輸出切換,而不會(huì)影響器件分辨率。

對(duì)于此類器件,評(píng)估的平均電壓上限和下限稱為輸入失調(diào)電壓VIO,VTRIP+/VTRIP-差值稱為遲滯電壓或VHYST。

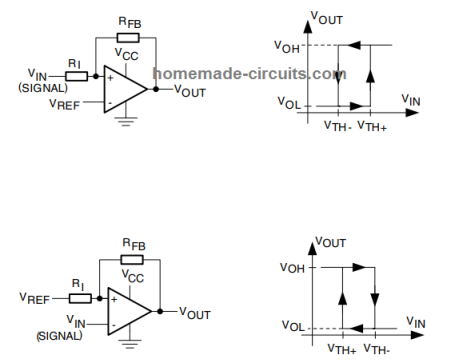

外部滯后

如果比較器沒有內(nèi)置遲滯,或者預(yù)期的遲滯水平相對(duì)較大,則可以添加外部配置,通過正反饋網(wǎng)絡(luò)實(shí)現(xiàn)遲滯功能,如下所示。

總結(jié)

-

比較器

+關(guān)注

關(guān)注

14文章

1839瀏覽量

108398 -

數(shù)據(jù)手冊(cè)

+關(guān)注

關(guān)注

95文章

6204瀏覽量

43419

發(fā)布評(píng)論請(qǐng)先 登錄

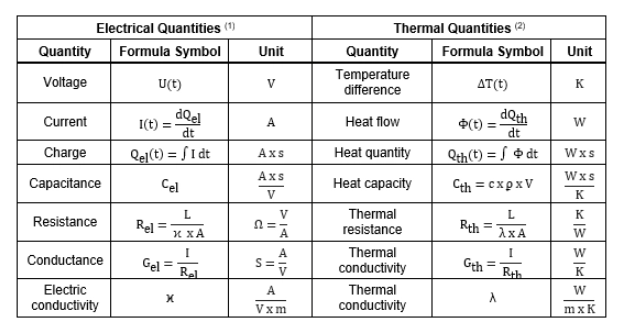

熱參數(shù)如何與PCB溫度或IC結(jié)溫進(jìn)行比較

怎樣讀懂ADC的技術(shù)手冊(cè),哪些參數(shù)比較關(guān)鍵?

#讀懂MOSFET數(shù)據(jù)手冊(cè) 理解MOSFET數(shù)據(jù)手冊(cè)中的雪崩能量等級(jí)

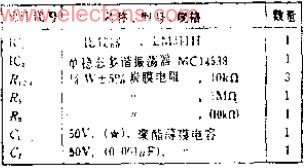

關(guān)于比較器波形問題

電源IC技術(shù)規(guī)格的解讀方法:部件選定

開關(guān)穩(wěn)壓器的基礎(chǔ):重要特性之IC的規(guī)格

關(guān)于芯片數(shù)據(jù)手冊(cè)參數(shù)理解的問題

AD53033:?jiǎn)涡酒?b class='flag-5'>數(shù)據(jù)手冊(cè)中的高性能驅(qū)動(dòng)器/比較器

比較器IC數(shù)據(jù)手冊(cè)中的參數(shù)和規(guī)格

比較器IC數(shù)據(jù)手冊(cè)中的參數(shù)和規(guī)格

評(píng)論