AXI4:高性能內(nèi)存映射需求(如讀寫DDR、使用BRAM控制器讀寫B(tài)RAM等),為了區(qū)別,有時候也叫這個為 AXI4-Full;

AXI4-Lite:用于簡單、低吞吐量的內(nèi)存映射通信(例如,與控制寄存器和狀態(tài)寄存器之間的通信);

AXI4-Stream :高速流數(shù)據(jù)(視頻、圖像等流式數(shù)據(jù));

AXI4 、AXI4-Lite和AXI4-Stream均使用Ready、Valid握手機制進行通信 。

**信息傳輸?shù)陌l(fā)起者使用****Valid ** 信號指示數(shù)據(jù)何時有效,接收端產(chǎn)生 Ready 信號來表明已經(jīng)準(zhǔn)備好接收數(shù)據(jù) , 當(dāng)兩者均為高時,啟動傳輸 。

** AXI4 總線和 AXI4-Lite 總線都有 5 個通道(** **AXI4-Stream ** 取消了通道) ,**AXI4 和 AXI4-Lite **通道的相同部分:

(1) 寫地址通道(AW) ,包含AWVALID,AWADDR,AWREADY信號;

(2) 寫數(shù)據(jù)通道 (W)**** ,包含WVALID,WDATA,WSTRB,WREADY信號;

(3) 寫應(yīng)答通道 (B)**** ,包含BVALID,BRESP,BREADY信號;

(4) 讀地址通道 (AR)**** ,包含ARVALID,ARADDR,ARREADY信號;

(5) 讀數(shù)據(jù)通道 (R)**** ,包含RVALID,RDATA,RREADY,RRESP信號;

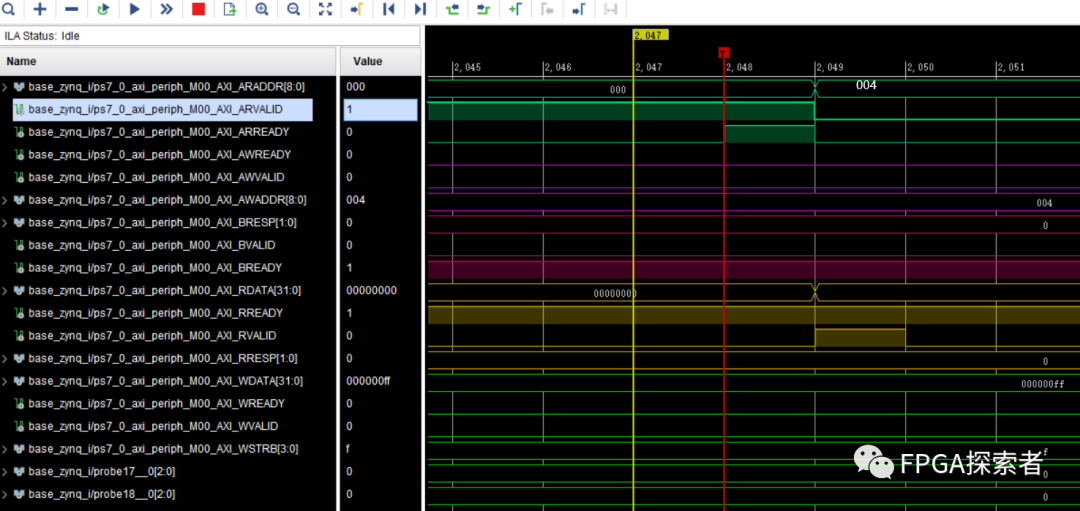

以 AXI-Lite 總線為例 ,Xilinx ZYNQ 通過 AXI4-Lite 總線控制 8 個 GPIO 的輸出,先寫入 0x0F 測試寫入操作,再寫入 0xFF 后讀取寫入的值,測試讀操作。

本操作是 ZYNQ 作為主機 Master,AXI-Lite GPIO 作為從機 Slave, 使用 ** Xilinx ****的 ****AXI Interconnect ** 總線互聯(lián)結(jié)構(gòu)互聯(lián) 。

**AXI4-Lite **是 AXI4 的刪減版,適合輕量級的應(yīng)用,也是包含 5 個通道,不同的是每個通道都進行了簡化, 去掉了對突發(fā)傳輸?shù)闹С郑˙urst) 。

寫事務(wù)握手實例

使用寫地址通道、寫數(shù)據(jù)通道和寫響應(yīng)通道 。

(1) 在寫數(shù)據(jù)通道上 ,主機給出要寫的數(shù)據(jù) 0x0F,并在一個時鐘周期后將數(shù)據(jù)有效信號 WVALID 拉高,等待從機的 WREADY 寫準(zhǔn)備好信號拉高;

(2) 在寫地址通道上 ,主機給出寫地址 0x00(GPIO 通道 1 的輸出數(shù)據(jù)的控制寄存器),并將地址有效信號 AWVALID 拉高,等待從機的 AWREADY 寫準(zhǔn)備好信號拉高;

(3)當(dāng) WVALID 和 WREADY 信號同時拉高后,數(shù)據(jù)成功寫入 GPIO 從機;當(dāng) AWVALID 和 AWREADY 信號同時拉高后,地址成功寫入 GPIO 從機;

(4)一個時鐘周期后, 在寫響應(yīng)通道上 ,給出響應(yīng)(BRESP 為 0),從機告訴主機已經(jīng)成功寫入;

此外,對于寫響應(yīng)信道,BREADY 由主機主動給出,一直保持在準(zhǔn)備好接收響應(yīng)的狀態(tài),當(dāng)從機發(fā)來一個 BVALID 信號指示一個有效的響應(yīng)后,BREADY 拉低一段時間后處理該響應(yīng)信息,處理完成后又恢復(fù)到準(zhǔn)備好接收響應(yīng)狀態(tài)。

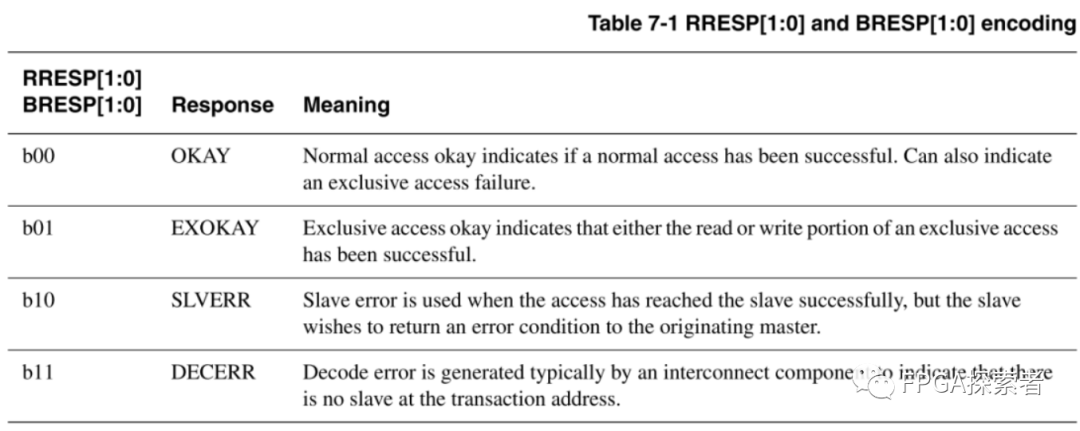

RRESP/BRESP 讀/寫響應(yīng)信號的含義,2-bit 信號,分別代表讀寫成功、獨占式讀寫、從設(shè)備錯誤、譯碼錯誤。

讀事務(wù)握手實例

**先向地址 ****0x00 ** 寫入數(shù)據(jù) 0xFF,再讀出,使用讀地址通道、讀數(shù)據(jù)通道 。

(1) 在讀地址通道上 ,主機給出要讀取的地址 0x00(GPIO 通道1 的輸出數(shù)據(jù)的控制寄存器),并將地址有效信號 AWVALID 拉高,等待從機的 AWREADY 寫準(zhǔn)備好信號拉高后,成功將要讀取的地址寫入從機;

(2) 在讀數(shù)據(jù)通道上 ,從機給出讀出的數(shù)據(jù) 0xFF,并將數(shù)據(jù)有效信號 WVALID 拉高,此階段主機的 WREADY 寫準(zhǔn)備好信號一直拉高,數(shù)據(jù)在兩個信號同時為高時傳輸,將 0xFF 寫入主機,此時讀響應(yīng) RRESP[1:0] 為 0,代表寫入成功;

(3)當(dāng) ARVALID 和 ARREADY 信號同時拉高后,地址成功寫入 GPIO 從機;

當(dāng) RVALID 和 RREADY 信號同時拉高后,數(shù)據(jù)成功返回給 ZYNQ 主機;

AXI4 總線握手機制

AXI4 、AXI4-Lite和AXI4-Stream均使用Ready、Valid握手機制進行通信 。

**信息傳輸?shù)陌l(fā)起者使用****Valid ** 信號指示數(shù)據(jù)何時有效,接收端產(chǎn)生 Ready 信號來表明已經(jīng)準(zhǔn)備好接收數(shù)據(jù) , 當(dāng)兩者均為高時,啟動傳輸 。

上面的實例給出了兩種 Valid 和 Ready 出現(xiàn)的情況,一種是 Valid 先為高,另一種是 Ready 先為高,實際上,Valid 和 Ready 一共有三種可能情況:

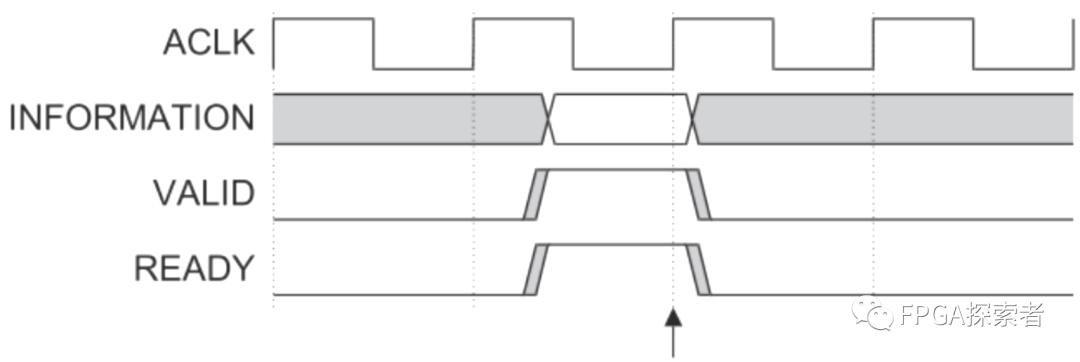

(1)Valid 先為高 Ready 后為高

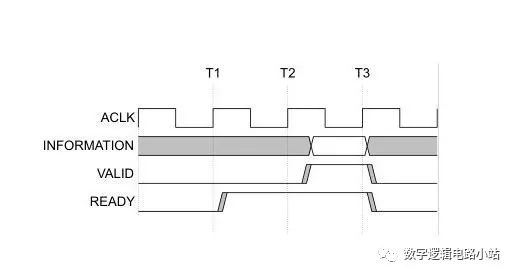

如前文實例中寫地址和寫數(shù)據(jù)通道所示,時序圖如下,傳輸發(fā)生在箭頭所指處(在時鐘 ACLK 的上升沿檢測到同時為高):

Master 主機發(fā)送端首先發(fā)出數(shù)據(jù)或者控制信息,并將自己的 Valid 有效信號拉高,指示信息(information)有效;

發(fā)送端的信息(information)和 Valid 信號保持穩(wěn)定,直到 Slave 從機接收端的 Ready 信號拉高,指示接收端已經(jīng)接收到 information。

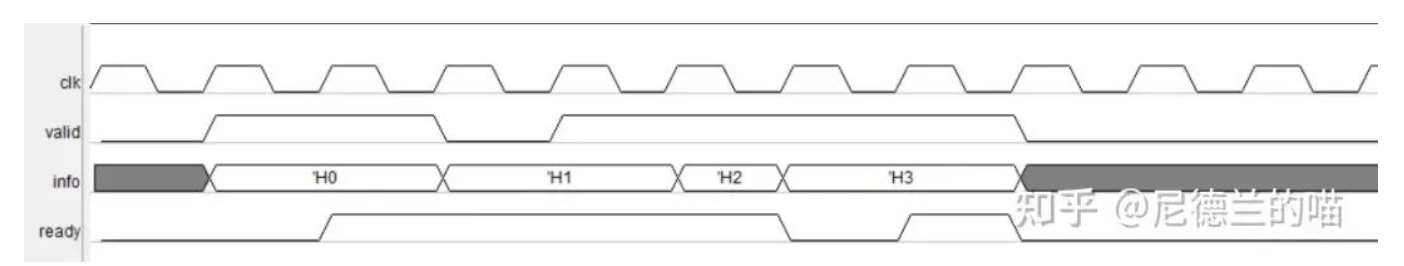

(2)Ready 先為高 Valid 后為高

如寫響應(yīng)通道所示,時序圖如下,傳輸發(fā)生在箭頭所指處(在時鐘 ACLK 的上升沿檢測到同時為高):

Slave 從機接收端首先表明自己準(zhǔn)備好接收數(shù)據(jù)或者控制信息,將自己的 Ready 準(zhǔn)備好信號拉高;

Master 發(fā)送端的信息(information)一旦有效,傳輸立刻開始。

(3)Ready 和 Valid 同時為高

時序圖如下,傳輸發(fā)生在箭頭所指處(在時鐘 ACLK 的上升沿檢測到同時為高):

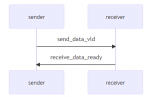

AXI4 總線通道依賴

(1)讀事務(wù)(讀地址通道、讀數(shù)據(jù)通道)

? 主機先發(fā)送 ARADDR 和 ARVALID 給從機;

? 從機回發(fā) ARREADY,通知主機該地址有效;

? 當(dāng) ARVALID 和 ARREADY 均為高電平時,主設(shè)備拉高 RREADY,表示主設(shè)備準(zhǔn)備好接收讀數(shù)據(jù)和讀響應(yīng)信號;

? 從設(shè)備發(fā)送 RVALID、RDATA 以及 RRESP,當(dāng) RVALID 和 RREADY 均為高電平時,數(shù)據(jù)成功寫入主設(shè)備。

圖中的單箭頭表示:箭頭兩端的信號沒有依賴關(guān)系,誰先拉高都行;

圖中的雙箭頭表示:箭頭起始信號拉高之后,箭頭指向的信號才可以拉高。

下圖可以看出,讀地址的 Valid 和 Ready 兩者誰先拉高都可以,讀數(shù)據(jù)的 Valid 和 Ready 兩者誰先拉高也沒關(guān)系,但是讀數(shù)據(jù)必須在讀地址完成后才可以拉高。

(2)寫事務(wù)(寫地址通道、寫數(shù)據(jù)通道、寫響應(yīng)通道)

在寫操作過程中,主機向從從機發(fā)生AWADDR、AWVALID、WVALID和WDATA,當(dāng) WVALID 和 WREADY 都為高電平時數(shù)據(jù)寫入從機。

**主設(shè)備發(fā)送的 AWVALID ** 和 WVALID 要有重疊區(qū) 。

-

FPGA設(shè)計

+關(guān)注

關(guān)注

9文章

428瀏覽量

27157 -

接收機

+關(guān)注

關(guān)注

8文章

1218瀏覽量

54238 -

BRAM

+關(guān)注

關(guān)注

0文章

41瀏覽量

11238 -

狀態(tài)寄存器

+關(guān)注

關(guān)注

0文章

39瀏覽量

7278 -

AXI4總線

+關(guān)注

關(guān)注

0文章

9瀏覽量

1466

發(fā)布評論請先 登錄

【芯片設(shè)計】握手協(xié)議的介紹與時序說明

ZYNQ & AXI總線 & PS與PL內(nèi)部通信(用戶自定義IP)

有沒有一種標(biāo)準(zhǔn)的方式到達(dá)PL AXI-Lite總線?

AXI總線的相關(guān)資料下載

AXI接口協(xié)議詳解

什么是握手信號? 什么是握手協(xié)議?

深入AXI4總線一握手機制

AXI總線學(xué)習(xí)(AXI3&4)

AXI3與AXI4寫響應(yīng)的依賴區(qū)別?

在握手協(xié)議中的Valid及data打拍技巧

簡述TCP協(xié)議的三次握手機制

TCP三次握手安全性分析

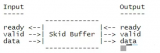

AXI握手時序優(yōu)化—pipeline緩沖器

握手機制、通道依賴性及AXI-Lite握手實例

握手機制、通道依賴性及AXI-Lite握手實例

評論