圖案化工藝包括曝光(Exposure)、顯影(Develope)、刻蝕(Etching)和離子注入等流程。其中,刻蝕工藝是光刻(Photo)工藝的下一步,用于去除光刻膠(Photo Resist,PR)未覆蓋的底部區(qū)域,僅留下所需的圖案。這一工藝流程旨在將掩模(Mask)圖案固定到涂有光刻膠的晶圓上(曝光→顯影)并將光刻膠圖案轉印回光刻膠下方膜層。隨著電路的關鍵尺寸(Critical Dimension, CD)小型化(2D視角),刻蝕工藝從濕法刻蝕轉為干法刻蝕,因此所需的設備和工藝更加復雜。由于積極采用3D單元堆疊方法,刻蝕工藝的核心性能指數(shù)出現(xiàn)波動,從而刻蝕工藝與光刻工藝成為半導體制造的重要工藝流程之一。

1.沉積和刻蝕技術的發(fā)展趨勢

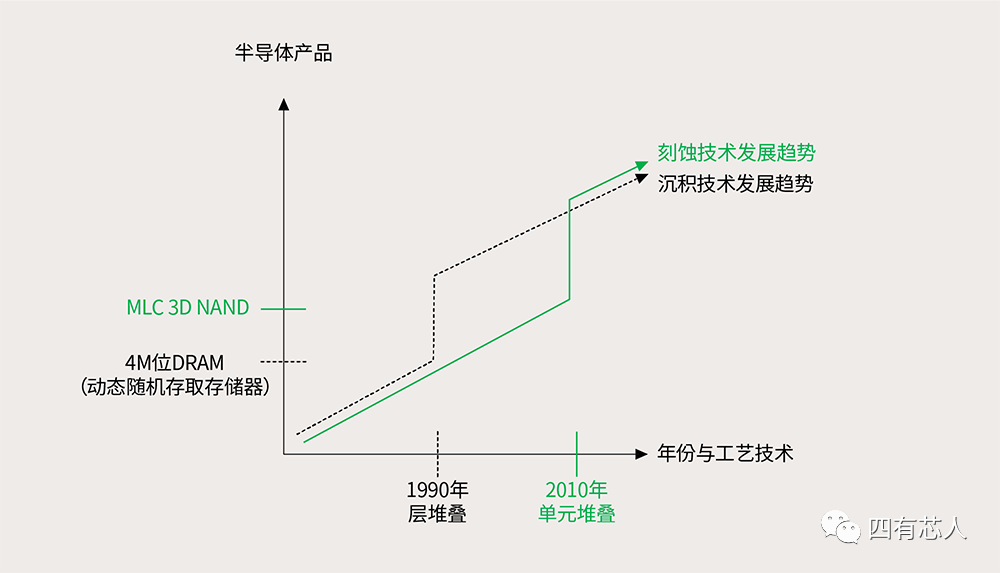

圖1. 沉積和刻蝕技術發(fā)展趨勢

在晶圓上形成“層(Layer)”的過程稱為沉積(化學氣相沉積(CVD)、原子層沉積(ALD)和物理氣相沉積(PVD)),在所形成的“層“上繪制電路圖案的過程稱為曝光。刻蝕是沉積和曝光工藝之后在晶圓上根據(jù)圖案刻化的過程。光刻工藝的作用類似于畫一張草圖,真正使晶圓發(fā)生明顯變化的是沉積和刻蝕工藝。

自從半導體出現(xiàn)以來,刻蝕和沉積技術都有了顯著發(fā)展。而沉積技術最引人注目的創(chuàng)新是從溝槽法(Trench)轉向堆疊法(Stack),這與20世紀90年代初裝置容量從1兆位(Mb)DRAM發(fā)展成4兆位(Mb)DRAM相契合。刻蝕技術的一個關鍵節(jié)點是在2010年代初,當時3D NAND閃存單元堆疊層數(shù)超過了24層。隨著堆疊層數(shù)增加到128層、256層和512層,刻蝕工藝已成為技術難度最大的工藝之一。

2.刻蝕方法的變化

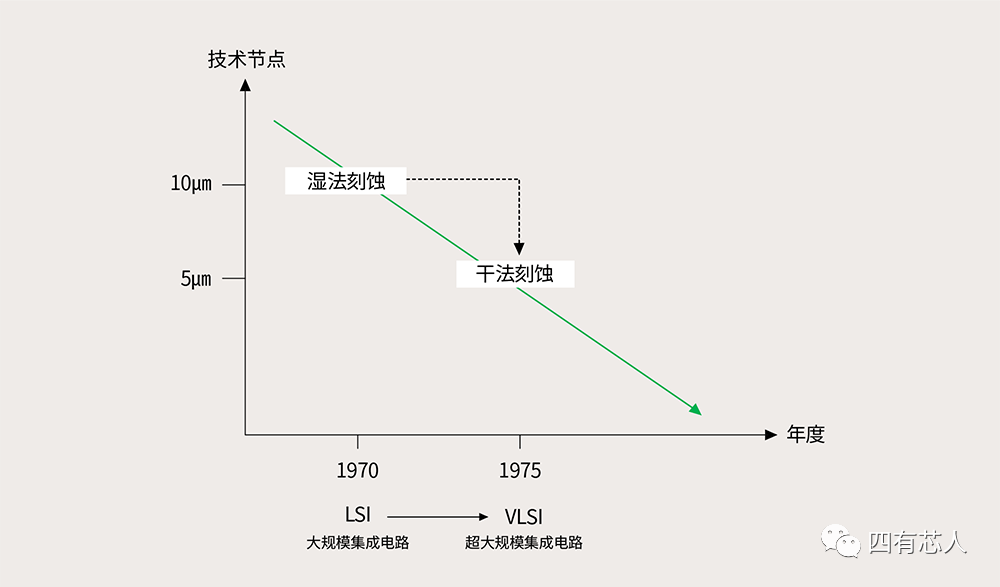

圖2. 小型化(2D)與刻蝕方法的發(fā)展

在2D(平面結構)半導體小型化和3D(空間結構)半導體堆疊技術的發(fā)展過程中,刻蝕工藝也在不斷發(fā)展變化。在20世紀70年代,2D半導體為主流,電路關鍵尺寸(CD)從100微米(?)迅速下降到10微米(?),甚至更低。在此期間,半導體制造流程中的大部分重點工藝技術已經(jīng)成熟,同時刻蝕技術已經(jīng)從濕法刻蝕過渡到干法刻蝕。對于層切割技術,最先采用的是化學濕法,這是一種相對簡單的技術。由于從20世紀70年代早期開始,化學濕法難以滿足5微米(?)關鍵尺寸的要求,從而開發(fā)出利用等離子體的干法。發(fā)展到今天,刻蝕工藝大多采用干法,而濕法刻蝕技術后來發(fā)展應用于清潔過程。

3.濕法刻蝕和干法刻蝕的優(yōu)缺點

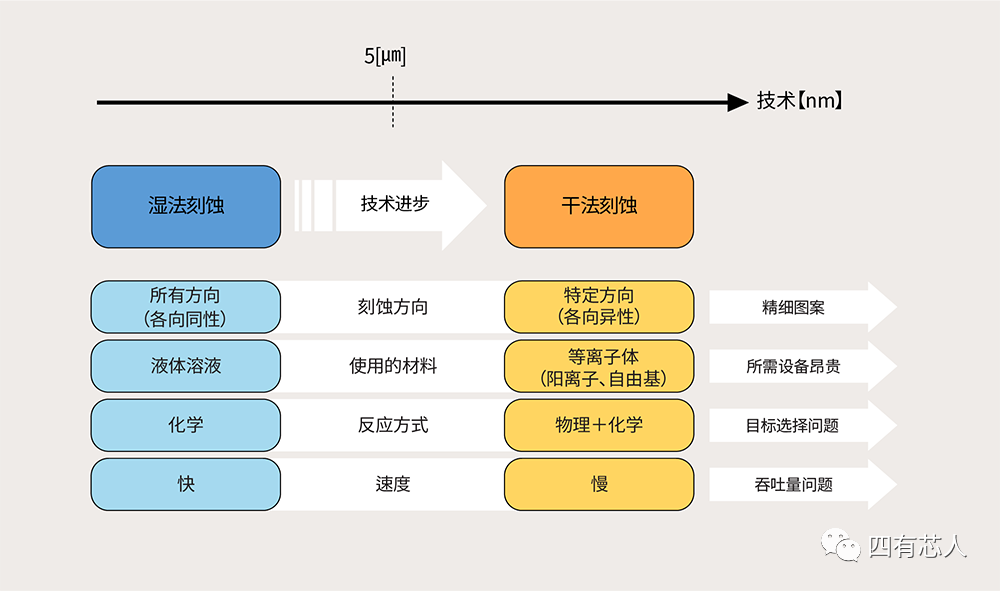

圖3. 濕法刻蝕和干法刻蝕的優(yōu)缺點

濕法刻蝕因為使用液體速度更快,每分鐘去除的深度更大,但不會形成類似于直方的結構。濕法刻蝕會均勻地刻蝕所有方向,從而導致橫向方向上的損耗,而對于CD小型化應該避免這種現(xiàn)象。相反,干法刻蝕可以在某一特定方向上進行切割,使得實現(xiàn)理想中納米(nm)級的超精細圖案輪廓。

此外,濕法刻蝕會產(chǎn)生環(huán)境污染,因為使用過的液體溶液需在此工藝完成后進行丟棄處理。相比之下,采用干法刻蝕時,排放管線中會布置洗滌器,這能夠在向大氣中排放廢氣之前經(jīng)過中和過程,從而減少對環(huán)境的影響。

然而,由于晶圓上方數(shù)多層復雜地纏繞在一起,所以在采用干法刻蝕過程中很難瞄準某一特定的層(膜)。在針對某一特定層進行刻蝕時,采用濕法刻蝕會更容易進行,因為它采用化學反應進行刻蝕。而在進行選擇性刻蝕時使用干法并不容易,因為需要結合物理和化學技術。

4.刻蝕工藝流程及相關問題

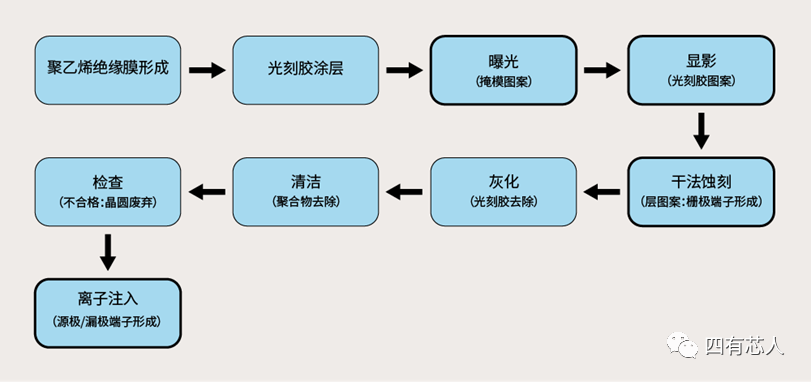

圖4. 刻蝕相關工藝流程

刻蝕工藝流程始于形成薄膜,在其上施加光刻膠,并進行曝光、顯影、刻蝕、灰化、清潔、檢查和離子注入等步驟,以形成三個TR端子,這是半導體制造的核心工藝。如果在顯影過程中不能順利切割光刻膠,則剩余的光刻膠會妨礙刻蝕。如果在刻蝕過程中未能對目標層進行充分刻蝕,則不能按計劃注入離子,因為雜質(zhì)會妨礙離子注入。如果干法刻蝕后未能徹底清除殘留的聚合物,也會產(chǎn)生同樣的后果。如果由于時間控制失敗,等離子體的離子氣體量太大或薄膜刻蝕過度,會對下層薄膜造成物理性損傷。

因此,在干刻蝕工藝中精準控制終點(EOP:End of Point)至關重要。徹底檢查刻蝕條件以及灰化和清潔過程也非常重要。如果晶圓刻蝕不均勻,則晶圓可能遭到退貨,而且刻蝕不足比過度刻蝕更為致命。

由于刻蝕工藝涉及的步驟非常復雜,我打算將其分為兩部分進行闡述。在這一部分中,我們闡述了刻蝕技術的歷史和發(fā)展方向。在下一部分中,我們將對等離子體和刻蝕之間的關系、RIE、刻蝕方法、縱橫比以及刻蝕速度進行詳細闡述。

-

半導體

+關注

關注

335文章

28713瀏覽量

234420 -

晶圓

+關注

關注

52文章

5131瀏覽量

129306 -

光刻

+關注

關注

8文章

344瀏覽量

30623 -

工藝流程

+關注

關注

7文章

112瀏覽量

16534 -

刻蝕

+關注

關注

2文章

203瀏覽量

13349

原文標題:半導體圖案化工藝流程之刻蝕(一)

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

簡述半導體超純水設備工藝流程及標準參考分析

【新加坡】知名半導體晶圓代工廠招聘資深刻蝕工藝工程師和刻蝕設備主管!

振奮!中微半導體國產(chǎn)5納米刻蝕機助力中國芯

半導體材料的工藝流程

泛林集團自維護設備創(chuàng)半導體行業(yè)工藝流程生產(chǎn)率新紀錄

功率半導體分立器件工藝流程

半導體前端工藝:刻蝕——有選擇性地刻蝕材料,以創(chuàng)建所需圖形

半導體圖案化工藝流程之刻蝕(一)

半導體圖案化工藝流程之刻蝕(一)

評論