該電路使用電子可編程電壓基準(zhǔn)(DS4305)作為單位非易失性存儲單元,可記住待機(jī)/ON開關(guān)的狀態(tài),該開關(guān)在沒有操作員在場的情況下改變狀態(tài)。

以下待機(jī)/ON開關(guān)適用于應(yīng)用(例如工業(yè)和電信),在這些應(yīng)用中,在沒有操作員在場時發(fā)生電源故障后,電路必須以某種方式“記住”其狀態(tài)(待機(jī)或ON)。基于電池(或超級電容器)和觸發(fā)器的替代方法不太可靠,因為如果漏電流耗盡電池,其狀態(tài)可能會丟失。另一種選擇涉及使用微控制器和EEPROM,但這需要軟件和啟動時間的規(guī)定。此外,用于此應(yīng)用的獨立EEPROM具有尷尬的接口。

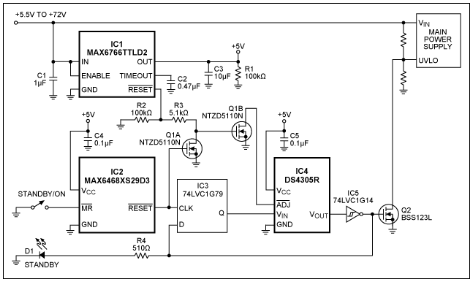

其思路(圖1)是使用電子可編程基準(zhǔn)電壓源(IC4、DS4305)作為單位非易失性存儲單元。為了記住待機(jī)/ON開關(guān)的狀態(tài),該電路對輸出電壓進(jìn)行高電平或低電平編程,并可對其進(jìn)行至少50,000次重新編程。

圖1.如果電源故障且沒有操作員在場,則此電路會記住其狀態(tài)(待機(jī)或打開)。

IC1 (MAX6766)為低壓差(LDO)線性穩(wěn)壓器,具有RESET輸出,寬輸入電壓范圍可擴(kuò)展至72V。μP監(jiān)控器(IC2,MAX6468)對控制按鈕(待機(jī)/開啟按鈕)進(jìn)行去抖動,并通過增加脈沖之間的暫停長度來支持IC4的編程。IC4輸出驅(qū)動具有施密特觸發(fā)器輸入(IC5)的逆變器,該逆變器反過來驅(qū)動晶體管Q2的柵極以控制主電源。

觸發(fā)器IC3有助于通過每次按下控制按鈕來改變待機(jī)/開啟狀態(tài)。在IC4編程周期結(jié)束時,由于來自逆變器的反饋,IC3的CLK輸入處的低至高邊沿將觸發(fā)器設(shè)置為相反的狀態(tài)。此操作也會在上電時由IC2 RESET觸發(fā),以確保開關(guān)已準(zhǔn)備好更改狀態(tài)。晶體管Q1B和IC1的RESET輸出通過在啟動和電源故障條件下阻止IC4的ADJ輸入來防止錯誤狀態(tài)的編程。

IC2的上電(或關(guān)斷)RESET脈沖對IC4的ADJ輸入的影響也必須被阻斷;因此,IC1的復(fù)位超時(由電容C2設(shè)置)比IC2的復(fù)位超時長。IC2(2.9V)的電壓閾值也低于IC1(4.6V)。IC5的最差情況“低”輸入門限(1.32V)保證了首次上電時的待機(jī)位置,因為IC4的出廠預(yù)設(shè)輸出僅為1.2V。

審核編輯:郭婷

-

微控制器

+關(guān)注

關(guān)注

48文章

7922瀏覽量

153799 -

電容器

+關(guān)注

關(guān)注

64文章

6569瀏覽量

101982 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2033瀏覽量

61919

發(fā)布評論請先 登錄

TPL1401數(shù)字電位器易失性和非易失性的區(qū)別是什么?

Cypress非易失性SRAM技術(shù)

非易失性MRAM的基礎(chǔ)知識匯總

非易失性MRAM基礎(chǔ)知識匯總

求助,如何使用非易失性密鑰生成CMAC?

非易失性內(nèi)存有寫入限制嗎?

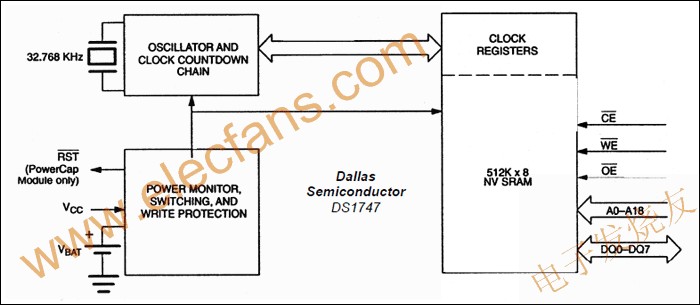

非易失性SRAM DS1747

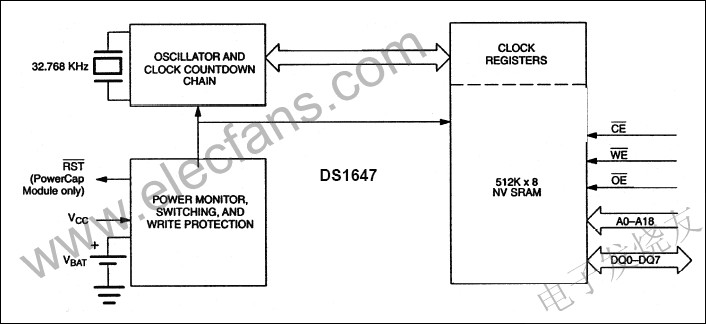

DS1647為512k x 8非易失性靜態(tài)RAM

采用55納米非易失性內(nèi)存的Qorivva MCU

一文知道新興非易失性存儲(NVM)市場及技術(shù)趨勢

非易失性NVSRAM存儲器的詳細(xì)講解

簡單的非易失性門控

非易失性待機(jī)/接通開關(guān)

非易失性待機(jī)/接通開關(guān)

評論