· 基本硬件設(shè)計(jì)模式 ·

讀者如果學(xué)習(xí)了verilog,并且有了一定的實(shí)踐經(jīng)驗(yàn)的話應(yīng)該強(qiáng)烈的感受到,verilog和軟件(諸如C/C++)有著本質(zhì)且明顯的差別,是一條不可跨越的鴻溝。所以初學(xué)者把C和verilog拿來(lái)作比較是完全沒(méi)用的,甚至?xí)殉鯇W(xué)者繞暈,影響學(xué)習(xí)效率的提高。

雖然verilog比硬件更抽象,但是最終實(shí)現(xiàn)的結(jié)果就是一堆硬件電路。所以評(píng)價(jià)一個(gè)verilog代碼的好壞不是看代碼量多少,而是看最終實(shí)現(xiàn)的功能和性能(有速度和面積2方面)。假設(shè)面積為S,性能為V,定義品質(zhì)數(shù)Q=S/V,Q越小,設(shè)計(jì)的電路越成功。

評(píng)價(jià)一個(gè)設(shè)計(jì)者代碼水平較高,只是這個(gè)設(shè)計(jì)由硬件向verilog表現(xiàn)形式轉(zhuǎn)換更流暢,合理。一個(gè)設(shè)計(jì)最終實(shí)現(xiàn)的性能,很大程度上取決于設(shè)計(jì)的硬件方案是否高效合理。這是兩回事。

也因上述2點(diǎn),verilog設(shè)計(jì)不刻意追求代碼簡(jiǎn)潔,合理的設(shè)計(jì)方法是首先理解要設(shè)計(jì)的電路,也就是把需求轉(zhuǎn)化為數(shù)字電路,對(duì)此電路的結(jié)構(gòu)和連接十分清晰,然后再用verilog表達(dá)出這段電路。也就是說(shuō),verilog只是簡(jiǎn)化了電路設(shè)計(jì)的工作量,本質(zhì)上就是設(shè)計(jì)數(shù)字電路,永遠(yuǎn)繞不開電路這點(diǎn)!這也決定了不能憑空去想代碼,因?yàn)橹挥写嬖诘碾娐凡攀强蓪?shí)現(xiàn)的,而存在的代碼未必可以變成存在的電路。

大家也應(yīng)該知道,在沒(méi)有verilog這種高級(jí)語(yǔ)言之前都是用原理圖設(shè)計(jì),必須先構(gòu)思好整個(gè)電路框架,才能去實(shí)現(xiàn)。有了verilog以后這種思路并沒(méi)有被拋棄,依然需要大家去思考電路結(jié)構(gòu),只有深入理解了電路本身,才能夠有高效的設(shè)計(jì)。

· 實(shí)例說(shuō)明 ·

世界上沒(méi)有工作2次就自動(dòng)停下的觸發(fā)器,所以下面的電路綜合是無(wú)法實(shí)現(xiàn)的。

repeat(2)@(posedge clk)

d <=x;

雖然上述語(yǔ)法很正確,沒(méi)有毛病,但是是不現(xiàn)實(shí)的,現(xiàn)在的技術(shù)或者提供的語(yǔ)言還沒(méi)有抽象到符合語(yǔ)法的都能直接綜合成電路,他比較生硬,沒(méi)有大家想的那么靈活。

至此可以得出一個(gè)基本結(jié)論,面向硬件的設(shè)計(jì)模式,就是要從電路特征和行為來(lái)編寫代碼。

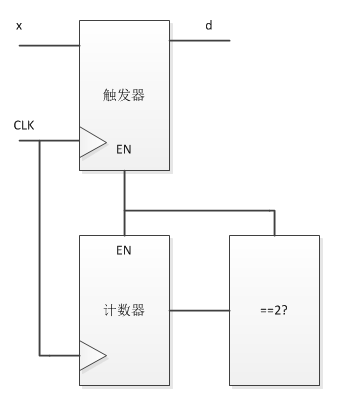

例如上面的電路,要實(shí)現(xiàn)觸發(fā)器只工作2次就停止怎么辦呢?這個(gè)電路是存在的,只是不存在工作2次就自動(dòng)停下的觸發(fā)器,所以控制觸發(fā)器運(yùn)行2次后關(guān)閉使能就可以了。按照這個(gè)思路,原理圖如下:

上圖觸發(fā)器輸入數(shù)據(jù)x,輸出數(shù)據(jù)d,觸發(fā)器和計(jì)數(shù)器使能端由比較器控制,計(jì)數(shù)到2的時(shí)候,計(jì)數(shù)器和觸發(fā)器都不使能,這樣觸發(fā)器就只工作了2次。也可以認(rèn)為是一個(gè)簡(jiǎn)單的狀態(tài)機(jī),計(jì)數(shù)器就是狀態(tài)控制。具體代碼請(qǐng)讀者思考,首先用上圖思路,再用三段式狀態(tài)機(jī)思路,建議二者都寫出來(lái),好好比較綜合后的RTL圖,并且仿真確保結(jié)果正確。

-

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2287瀏覽量

96091 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2033瀏覽量

61930 -

狀態(tài)機(jī)

+關(guān)注

關(guān)注

2文章

493瀏覽量

28095 -

C++語(yǔ)言

+關(guān)注

關(guān)注

0文章

147瀏覽量

7239 -

Verilog語(yǔ)言

+關(guān)注

關(guān)注

0文章

113瀏覽量

8502

發(fā)布評(píng)論請(qǐng)先 登錄

Verilog硬件描述語(yǔ)言描述.

VERILOG HDL硬件描述語(yǔ)言

Verilog HDL硬件描述語(yǔ)言【書籍

Verilog HDL語(yǔ)言簡(jiǎn)介

Verilog硬件描述語(yǔ)言參考手冊(cè)

Verilog HDL硬件描述語(yǔ)言_Verilog語(yǔ)言要素

基于Verilog硬件描述語(yǔ)言的IEEE標(biāo)準(zhǔn)硬件描述語(yǔ)言資料合集免費(fèi)下載

Verilog硬件描述語(yǔ)言的學(xué)習(xí)課件免費(fèi)下載

Verilog硬件描述語(yǔ)言參考手冊(cè)免費(fèi)下載

verilog語(yǔ)言面向硬件設(shè)計(jì)的思維

verilog語(yǔ)言面向硬件設(shè)計(jì)的思維

評(píng)論